# PDP-9 PDP-9/L INTERFACE MANUAL

November 1968

Copyright © 1968 by Digital Equipment Corporation

The following are registered trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC FLIP CHIP DIGITAL

PDP FOCAL

COMPUTER LAB

# CONTENTS

|       |                                                          | Page |

|-------|----------------------------------------------------------|------|

|       | CHAPTER 1<br>INTRODUCTION TO DEC LOGIC                   |      |

|       | CHAPTER 2 THE PDP-9 and PDP-9/L COMPUTER SYSTEMS         |      |

| 2.1   | PDP-9                                                    | 2-1  |

| 2.2   | PDP-9/L                                                  | 2-1  |

| 2.3   | Computer Subsystems                                      | 2-1  |

| 2.3.1 | Central Processor Unit                                   | 2-1  |

| 2.3.2 | Core Memory                                              | 2-2  |

| 2.3.3 | Input/Output Facilities                                  | 2-5  |

|       | CHAPTER 3 INTERFACING TO THE PDP-9 and PDP-9/L COMPUTERS |      |

| 3.1   | Program Controlled Transfers                             | 3-2  |

| 3.1.1 | Signal Summary                                           | 3-2  |

| 3.1.2 | Peripheral Interface Requirements                        | 3-2  |

| 3.1.3 | I/O Bus Transfer                                         | 3-2  |

| 3.1.4 | Other I/O Bus Facilities Used in AC Transfers            | 3-4  |

| 3.2   | General Use of IOP Pulses and Device Select Codes        | 3-6  |

| 3.2.1 | Timing Charts                                            | 3-7  |

| 3.3   | Program Controlled Transfers Using The API Option        | 3-7  |

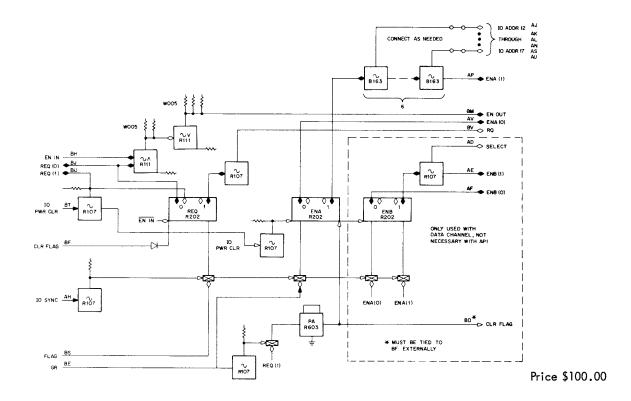

| 3.3.1 | API Interface Logic                                      | 3-8  |

| 3.4   | Data Channel Transfers                                   | 3-15 |

| 3.4.1 | Latency                                                  | 3-16 |

| 3.4.2 | Data Channel Interface Logic                             | 3-16 |

| 3.4.3 | Data Transfers To and From the Computer                  | 3-17 |

| 3.4.4 | Expanding the DCH to Eight Devices                       | 3-18 |

| 3.4.5 | Interface Design                                         | 3-18 |

| 3.4.6 | Other DCH Features                                       | 3-22 |

| 3.4.7 | Standard Core Register Assignment for DCH                | 3-23 |

|       | CHAPTER 4 DIRECT MEMORY ACCESS CHANNEL OF THE PDP-9      |      |

| 4.1   | DMA Interface Signals                                    | 4-1  |

| 4.2   | DM09A Operation                                          | 4-3  |

# CONTENTS (Cont)

|       |                                                               | Page |  |  |

|-------|---------------------------------------------------------------|------|--|--|

| 4.2.1 | Interfacing To The DM09A                                      |      |  |  |

| 4.2.2 | DM09A Master Drawing List                                     |      |  |  |

| 4.2.3 | Summary of Data Transfer Rates and Latency Times              | 4-7  |  |  |

|       | CHAPTER 5 GENERAL WIRING RULES AND SUGGESTIONS                |      |  |  |

| 5.1   | Typical Wiring                                                | 5-1  |  |  |

| 5.2   | Ground System                                                 |      |  |  |

| 5.3   | Signal Wiring Rules                                           | 5-2  |  |  |

| 5.3.1 | Control Area Pulses                                           | 5-2  |  |  |

| 5.3.2 | Register Loading Pulses                                       | 5-2  |  |  |

| 5.3.3 | Waveform Requirements                                         | 5-2  |  |  |

| 5.4   | Level Wiring Rules For B-, R-, and S-Series Levels and Pulses | 5-4  |  |  |

|       | CHAPTER 6 USER TERMINAL INTERFACES                            |      |  |  |

| 6.1   | Requirements                                                  | 6-1  |  |  |

| 6.2   | Teletype Interface                                            | 6-1  |  |  |

|       | CHAPTER 7<br>MARGIN CHECK BUS                                 |      |  |  |

|       | CHAPTER 8 THE PDP-9 and PDP-9/L GROUND MESH SPECIFICATIONS    |      |  |  |

|       | APPENDIX A<br>I/O BUS SUMMARY                                 |      |  |  |

| A.1   | Physical Characteristics                                      | A-1  |  |  |

| A.2   | Electrical Characteristics                                    | A-2  |  |  |

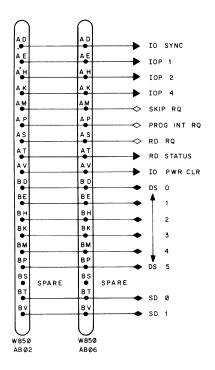

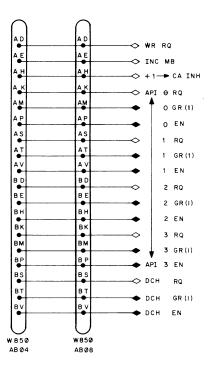

| A.3   | W850 Connector                                                | A-2  |  |  |

| A.4   | Loading Rules                                                 | A-2  |  |  |

| A.5   | General Rules                                                 | A-2  |  |  |

| A.6   | Interface Signals                                             | A-2  |  |  |

|       | APPENDIX B<br>PDP-9 MODULE INFORMATION                        |      |  |  |

| в.1   | Measurement Definitions                                       | B- 1 |  |  |

| B.2   | B-Series Module Interconnections                              | B-1  |  |  |

# APPENDICES (Cont)

|      |                                                                                        | <u>Page</u> |

|------|----------------------------------------------------------------------------------------|-------------|

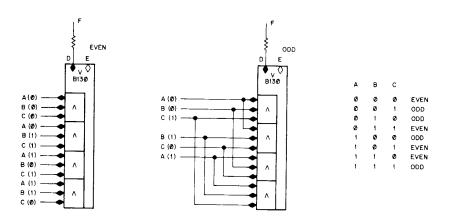

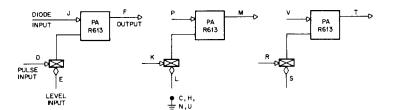

| B.3  | Modules For PDP-9 or PDP-9/L Interfacing                                               | B-3         |

|      | APPENDIX C DESIGN EXAMPLE FOR STANDARD INTERFACE FOR THE PDP-9 and PDP-9/L I/O DEVICES |             |

| C.1  | Implementing The Standard Interface                                                    | C-1         |

|      | ILLUSTRATIONS                                                                          |             |

| 1-1  | Digital Logic Signals                                                                  | 1-1         |

| 1-2  | Sources and Loads Shown Without Connections                                            | 1-2         |

| 1-3  | Wired AND                                                                              | 1-2         |

| 1-4  | Wired OR                                                                               | 1-2         |

| 1-5  | Flip-Flop Representation                                                               | 1-2         |

| 1-6  | DCD Gate                                                                               | 1-3         |

| 1-7  | Inverter (NOT Gate)                                                                    | 1-3         |

| 1-8  | AND Gate                                                                               | 1-3         |

| 1-9  | OR Gate                                                                                | 1-3         |

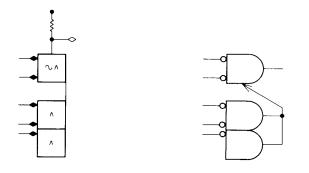

| 1-10 | Expanded Gate                                                                          | 1-4         |

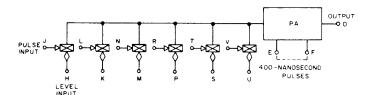

| 1-11 | Pulse Amplifier                                                                        | 1-4         |

| 1-12 | Monostable Multivibrator (Single Shot)                                                 | 1-4         |

| 1-13 | Monostable Multivibrator (Delay)                                                       | 1-4         |

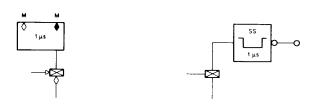

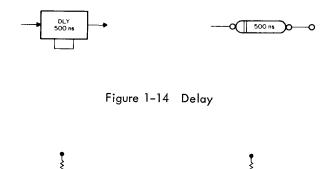

| 1-14 | Delay                                                                                  | 1-4         |

| 1-15 | Clamped Load                                                                           | 1-4         |

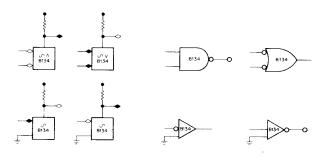

| 1-16 | Different Uses of a Particular Module                                                  | 1-4         |

| 1-17 | DCD Usage                                                                              | 1-5         |

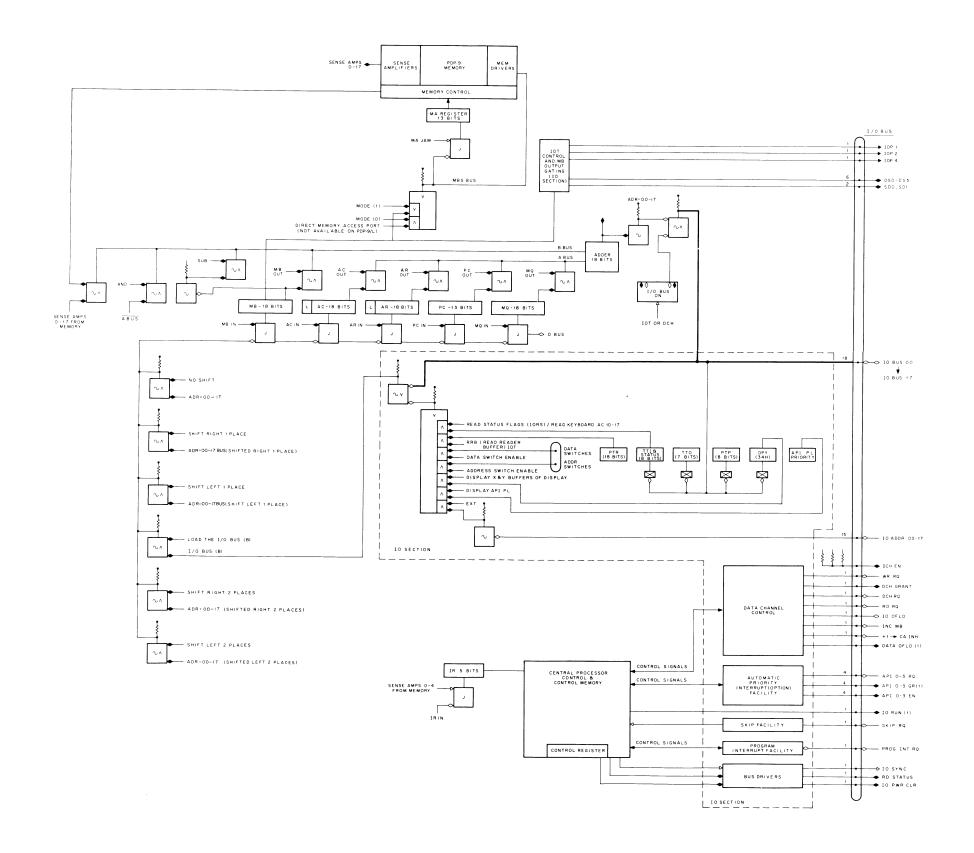

| 2-1  | CPU Control Elements and Registers                                                     | 2-3         |

| 2-2  | PDP-9 IOT Instruction Format                                                           | 2-6         |

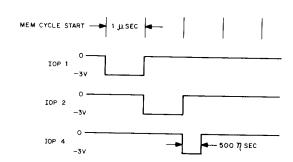

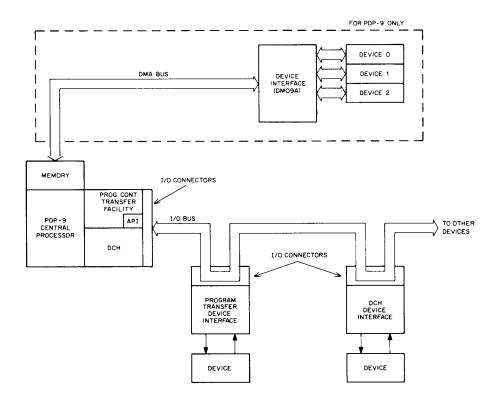

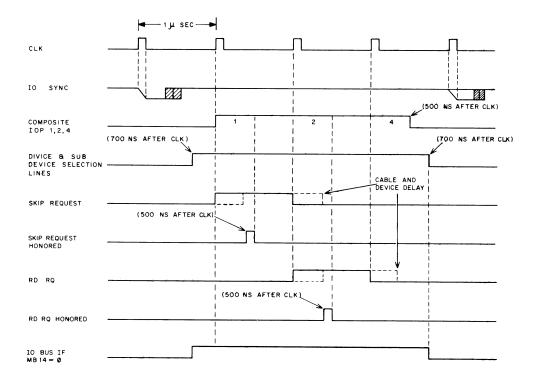

| 2-3  | IOP Timing Diagram for PDP-9                                                           | 2-6         |

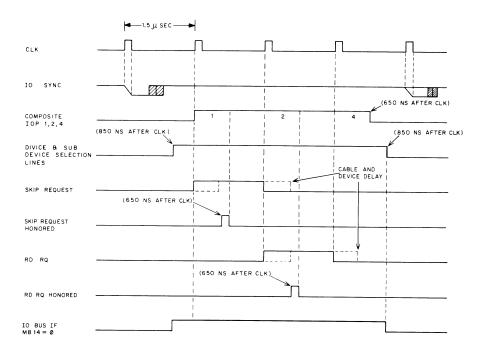

| 2-4  | IOP Timing Diagram for PDP-9/L                                                         | 2-6         |

| 2-5  | MB, DS or SD Signal Buffering                                                          | 2-7         |

| 2-6  | IOP Control Logic                                                                      | 2-9         |

| 2-7  | Typical Input Output Logic For Data on I/O Bus Lines 00 through 17                     | 2-11        |

| 2-8  | I/O PWR CLR Logic                                                                      | 2-11        |

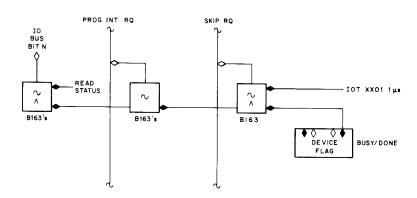

| 2-9  | RD Status Logic                                                                        | 2-11        |

# ILLUSTRATIONS (Cont)

|              |                                                                                                     | Page |

|--------------|-----------------------------------------------------------------------------------------------------|------|

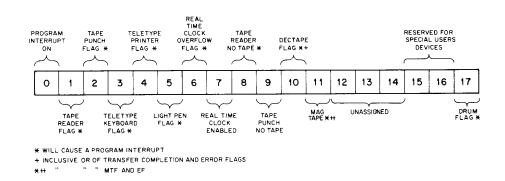

| 2-10         | Program Interrupt Storage Word Format                                                               | 2-11 |

| 2-11         | I/O PI Logic                                                                                        | 2-12 |

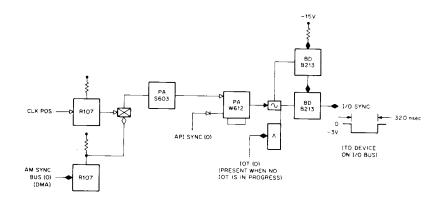

| 2-12         | I/O Sync Logic for the Computers                                                                    | 2-14 |

| 2-13         | DCH RQ Logic for PDP-9 and PDP-9/L                                                                  | 2-14 |

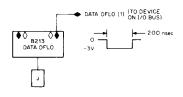

| 2-14         | IO OFLO Output Logic                                                                                | 2-15 |

| 2-15         | IO ADDR Input Logic to Computer                                                                     | 2-15 |

| 2-16         | DATA OFLO Logic                                                                                     | 2-15 |

| 2-1 <i>7</i> | +1 → CA INH and DCH EN Logic                                                                        | 2-15 |

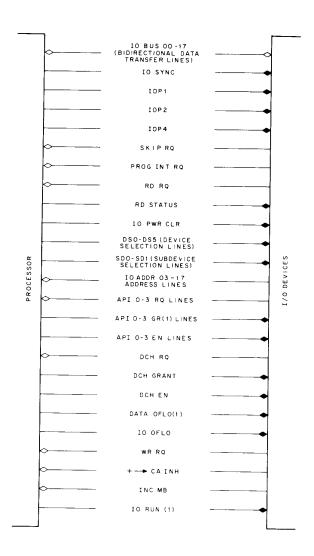

| 3-1          | Interfacing to the PDP-9 and PDP-9/L Computers                                                      | 3-1  |

| 3-2          | Reading and Writing on the PDP-9 and PDP-9/L I/O Buses                                              | 3-3  |

| 3-3          | Device Flag Hardware                                                                                | 3-4  |

| 3-4          | IORS Word-Status Bit Assignment                                                                     | 3-5  |

| 3-5          | PDP-9 Program Controlled Transfer Timing                                                            | 3-7  |

| 3-6          | PDP-9/L Program Controlled Transfer Timing                                                          | 3-8  |

| 3-7          | Equivalent Circuit of the W104 Module                                                               | 3-9  |

| 3-8          | Using the API Facility of the PDP-9                                                                 | 3-9  |

| 3-9          | Interfacing a Single Flag Device to the API                                                         | 3-11 |

| 3-10         | Multiple Flags Device Using Both API and PI Facilities                                              | 3-13 |

| 3-11         | Multiple Devices on the Automatic Priority Interrupt System                                         | 3-15 |

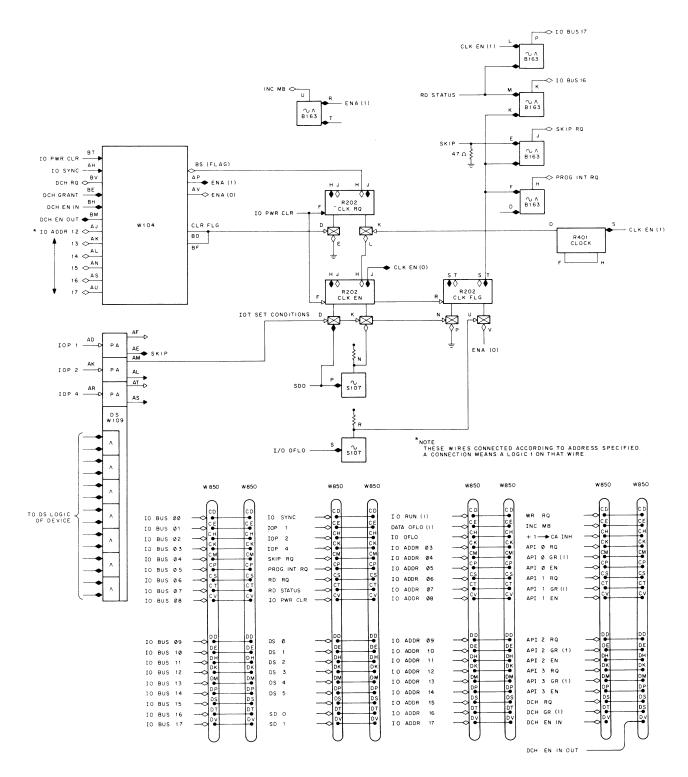

| 3-12         | DCH Interface Logic for Reading and Writing                                                         | 3-19 |

| 3-13         | DCH Clock Using Memory Increment                                                                    | 3-21 |

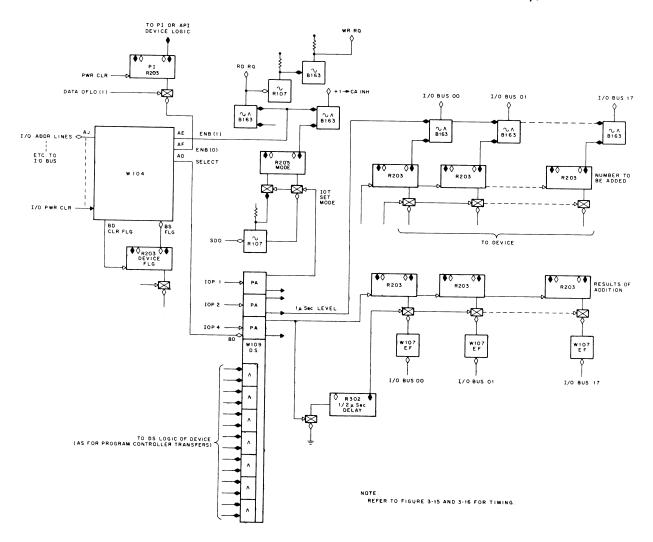

| 3-14         | DCH Add-to-Memory Circuit with +1 → CA INH Mode                                                     | 3-22 |

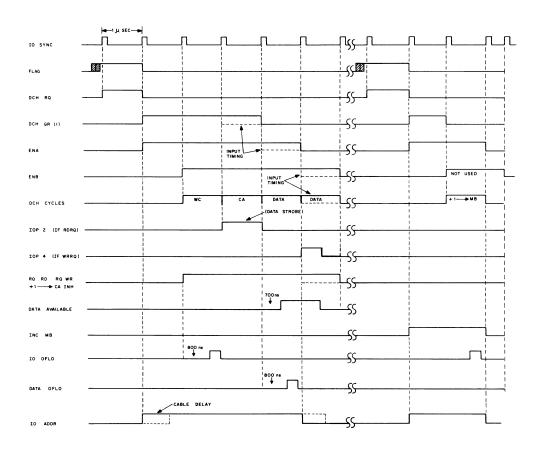

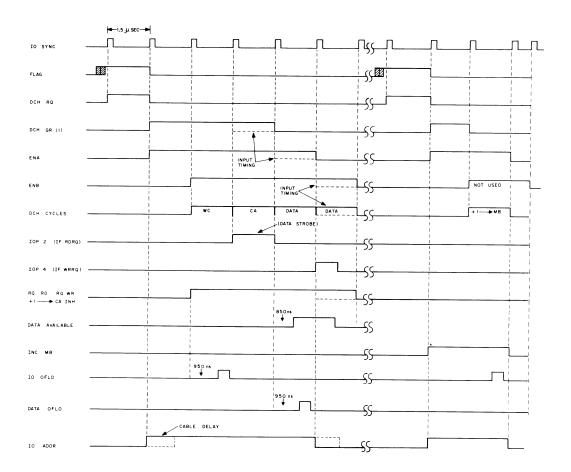

| 3-15         | DCH IO Timing in the PDP-9                                                                          | 3-23 |

| 3-16         | DCH IO Timing in the PDP-9/L                                                                        | 3-24 |

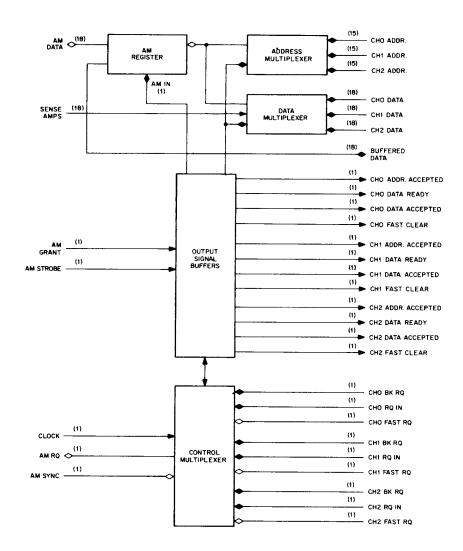

| 4-1          | DM09A Option Block Diagram                                                                          | 4-2  |

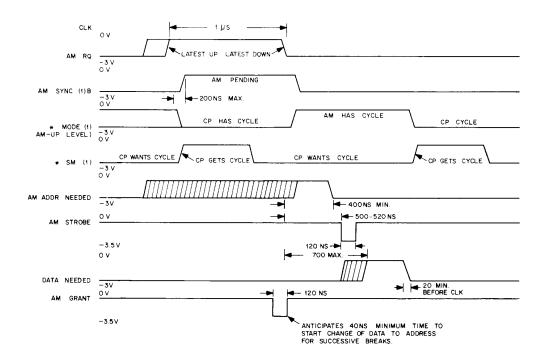

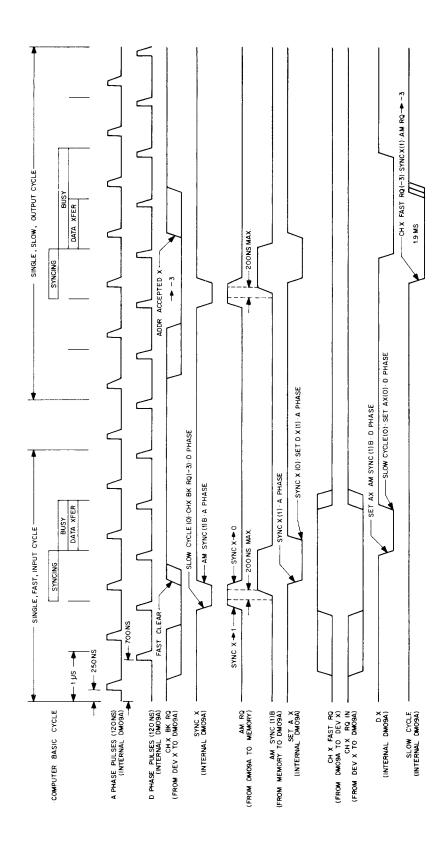

| 4-2          | DMA Synchronization Cycle, Timing Diagram                                                           | 4-4  |

| 4-3          | DM09 Data Cycle Timing Diagram                                                                      | 4-5  |

| 5-1          | Logic Ground Mesh                                                                                   | 5-1  |

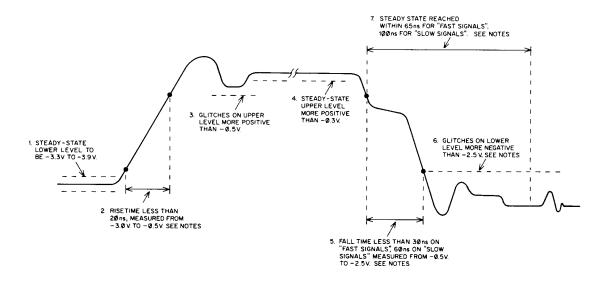

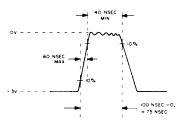

| 5-2          | Waveform Requirements for B Series                                                                  | 5-2  |

| 5-3          | Waveform Requirements for B Series Modules                                                          | 5-3  |

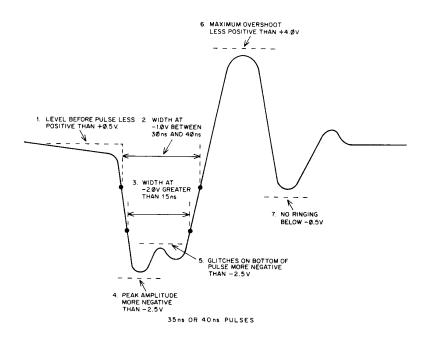

| 5-4          | Standard R Series FLIP CHIP Waveform                                                                | 5-3  |

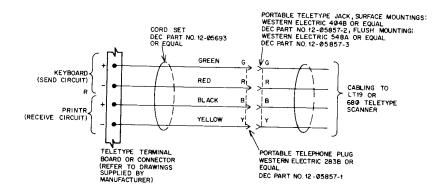

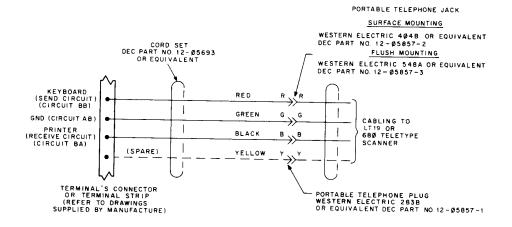

| 5 <b>-</b> 1 | 20 mA, Full Duplex Terminals                                                                        | 6-2  |

| <b>5-</b> 2  | Connections for EIA Interface (EIA Standard RS-232-B) (Model 37 Teletypes and many other terminals) | 6-2  |

# ILLUSTRATIONS (Cont)

|              |                                                | Page |

|--------------|------------------------------------------------|------|

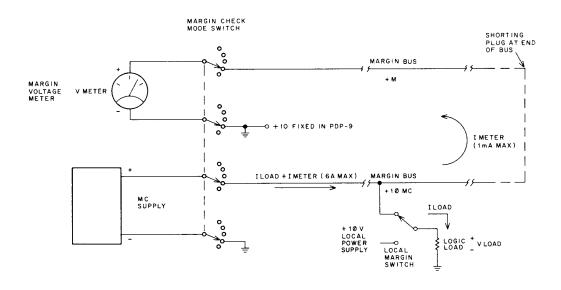

| 7-1          | Margin Bus Voltage Drops                       | 7-1  |

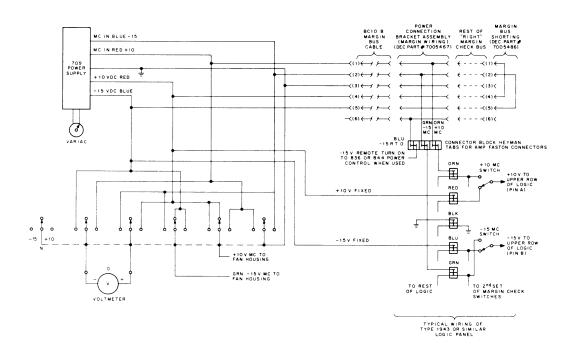

| 7-2          | Margin Bus Circuit                             | 7-2  |

| 8-1          | Typical Ground Mesh System                     | 8-1  |

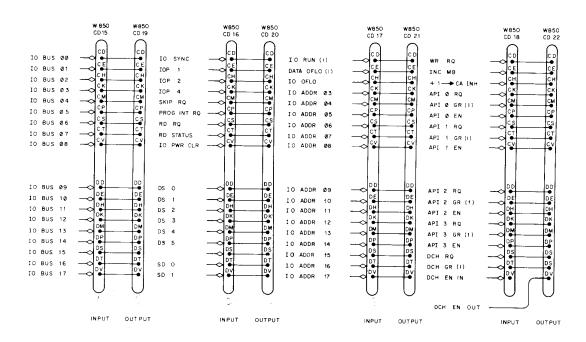

| A-1          | IO Bus Connections                             | A-1  |

| A-2          | I/O Cable Assembly                             | A-1  |

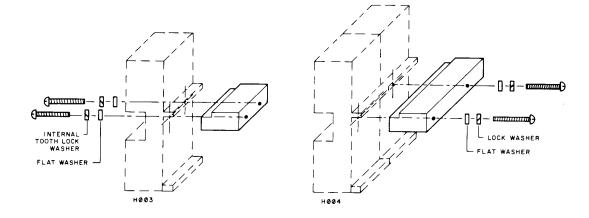

| A-3          | H003, H004 Connector Retaining Block Kits      | A-2  |

| A-4          | I/O Connector W850                             | A-3  |

| A-5          | Typical I/O Bus Connection in Device Using DCH | A-4  |

| A-6          | I/O Bus Interface                              | A-5  |

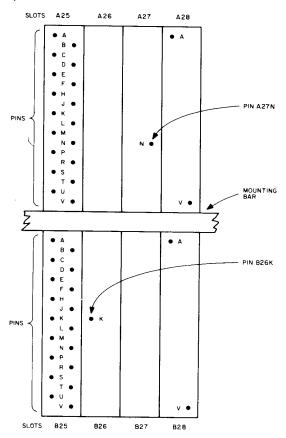

| A-7          | Interface Connectors and Pins                  | A-7  |

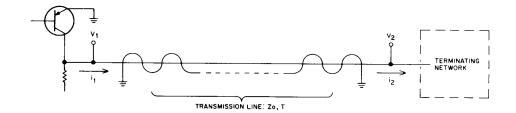

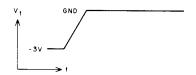

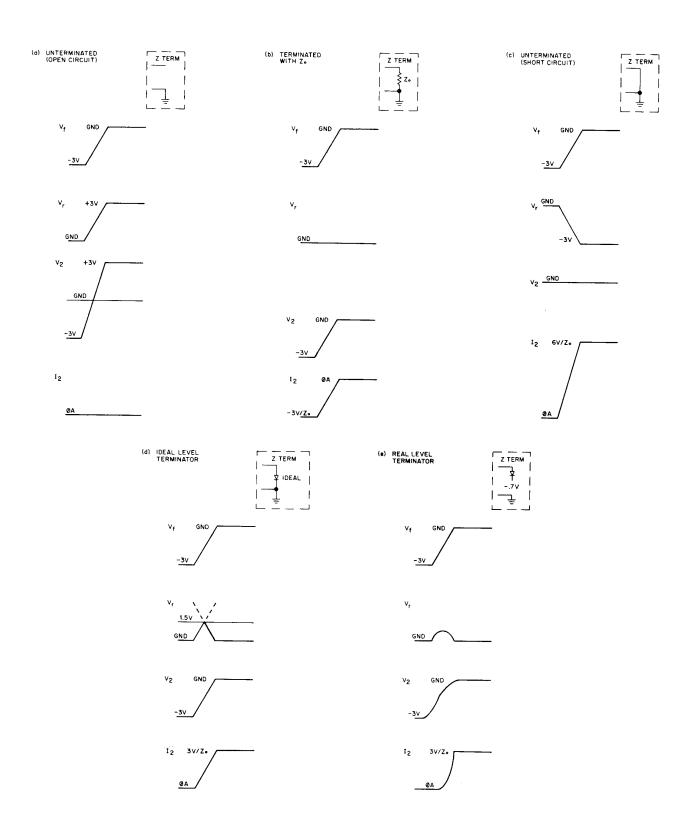

| A-8          | Level Transmission Line                        | A-8  |

| A-9          | Driving Waveform                               | A-8  |

| A-10         | Waveforms During Reflection                    | A-9  |

| B-1          | Circuit to Estimate Falltime                   | B-2  |

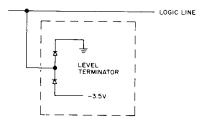

| B-2          | Level Terminator, Simplified Circuit           | B-2  |

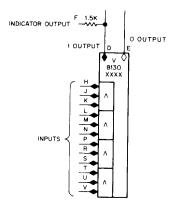

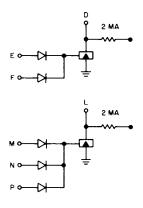

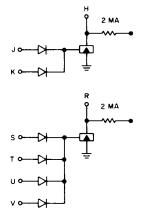

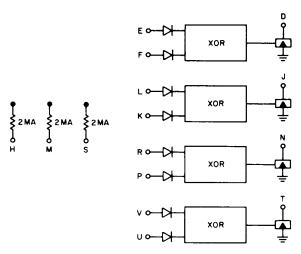

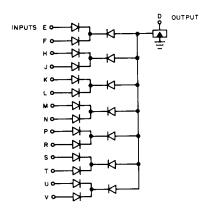

| B-3          | B130 Connections, Odd and Even Parity          | B-4  |

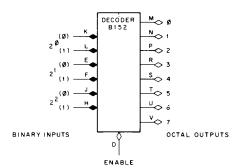

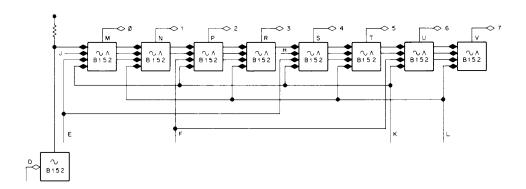

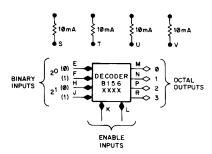

| B-4          | Internal Gating Structure, B152 Module         | B-7  |

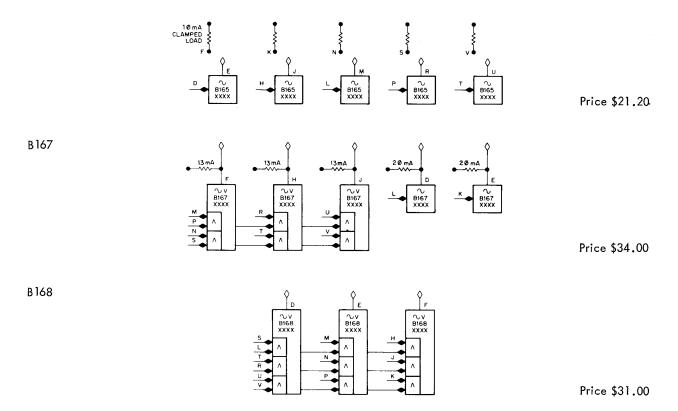

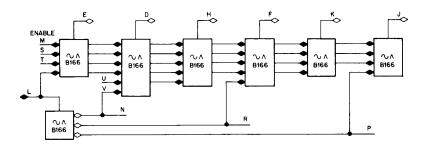

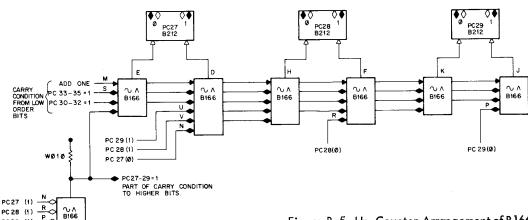

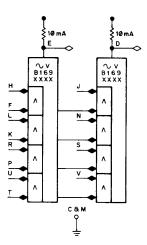

| B-5          | Up-Counter Arrangement of B166 Module          | B-12 |

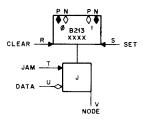

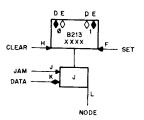

| B-6          | B213 With Negative Data Input                  | B-17 |

| B-7          | B213 As Bus Driver                             | B-18 |

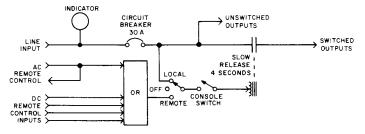

| B-8          | 841 Power Control Block Diagram                | B-55 |

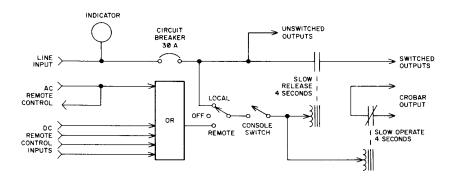

| B <b>-</b> 9 | 844 Power Control Block Diagram                | B-57 |

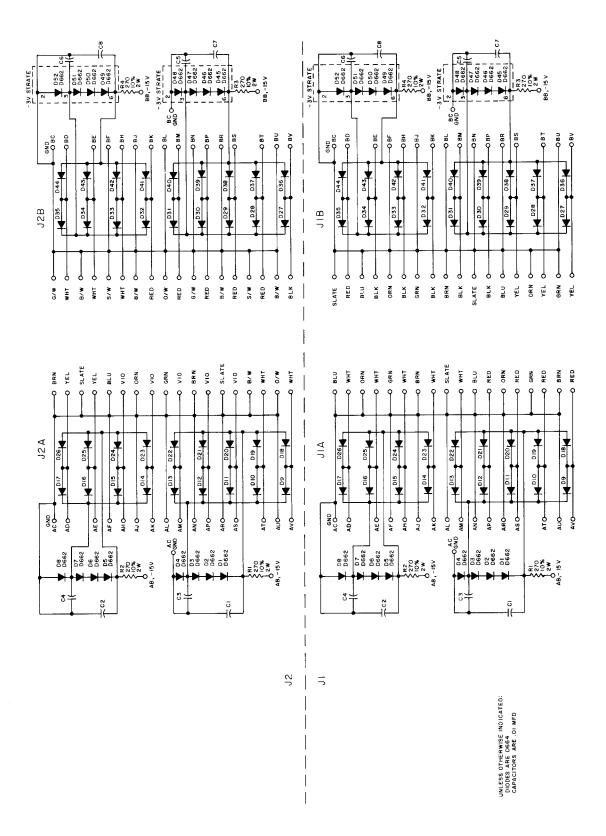

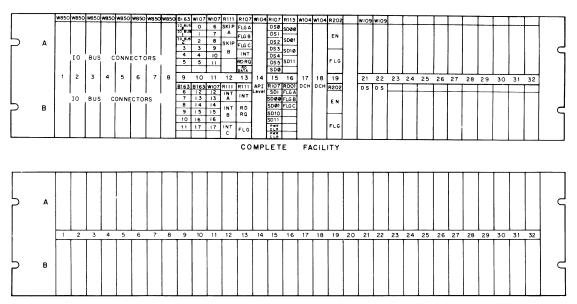

| C-1          | Complete Facility                              | C-4  |

| C-2          | I/O Bus Connectors                             | C-5  |

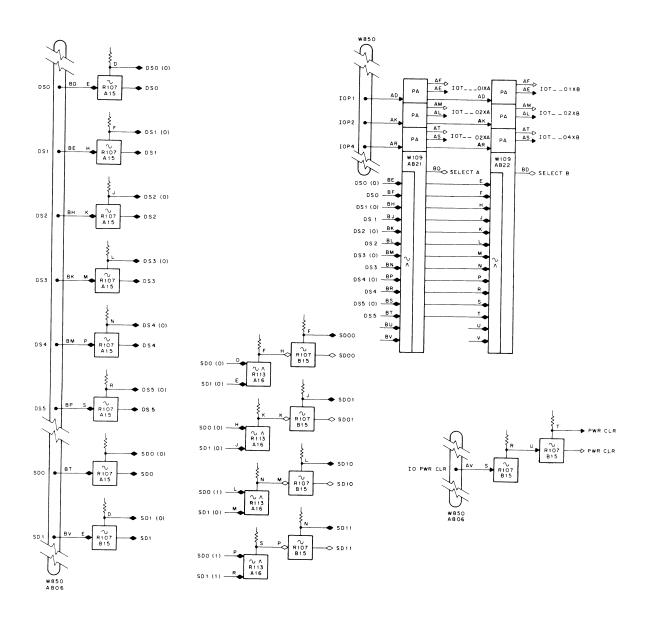

| C-3          | Command Decode Logic                           | C-6  |

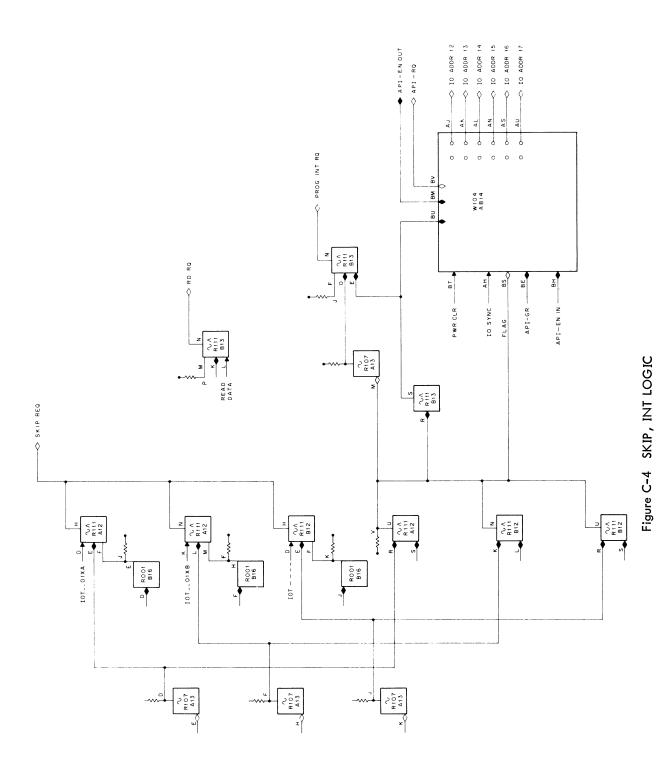

| C-4          | SKIP, INT LOGIC                                | C-7  |

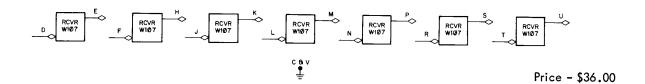

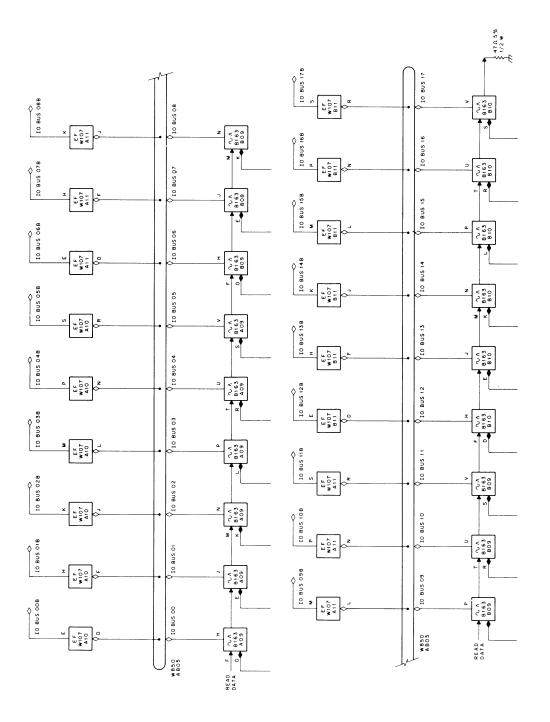

| C-5          | I/O Bus RCVRS and Gates                        | C-8  |

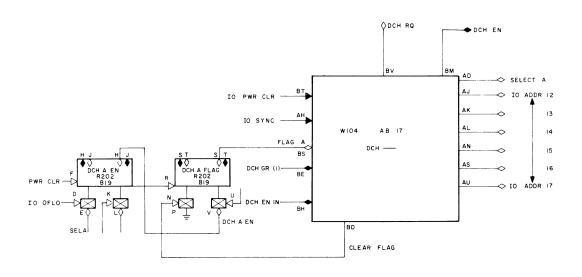

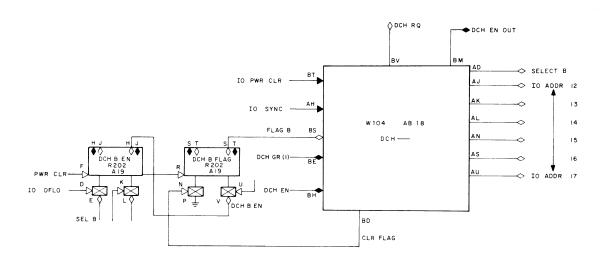

| C-6          | DCH Logic                                      | C-9  |

|              | TABLES                                         |      |

| 3-1          | Channel and Priority Assignments               | 3-14 |

| 3-2          | Standard Core Register Assignment              | 3-23 |

| 4-1          | Engineering Drawings                           | 4-7  |

# TABLES (Cont)

|              |                                        | <u>Page</u> |

|--------------|----------------------------------------|-------------|

| 4-2          | Data Transfer Rates and Latency Times  | 4-7         |

| A-1          | I/O Cable Specifications               | A-1         |

| A-2          | Electrical Characteristics of IO Cable | A-2         |

| A-3          | I/O Bus Interface Chart                | A-10        |

| B-1          | Inter-Series Pulse Conversion          | В-3         |

| B-2          | Input Loading (at ground)              | B-10        |

| B <b>-</b> 3 | Technical Data                         | B-10        |

#### INTRODUCTION

This manual provides the design engineer basic interface data for the PDP-9 and PDP-9/L computers manufactured by Digital Equipment Corporation of Maynard, Massachusetts. It is assumed that the reader is familiar with logic design, interface design, and basic PDP-9 programming.

Included in this manual are an introduction to DEC logic symbology; descriptions of the PDP-9 and PDP-9/L computers, with emphasis on input/output facilities; a complete description of interfacing techniques with detailed examples; some notes on terminal interfacing, margining, grounding; and general wiring rules. The I/O bus is summarized in Appendix A, a list of modules and their characteristics is presented in Appendix B, and a complete design example is given in Appendix C.

The following DEC reference documents provide additional design data: Logic Handbook (C-105), Industrial Handbook (C-110), PDP-9 User Handbook (F-95) and PDP-9/L User Handbook (DEC-9L-GRVA-D). The Logic Handbook and the Industrial Handbook provide complete specifications of DEC FLIP CHIP logic modules along with basic instructions in digital logic usage. The PDP-9 and PDP-9/L User Handbooks describe the instruction set for these computers and associated peripherals. Of particular interest are descriptions of the I/O instructions.

# CHAPTER 1 INTRODUCTION TO DEC LOGIC

The logic circuits of the PDP-9 and PDP-9/L computers are assembled with DEC discrete component FLIP CHIP modules (B, R, S, and W series modules). Logic schematics (called block schematics at DEC) using these modules are usually drawn with DEC pre-MIL-STD-806B logic symbols. Except for shape representation, these logic symbols conform to MIL-STD-806B with additional features added for clarity. Both of these logic symbol standards are discussed below.

The most striking feature of DEC logic (and most puzzling to those not accustomed to it) is that a logic signal may be true (logical 1) either when it is high or when it is low depending on the logic designer's preference. In any given logic network, signals which are high-when-true and signals which are low-when-true will ordinarily exist. Not infrequently, the same logic signal will have two electrical representations, one high-when-true and the other low-when-true. In addition, the logic designer has the freedom of using the logic negation

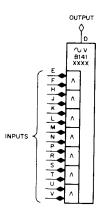

of a signal. This usage is indicated by a not sign (~), and overbar (XXXX), or a minus sign preceding the signal name (Figure 1-1). Whether a signal is true-when-high or true-when-low is indicated by the type of diamond or arrow (open or solid) in DEC logic symbols or by the presence or absence of a small circle in MIL-STD-806B logic. This convention permits logic design without regard to the inversion properties of most DEC logic. It also permits assignment of logic packages to the realization of the design without requiring undue redesign to account for gate inversions.

Frequently in larger logic networks, it is convenient to show a named signal's source without a connection to its load which is located elsewhere (Figure 1-2). To facilitate this, a small circle may be drawn at the end of the source line when using MIL-STD-806 logic symbols in order to show that the signal is truewhen-low.

Figure 1-1 Digital Logic Signals

Figure 1–2 Sources and Loads Shown Without Connections

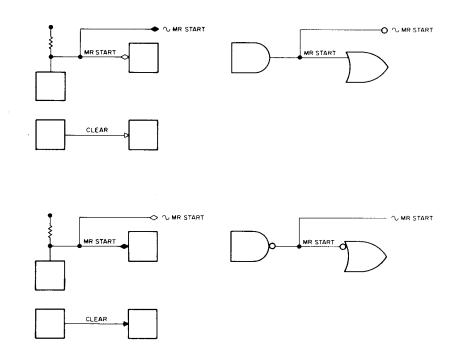

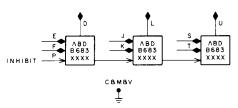

In DEC logic symbols, wired ANDs and wired ORs are not explicitly marked (Figure 1–3 and 1–4); they must be recognized. Due to the electrical properties of DEC's below ground logic (ground and –3V logic levels), a wired OR will usually occur at ground (high) and a wired AND at –3V (low). The B683 is an exception (refer to Appendix B).

Figure 1-3 Wired AND

Figure 1-4 Wired OR

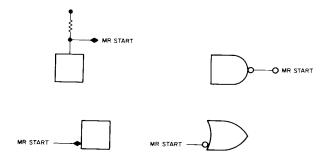

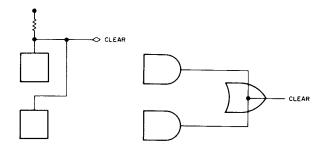

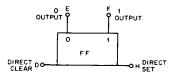

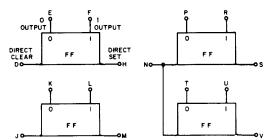

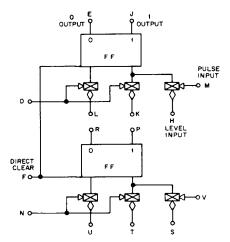

In DEC logic, most flip-flops are drawn with four outputs: one which is high when the flip-flop is in the 1 state, one which is low when the flip-flop is in the 1 state, one which is high when the flip-flop is in the 0 state, and one which is low when the flip-flop is in the 0 state. This convention allows the condition "the flip-flop is in the 1 (0) state" to be used with gates that require either high or low inputs without manipulating highs, lows, 1s and 0s. Although a flip-flop has four logical outputs, as noted above, it has only two electrical output connections, as the 1-high and 0-low connections are electrically equivalent (same output pin), as are the 1-low and 0-high connections. Except when the lines are quite short, connections to flip-flop outputs are not usually shown explicitly (Figure 1-5).

Figure 1-5 Flip-Flop Representation

In MIL-STD-806B logic drawings, DEC shows only the 1-high and 0-high output of a flip-flop, although all outputs are considered present for the purpose of logic design.

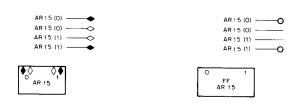

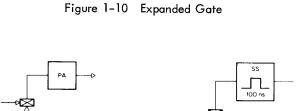

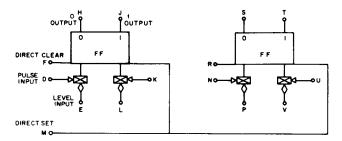

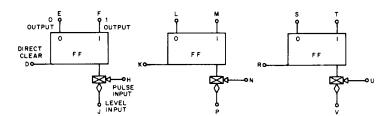

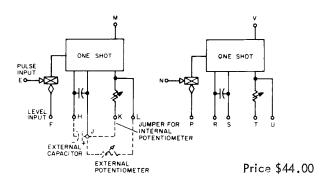

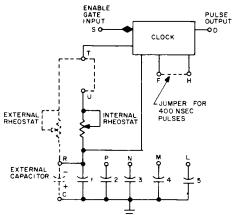

Mention should be made of the DEC diode-capacitor-diode (DCD) gate which is both an AND gate and a logic delay (Figure 1-6). This gate allows the output of a flip-flop to be sampled (with a DCD gate) at the same time the flip-flop state is changed. The flip-flop state seen by the DCD gate is the state prior to the change. The DCD gate generates an output pulse when the "level" input has been true (high) for approximately 400 ns and the "pulse" input has a 100 ns positive pulse or a positive-going (ground-going) level change with a rise time of less than 60 ns applied to it.

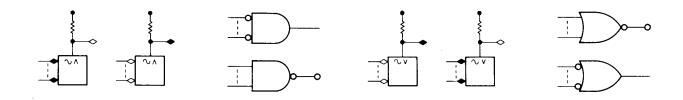

It is recommended that the DEC rectangular symbol for the DCD gate be used with either the older DEC logic symbols or with the MIL-STD-806B logic symbols in order to distinguish the quite different properties of the two inputs and to indicate the logic delay properties of the DCD gate. DEC logic sym-

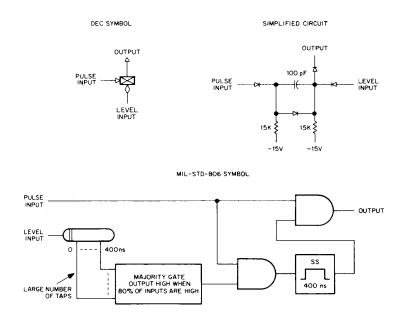

bols are all rectangular in shape. The function of the symbol is indicated by a descriptive notation within the rectangle. Examples of the more common symbols are shown in Figures 1–7 through 1–15.

Figure 1-6 DCD Gate

Figure 1-7 Inverter (NOT Gate)

Figure 1-8 AND Gate

Figure 1-9 OR Gate

Figure 1-11 Pulse Amplifier

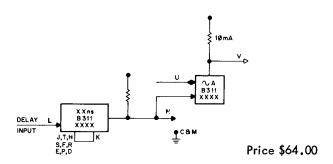

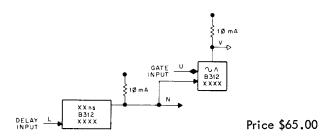

Figure 1-12 Monostable Multivibrator (Single Shot)

Figure 1-13 Monostable Multivibrator (Delay)

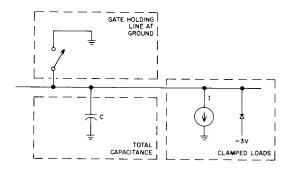

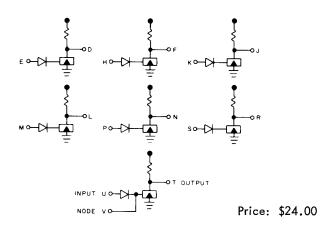

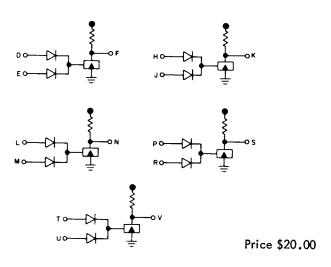

Figure 1-15 Clamped Load

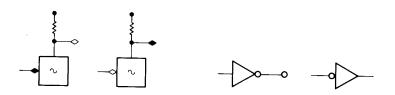

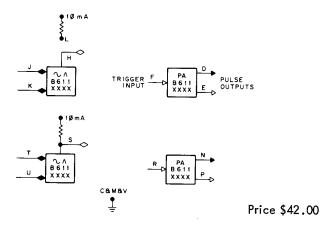

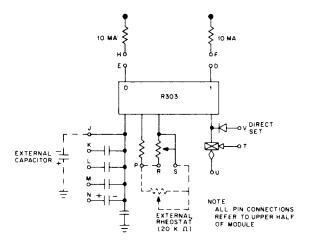

DEC makes use of the electrical equivalence of various logic configurations. As an aid to understanding, symbols are drawn to represent the logic function intended by the designer rather than as a single standard symbol for each module type. Thus, a particular module type may appear as several different symbols. (See Figure 1-16.)

Figure 1-16 Different Uses of a Particular Module

Occasionally, the trailing edge of a signal will be used to cause some action, usually by triggering a DCD gate. This usage is illustrated in Figure 1-17. For additional details on the types of logic modules available see the DEC Logic Handbook (C-105) and the module descriptions in Appendix B.

Figure 1-17 DCD Usage

# CHAPTER 2 THE PDP - 9 and PDP-9 / L COMPUTER SYSTEMS

## 2.1 PDP-9

The PDP-9 is a modular, medium scale digital computer. The basic system consists of a PDP-9 central processor with 8192 18-bit words of core storage (1 µs cycle time), a Teletype Model K SR33 Teletypewriter with keyboard and printer (10 cps), a paper tape reader (300 cps), and paper tape punch (50 cps). Also included are a real-time clock, hardware read-in, eight data channels, and a direct memory-access port. For details of expanded systems, see the PDP-9 User Handbook (F-95).

### 2.2 PDP-9/L

The PDP-9/L is a highly modular medium-scale digital computer. The basic system consists of a central processor with 4096 18-bit words of core storage (1.5  $\mu s$  cycle time) and a Teletype Model ASR33 Teletype-writer and punch (10 cps) with keyboard and printer (10 cps). Also included are eight data channels and hardware read-in. No direct memory access port is available either in the basic or expanded version. For details of expanded PDP-9/L systems, see the PDP-9/L User Handbook DEC-9L-GRVA-D.

Both the central processor and the input/output facilities of the PDP-9 and PDP-9/L systems are very similar. Significant differences are pointed out in the text.

### 2.3 COMPUTER SUBSYSTEMS

The major subsystems of the two computers are the central processor unit (CPU), core memory, and the input/output facilities. These are described below.

# 2.3.1 Central Processor Unit

The PDP-9 and 9/L central processor unit (CPU) is a single address binary processor. This section describes the internal organization of the major CPU registers and is intended to give the user sufficient understanding of CPU instruction and data handling

to prepare him for input/output interfacing techniques described later. For detailed descriptions of the CPU, refer to the PDP-9 or PDP-9/L maintenance manual.

The CPU employs a bus system on which data is transferred at dc levels between registers. In this bus system, all active registers use simple circuit designs for transfers which minimize timing problems.

The control elements and registers of the CPU that govern gating of information are described in the following paragraphs. (Refer to Figure 2-1.)

# 2.3.1.1 Control Elements and Registers

Instruction Register (IR) - The IR accepts the five most-significant bits of each instruction word fetched from memory. The four most significant bits constitute the operation code and, when decoded, indicate the entry point to the control memory microinstruction sequence necessary to effect system response. The fifth bit signals when the fetched instruction indicates indirect addressing.

Control Memory (CM) - The CM stores the sequence of internal microinstructions required to fetch and execute a program's instructions, to effect operation of the data channels, and to respond to operator commands initiated at the control console. It is a very fast, read-only, magnetic-core storage unit, prewired with the sequences.

Control Register (CR) - The CR provides gate control signals to the transfer buses and to the active registers. The register supplies new address information to the CM based on conditions sensed.

2.3.1.2 Major Registers - The major registers in the processor are as described in the following paragraphs.

Adder (ADR) - The 18-bit ADR functions as a fast adder for arithmetic operations and as the transfer path for inter-register transfers and shift operations. It also increments the PC and MB registers as required. Entry to the ADR is via the A bus and/or the B bus, under control of CR-developed gating control level. The ADR operates at a 5 mc rate to provide an inter-register transfer time of 200 ns.

Accumulator (AC) - The AC is an 18-bit register that retains the result of arithmetic/logical operations for the period between instructions. The AC can be cleared and complemented; its contents can be rotated right or left with the link. The contents of the memory buffer register can be added to the contents of the AC with the result left in the AC. The contents of both the MB and AC can be combined by the logical operation AND and exclusive OR, with the result remaining in the AC. The inclusive OR can be formed between the AC and the DATA switches on the operator console and the result can be left in the AC. For all program controlled transfers, information is transferred between core memory and an external device through the accumulator.

Link (L) - This 1-bit register is used to extend the arithmetic capability of the accumulator. In 1's complement arithmetic, the link is an overflow indicator; in 2's complement arithmetic, it logically extends the AC to 19 bits and functions as a carry register. The program can check overflow into the link from the accumulator to greatly simplify and speed up single and multiple precision arithmetic routines. The link can be cleared and complemented and its state sensed independent of the AC. It is included with the AC in rotate operations and in logical shifts.

Arithmetic Register (AR) - The AR functions with the AC to perform arithmetic and logic operations. It is not accessible to the programmer. Its operation is a function of the microinstruction sequence in the CM.

Multiplier-Quotient Register (MQ) - The optionally implemented extended arithmetic element (EAE) adds the logic of the MQ to the basic PDP-9. The MQ is 18 bits long and holds the multiplier during multiplication instructions and receives the low-order 18 bits of the resulting product. During division operations, it holds the low-order 18 bits of the dividend and, at the completion of the divide instruction, it contains the quotient. It can also be used as an extension of the AC for 36-bit shift operations and for data normalizing operations.

Program Counter (PC) - The PC determines the program sequence; that is, the order in which instructions are performed. This 13-bit register contains the address of the memory cell from which the next instruction is to be taken. Addition of the memory extension control option expands the PC to 15 bits for addressing up to 32,768 locations.

Memory Buffer Register (MB) - All information transferred into, or out of, core memory passes through the 18-bit MB. Information is read from a memory cell into the MB and is rewritten into the cell in one cycle time. Instructions and data are brought from core memory into the MB for processing. The MB also serves as a buffer for information transferred between core memory and the external device in data channel transfers. As an example of operation, the CPU would perform the instruction to add the contents of the MB to those of the AC by issuing the following microinstructions (see Figure 2-1).

MB OUT /THIS OPENS THE MB TO THE /B BUS

AC OUT /THIS OPENS THE AC TO THE /A BUS

The adder now adds the contents of the A and B buses, and the output of the adder is fed back to the input mixers of the major registers.

NO SHIFT /THE OUTPUT OF THE ADDER IS

/GATED ONTO THE "0" BUS (OR

/INPUT GATES TO THE MAJOR

/PROCESSOR REGISTERS)

AR IN /THE "0" BUS (OR ADDER OUT-/PUT) IS TRANSFERRED TO THE /AR

AR OUT /OPEN AR TO "A" BUS

NO SHIFT /GATE ADDER OUTPUT TO "0"

/BUS

AC IN /TRANSFER DATA TO AC

### 2.3.2 Core Memory

2.3.2.1 PDP-9 Memory - PDP-9 core memory (Figure 2-1) operates with a complete cycle time of 1.0 µs. Each 8192-word core memory module contains a core stack, sense amplifiers, drivers, and a memory address (MA) register. The MA sets up the memory location (address) to be used for data retrieval or storage.

System core memory can be expanded from the basic 8,192 words up to 32,768 words in 8,192-word increments. Such expansion requires implementation

Figure 2-1 CPU Control Elements and Registers

of the optional Type KG09A Memory Extension Control, to extend PDP-9 addressing capability.

Each PDP-9 memory module has a two-port capability for data entry and retrieval. One port, connecting to the memory bus, services the processor; the other port allows a peripheral device direct and immediate access to memory for fast data transfers via a direct memory access (DMA) bus. A device request for DMA service has priority over a processor request, which is deferred until DMA operation terminates. The optional Type DM09A Multiplexer Adapter permits concurrent servicing of up to three DMA peripherals and assigns each a fixed priority.

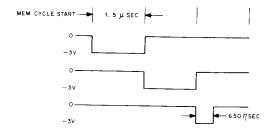

2.3.2.2 PDP-9/L Memory - The PDP-9/L core memory is a 4-wire, 3D system with a cycle time of 1.5 μs. The basic PDP-9/L contains 4,096 18-bit words and is expandable in 4,096-word sections up to 32,768 words. The Type KG09A Memory Extension Control option is required for memory expansion above 8K. Each PDP-9/L memory has a one-port capability, i.e., no direct memory access is available.

# 2.3.3 Input/Output Facilities

One of the most useful features of both the PDP-9 and PDP-9/L computer systems is the flexible, high capacity input/output facility (Figure 2-1) with which the computers communicate to such DEC peripherals as displays, analog-digital and digital-analog converters, magnetic tape controllers, data communications equipment, disk systems and, for the PDP-9, drums. The design techniques developed for interfacing special systems are simple and inexpensive; for example, it is possible for the PDP-9 and PDP-9/L to communicate with their associated peripherals in two ways:

- a. Under direct program instruction control (Program Controlled Transfers)

- b. Under channel control (Channel Transfers)

Program controlled transfers are implemented under direct supervision of a stored program. Machine instructions, called IOT instructions, contained in this program carry out the necessary internal and external (device) signal conditioning to effect the desired information transfer. This method requires very little device interface logic and is the least

expensive method for slow speed transfers (50,000 words per second for the PDP-9 and 33,000 words per second for the PDP-9/L). However, program controlled transfers require the use of major registers in the CP which must be cleared of vital information before a transfer occurs.

Channel transfers require more logic in the external device, but are less demanding of computer hardware and time. In general, they are used to move large blocks or arrays of data between machine and peripheral at rates of from 6 to 20 times those of program-controlled transfers.

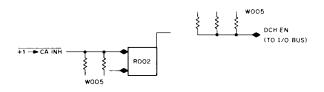

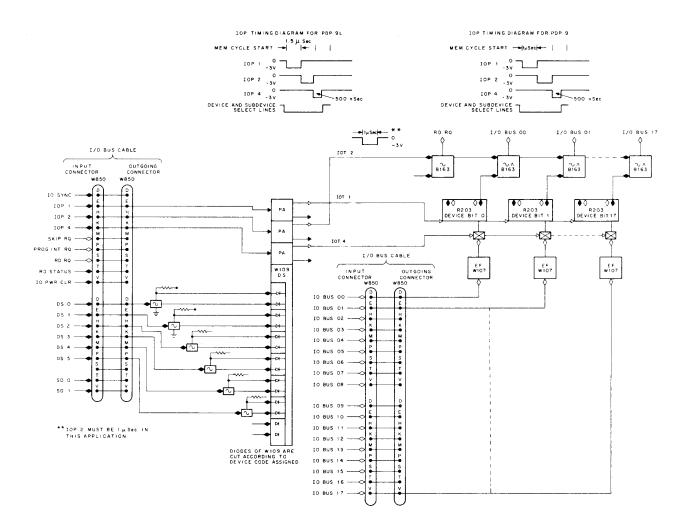

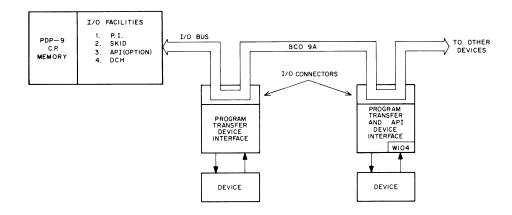

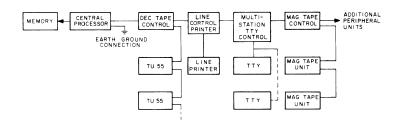

The PDP-9 uses two distinct channel transfers, the data channel (DCH) and direct memory access (DMA) Figure 3-1. The data channel requires from three to four memory cycles to effect an 18-bit word transfer and uses some of the CP control logic. The PDP-9/L has only the data channel facility which is the same configuration as in the PDP-9; however, the 1.5 µs cycle time of the PDP-9/L slows transfer to two-thirds of the rate of the PDP-9 transfers.

Both computers communicate with peripheral devices by program control and data channel through the I/O bus which consists of two 36-pair cables with male connectors at both ends. Each peripheral is chain linked to a common interface point at the central processor. Signals between the bus and central processor are shown in Figure 2-1. Each signal is described in detail and some of the computer control logic which serves them is shown in the following section.

A summary of the physical properties of the I/O bus and descriptions of the signals it serves are given in Appendix A. The DMA channel of the PDP-9 has its own bus, and will be covered separately.

2.3.3.1 Program Controlled Transfers – When there are a small number of peripherals and no complex timing or stringent priority considerations in a computer system, data can be transferred by IOT instructions via the I/O bus to and from peripherals (most applications fall into this category). Hardware cost is low since the computer supplies most of the control, but computer time may be high.

There are four computer subsystems used in programcontrolled transfers. These are: IOT instruction logic, read status logic, program interrupt and skip logic, and API logic. Each of these is described below. IOT Instruction Logic - Input/output (IOT) instructions initiate the transmission of signals through the I/O bus to control peripheral devices, sense their status, and effect transfers between them and the processor. When an IOT instruction is transferred to the MB (Figure 2-1) the computer logic decodes it according to the format shown in Figure 2-2.

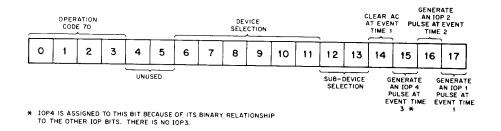

The PDP-9 IOT instruction has the following characteristics.

- a. An operation code of 70g.

- b. An 8-bit selection code to allow the selection of up to 256 decoders. Outputs of these decoders are used by peripheral devices to enable various functions such as data transfers.

Figure 2-3 IOP Timing Diagram for PDP-9

c. If the device has requested an input transfer (to the computer) by grounding the RD RQ signal of the I/O bus, the contents of the 18 data lines, I/O

Figure 2-2 PDP-9 IOT Instruction Format

c. A command code (bits 14-17) capable of being microprogrammed to clear the AC and/or issue up to three pulses to the I/O bus (IOP1, IOP2 and IOP4).

When an IOT instruction is decoded in the IR, the following sequence occurs (Figure 2-1).

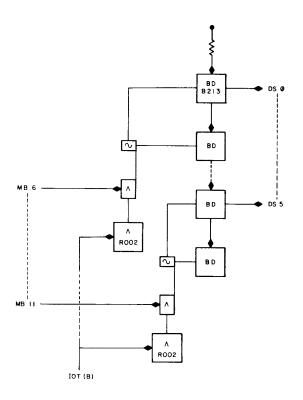

- a. The bit pattern placed in MB bits 6 through 13 is buffered by the IOT control logic (where it emerges as DS0 through DS5 for MB6 through MB11, and SD0, SD1 for MB12 and MB13) and placed on the I/O bus cable. Assertion or binary 1 is -3V and binary 0 is ground. (The device logic used to respond is explained later.)

- b. The microprogrammed signals IOP1, IOP2 and IOP4 are generated by the IOP control logic, if they are selected by the instruction, and appear in time sequences defined by the IOP timing diagram (Figures 2–3 and 2–4). They are used by the device to effect data transfers, sense the status of a device, or issue commands.

BUS 00-17, are jammed into the AC register of the CP. If, during the IOT instruction, the RD RQ line is not grounded, the computer will place the contents of its AC onto the 18 data lines. The proper timing to effect the transfer is given in Chapter 4.

Figure 2-4 IOP Timing Diagram for PDP-9/L

There are five basic control circuits in the PDP-9 and PDP-9/L I/O sections, which handle the IOT instructions. Part of each circuit is described below. Characteristics of the driver or receiver modules are presented in Appendix B.

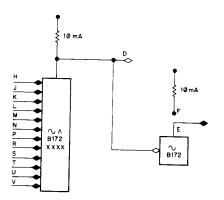

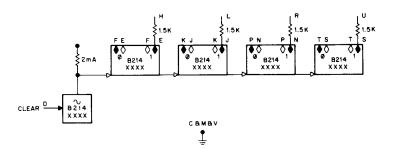

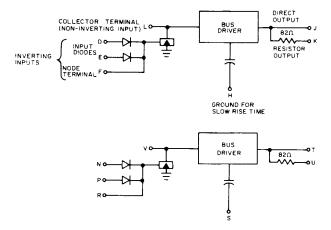

MB Bits 6 through 13 Buffering - Figure 2-5 shows how MB bits 6 through 13 of the CP are gated with the IOT (B) signal (always present during an IOT instruction) and then drive DEC Type B213 Bus Drivers down the I/O bus in the form of signals DS0 through DS5 for MB6 through MB11 and SD0, SD1 for MB12 and MB13. Any device on the bus must be able to decode these signals.

Figure 2-5 MB, DS or SD Signal Buffering

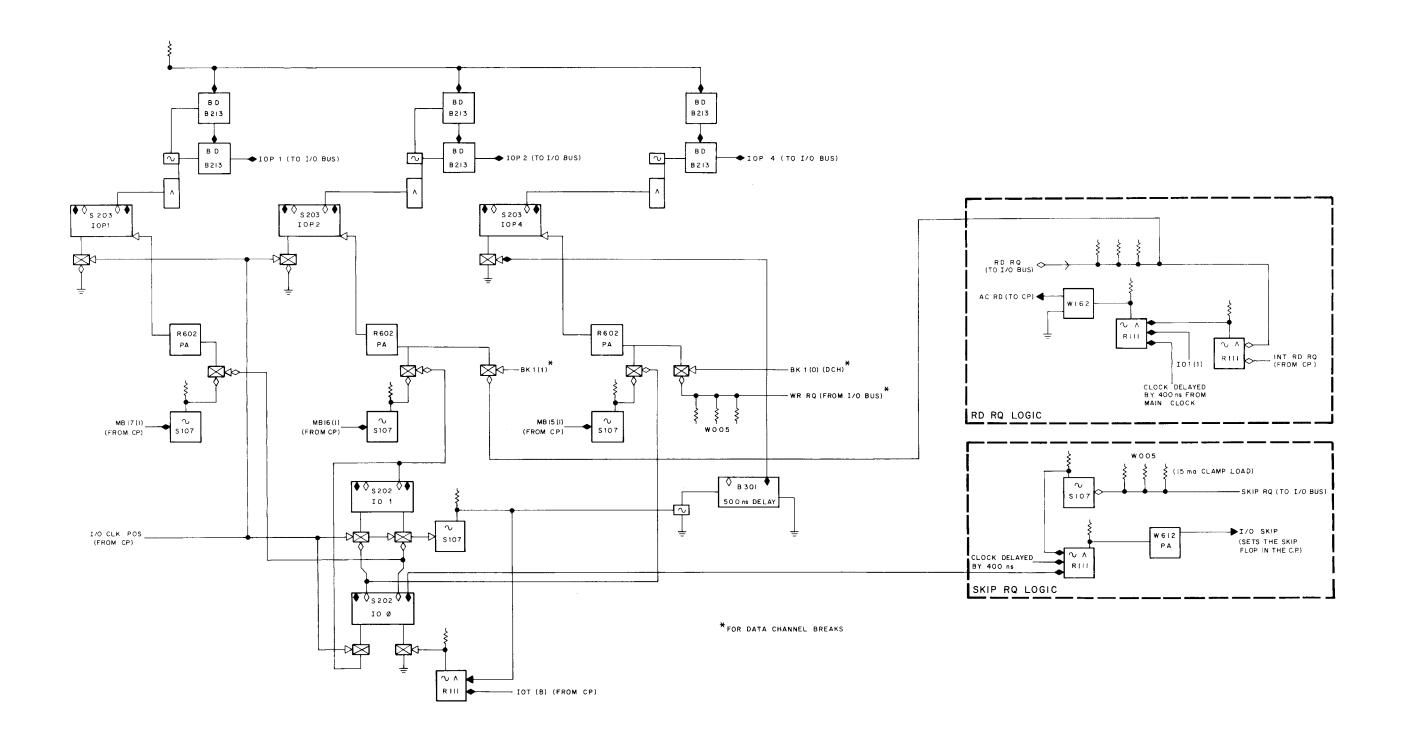

IOP Control Logic - The IOP control logic is shown in Figure 2-6. A 2-bit counter (IOO, IO1) is driven by the I/O CLK POS clock pulse during the IOT instruction. The counter pulses each of the three R602 Pulse Amplifiers in turn. If any one is enabled by the appropriate MB bit 15, 16, or 17, the associated flip-flop, IOP1, IOP2, or IOP4 is set. IOP1 and IOP2 are reset by the next I/O CLK POS pulse while IOP4 is reset by a delay.

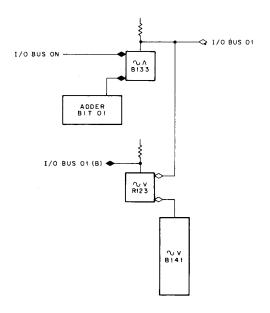

Data Lines (I/O Bus 00 through I/O Bus 17) - Figure 2-7 indicates the modules which manipulate the data lines. I/O bus line 01 is illustrated as an example.

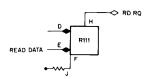

RD RQ - This ground signal, which must be issued by the device requesting data transfer to the computer, is gated with IO1 to the IOP counter and is used to generate an AC RD control pulse to the CP (see Figure 2-6).

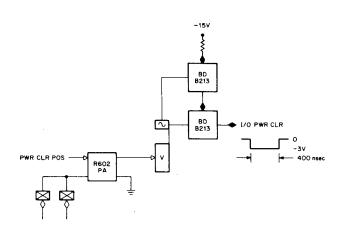

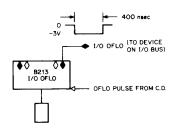

I/O PWR CLR - Whenever it becomes necessary to reset a device to its initial conditions, I/O PWR CLR pulses, which are 400 ns (nominal width) negative-going signals, are issued. This occurs during power turn-on, actuation of the IO RESET switch, or the occurrence of a CAF (clear all flags) instruction. The output driver for I/O PWR CLR is shown in Figure 2-8.

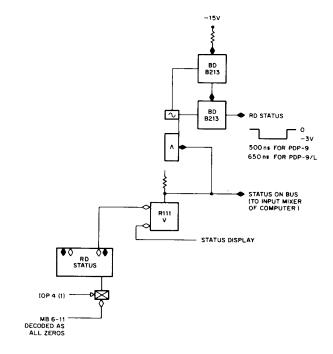

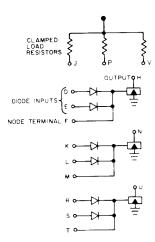

Read Status Logic - The IOT instruction IORS = 700314 sends a pulse down the RD status line of the I/O bus. This signal can be used to place various device flags onto the data lines. The computer then reads the data on these lines into its AC for evaluation. These status bits can also be displayed on the register indicators by turning the console switch to position STATUS (STA on the PDP-9/L) and stopping the computer. In this situation, a train of pulses is placed on the RD status line. The output logic for the RD status line is shown in Figure 2-9.

Program Interrupt (PI) and SKIP Logic – To avoid for– cing the computer to continually monitor slower devices for their ready conditions in program controlled transfers, program interrupt and SKIP facilities are built into these computers. The program interrupt logic allows a device to force the running computer into a break state (i.e., a break from normal program sequence) by grounding the PROG INT RQ signal of the I/O bus. Before entering this break state the computer completes its current instruction or higher order break (such as DCH request or API or real-time clock), stores the contents of the PC, link, state of extended memory, state of memory protect and content of extended PC in location 0 and executes the instruction in location 1 (see Figure 2-10). This instruction is usually a JMS to a SKIP routine.

Figure 2-6 IOP Control Logic

Figure 2-7 Typical Input/Output Logic for Data on I/O Bus Lines 00 through 17

Figure 2-8 I/O PWR CLR Logic

The SKIP routines consist of a set of IOT instructions which send IOP1 pulses to all devices; thus interrogating each device which may be requesting the PI (many devices can tie onto the PROG INT RQ line). If a device returns the pulse via the SKIP RQ line of the I/O bus, the computer skips the next instruction. Thus, the device has been identified and can be serviced by the computer.

Figure 2-9 RD Status Logic

| INFORMATION                                                                                                                                                              | L | E M | MP | EPC | P C |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----|-----|-----|

| SIZE (BITS)                                                                                                                                                              | 1 | 1   | 1  | 2   | 13  |

| L = LINK CONTENT EM - STATE OF EXTEND MODE MP - STATE OF MEMORY PROTECT MODE EPC - CONTENT OF THE EXTENSION TO PROGRAM COUNTER AND; PC = CONTENT OF THE PROGRAM COUNTER. |   |     |    |     |     |

| THE INTERRUPT SERVICING SUBROUTINE MUST SAVE AND RESTORE THE CONTENTS OF THE ACCUMULATOR.                                                                                |   |     |    |     |     |

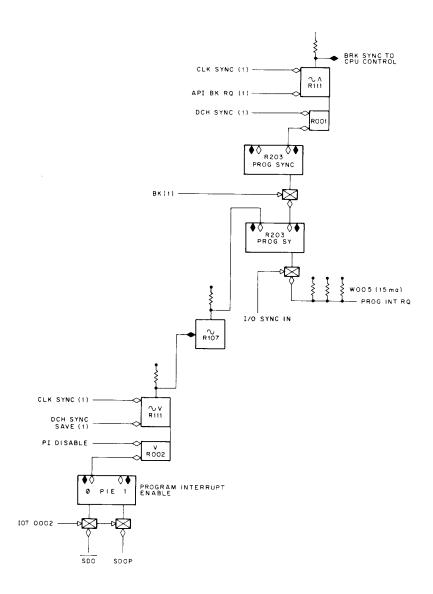

Figure 2-10 Program Interrupt Storage Word Format

The I/O logic used by the computers to effect the PI facility is shown in Figure 2-11. The flip-flop PIE (program interrupt enable) is set with the ION instruction (700042). Then, if CLK SYNC, DCH SYNC and PI disable are all low, the flag PROG SYNC can be set by I/O SYNC IN if a PROG INT RQ is initialized by some device. A control pulse called BK (1) then sets PROG SYNC which requests control memory to accept an odd address, which forces the computer to put the PC, link and extended memory address into location 0. The PC then goes to 1 and this becomes the address of the next instruction executed.

Figure 2-11 I/O PI Logic

Figure 2-6 shows the SKIP facility control logic. Here, the grounded SKIP RQ line is inverted, gated with bit I/O (1) of the counter, and finally triggers the W612 Pulse Amplifier which sets the CP SKIP flip-flop. This flip-flop forces the computer to add 2 to the PC instead of 1.

Automatic Priority Interrupt (API) System - The PI facility becomes inefficient on a system with a large number of peripherals which require a hierarchy of priorities or data rates of more than 50,000 words per second. In this case, central processor overhead time can be reduced with a multichannel interrupt

system. Such an option is the KF09A Automatic Priority Interrupt Facility provided in the PDP-9 system. A complete description of this option is given in a separate manual, DEC-08-I5AA-D. However, Chapter 3 will outline the interfacing techniques required to use in the API.

2.3.3.2 <u>Channel Controlled Transfers</u> - The PDP-9 has two separate facilities for channel controlled transfers. There are data channel and direct memory access. The PDP-9/L, however, uses only the data channel facility which is identical to that in the PDP-9 except for timing.

Channel transfers, in general, differ from program-controlled transfers in that they are designed to manipulate blocks of data, rather than a word at a time (a block of data is defined as a series of data words stored in sequence in some device; i.e., core memory or disk). A block of data can be completely specified for any device by the address of its first word and the number of words in the block. Thus, to specify a block and its destination between any two devices, three variables are necessary.

### These are:

- a. Present first address;

- b. First address of its destination;

- c. Word count of the block.

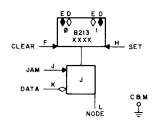

# Data Channel (DCH)

Each device on the DCH is assigned two locations in memory. The first location is defined as the word count (WC) register and is programmed to contain the 2's complement of the word count of the block. The second location is programmed to contain a value one less than the address in memory that will send or receive the first word of the block. This location is called the CA (current address) register.

After the computer has set up the WC and CA registers and has specified the address of the device's first word, it enables the device and returns to its main program. The device then informs the computer via the DCH RQ (data channel request) line when it wants to transfer each word and specifies on I/O ADDR lines (I/O address) its WC address. The CA register automatically becomes WC+1. At any given transfer, the WC and CA locations are incremented by the computer. Then, the word on the bus is passed into the address specified by the contents of CA. If, during the transfer, WC overflows; that is, the last word of the block has been reached, an I/O OFLO (overflow pulse) is transmitted to the device. During DCH transfers, the CP suspends execution of the main program. The MB register is used as a buffer between memory and device (see Figure 2-1).

DCH Logic - The I/O bus contains seven lines unique to the DCH, which are DCH RQ, DCH GR(1), DCH EN, ADD OFLO, I/O OFLO, INC MB and +1 +CA

INH. Other I/O bus signals used by the DCH include: IO PWR CLR, IO SYNC, IO ADDR 03 →IO ADDR17, WR RQ, and RD RQ.

The DCH RQ (request) line asks for a data channel break from the computer; the DCH GR (grant) signal represents the computer's permission to "go ahead." DCH EN (enable) is a -3V line that is linked from device to device to establish priority among the group tied to DCH. It can enable one device to post a DCH RQ or prevent it from doing so if a higher priority device has already requested it.

ADD OFLO (address overflow) and I/O OFLO (overflow) are signals issued by the computer to indicate overflow conditions. I/O PWR CLR (power clear) is used in each device to set all registers to their initial states (i.e., clear all data registers, interrupt flags, etc.). I/O SYNC (synchronize) is a timing pulse, I/O ADDR 03 to I/O ADDR 17 (address) specify word count registers assigned in memory to each device. RD RQ (read request) is a signal issued by a device to inform the computer that information must be transferred to computer memory. WR RQ (write request) is also issued by the device only to inform the computer that the transfer must be out of computer memory. INC MB causes a single cycle DCH break where the contents of the word located at the address specified on I/O ADDR lines is incremented by 1.  $+1 \rightarrow CA$  INH, when grounded by a device, inhibits the computer from incrementing the CA during the DCH break.

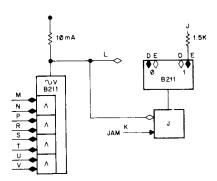

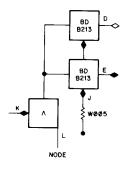

I/O SYNC pulses (Figure 2-12) occur on computer CLK POS pulses only where no AM SYNC (DMA) is present, and where no IOT instruction is currently in progress (IOT(0)). Output drivers are B213 Bus Drivers.

DCH RQ Logic - If a DCH RQ ground level (Figure 2-13) is present on the enabling input to the DCH SYNC flag, then I/O CLK POS will set this flag provided IOT(0), CLK SYNC(0), etc. are present. This means that this flag is set if no IOT, RTC, PI or optional API operation is in progress. The DCH, therefore, cannot interrupt any of these operations. However, once set, DCH SYNC inhibits the CLK, and the API takes priority.

DCH SYNC sets DCH SYNC SAVE which ultimately requests the break state from the CP. DCH SYNC also drives a B213 Bus Driver which supplies DCH GRANT to the device. DCH GRANT requests that the device specify its WC address.

Figure 2-12 I/O Sync Logic for the Computers

Figure 2-13 DCH RQ Logic for PDP-9 and PDP-9/L

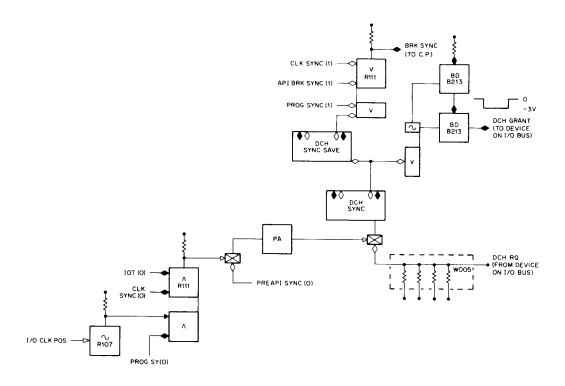

IO OFLO Logic - The IO OFLO signal, derived from a B213 in the CP (Figure 2-14) occurs during the WC cycle of a data channel break if the WC address overflows to all zeros.

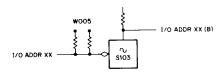

IO ADDR Input Logic – The IO ADDR input logic (Figure 2–15) consists of Type S103 Inverters and two 5-mA clamped loads from a W005 module. The output of this circuit is the IO ADDR XX(B) signal

which goes to the input mixer circuit shown in Figure 2-15.

Figure 2-14 IO OFLO Output Logic

Figure 2-15 IO ADDR Input Logic to Computer

DATA OFLO Logic - The DATA OFLO signal is derived from a B213 flip-flop as shown in Figure 2-16. DATA OFLO is a 200 ns pulse, gated onto the I/O bus in the middle of the third add to memory DCH cycle, which signals an incorrect sum occurred. This happens when the contents of the MB and the contents of the I/O bus are of like signs and their sum has the opposite sign. If the contents of the MB and the contents of the I/O bus have opposite signs DATA OFLO cannot occurs. Thus,

DATA OFLO occurs when:

(MB) + (I/O Bus) >

$$2^{17}$$

- 1

OR

(MB) + (I/O Bus) <  $-2^{17}$

Figure 2-16 DATA OFLO Logic

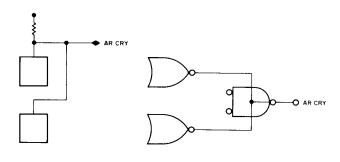

+1 → CA INH and DCH EN Logic - The +1 → CA INH is a signal from the device to the computer. It is applied to an R002 Diode Gate and two 5-mA clamped loads. DCH EN is a -3V signal from the computer to the device and is produced by three 5-mA clamped loads. Both of these signals are shown on Figure 2-17.

INC MB Signal - The INC MB signal is distributed between I/O facilities and control memory. Loading for INC MB is the same as that for RD RQ, shown in Figure 2-6.

## Direct Memory Access Channel (DMA)

The DMA logic of the PDP-9 is sufficiently complicated to require reference to the PDP-9 Maintenance Manual for logic schematics and explanations.

Figure 2-17 +1 → CA INH and DCH EN Logic

# CHAPTER 3 INTERFACING TO THE PDP - 9 and PDP-9 / L COMPUTERS

This chapter presents techniques and examples for interfacing special devices to either the PDP-9 or PDP-9/L computer. The methods shown have been designed and implemented by DIGITAL engineers and by no means represent any design rule restrictions. In many applications modules or circuits other than those shown can be employed for the same desired function at the discretion of the design engineer. In all cases, however, the bus rules summarized in Appendix A of this document must not be violated.

Both the PDP-9 and PDP-9/L communicate with their associated peripherals through I/O bus cables. Three transfer techniques can be used:

a. Program controlled transfers for systems without optional API.

- b. Program controlled transfers using the API facility.

- c. Data channel transfers.

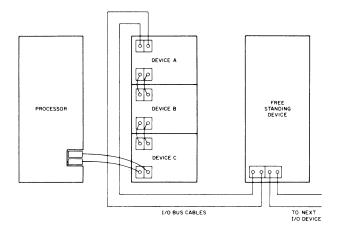

Program controlled transfers occur under direct control of IOT instructions. Data channel transfers are set up by IOT instructions, but are carried out independently. All transfers take place between the computer and its peripherals through a parallel I/O bus system (Figure 3-1). Each device interface has two sets of I/O cables; (these are two cables per set) an input set which comes from the computer or from the previous device, and an output set that goes to the next peripheral device on the line. Input cables are jumpered to the output cables within the device.

Figure 3-1 Interfacing to the PDP-9 and PDP-9/L Computers

# 3.1 PROGRAM CONTROLLED TRANSFERS

## 3.1.1 Signal Summary

The signals used with program controlled transfers in the computers were described in Chapter 2. The configuration of the PDP-9 and PDP-9/L I/O control logic which generated these signals was also shown. For characteristics of the modules driving, or receiving from the computer bus refer to either the Digital Logic Handbook (C-105) or Appendix B of this manual.

In summary, there are a total of seven sets of signals for non-API program controlled transfers. These are as follows:

# DSO through DS5, SD0, SD1

These signals correspond to the bit pattern in MB bits 6 through 13 during the IOT instruction and are used to address the device.

## IOP1, IOP2 and IOP4

These control pulses decoded from MB bits 17, 16, and 15 are used by the device to effect transfers or sense control functions.

## RD RQ

A signal which the device must place at ground if it requires a data transfer into the computer.

### Data Lines

I/O Bus 00 through I/O Bus 17 carry an 18-bit word to or from the AC during program controlled transfers.

### I/O PWR CLR

Clears all device flags committed to it.

### PROG INT RQ

Causes the computer to go into a "break" state when enabled.

# SKIP RQ

A ground on this line will force the computer to skip the next instruction after completion of the current IOT instruction.

# 3.1.2 Peripheral Interface Requirements

The bused system of input/output data transfers imposes the following requirements on peripheral equipment using the programmed data transfer facility.

- a. Each device must have the ability to sample the select code generated by the computer during IOT instructions. When selected, it must be capable of producing sequential command pulses in accordance with the computer-generated IOP pulses. Circuits performing these functions in peripheral devices are called device selectors (DS). One double-sized module Type W109 provides all these functions.

- b. Each device receiving output data from the computer must contain gating circuits at the input of a receiving register which are capable of strobing the data on the I/O bus into the register when triggered by a command pulse from the device selector. Such gates are called device input gates.

- c. Each device supplying input data to the computer must contain gating circuits at the output of the transmitting register capable of strobing the information from the output register to the I/O bus, and furnishing a read request (RD RQ) level to the computer when triggered by a command pulse from the DS. Such gates are called device output gates.

- d. Each device many contain a BUSY/DONE flag (flip-flop) and gating circuits that can supply a signal to the computer input/output skip bus upon command from the DS. The flag is set to indicate that the device is ready to transfer another byte of information.

Since the I/O bus is bidirectional, a signal called RD RQ must be supplied by the device to inform the computer that the desired direction of the data transfer is from the device to the AC. If RD RQ is not present, the computer assumes an outgoing transfer (from the computer).

# 3.1.3 I/O Bus Transfer

3.1.3.1 Loading a Device Buffer From The AC – Loading a device buffer from the AC (Figure 3–2) is usually accomplished by but is not restricted to the following two steps. The first IOT clears the device buffer and the second IOT ORs the contents of the AC into the cleared buffer. For such a transfer, the details are as follows:

Figure 3–2 Reading and Writing on the PDP–9 and PDP–9/L I/O Buses

- a. Prior to the end of the first cycle the AC is placed onto the I/O bus. Note that in any output transfer, IOP1 must not be used to transfer the AC to an external register.

- b. IOT1 is generated in the Device Selector Module W109 and transmitted to all "clear" inputs of the flip-flops in the device buffer.

- c. IOT4 is generated in the W109 and applied to the DCD input gates of the device buffer. Note that the input to the DCD gates for each bit must be buffered from the I/O bus by Type W107 Emitter Followers.

- 3.1.3.2 Reading a Device Buffer into the AC Reading the content of a device buffer into the computer is accomplished in the following manner:

- a. IOT pulse 2 is generated in the device selector module which is jumpered to produce a  $1-\mu s$  pulse.

- b. This  $1-\mu s$  pulse is used to gate the device data buffer onto the I/O data bus.

- c. Simultaneously, a read request positive pulse is generated (by a B163) on the RD RQ line.

- d. The central processor receives the request signal and allows time for the data bus to settle completely.

- e. The I/O bus is strobed into the AC.

The output of the W109 is a 1-µs pulse, and is regarded by the I/O bus system as a level. Either pulse or level notation may be used, provided this definition is kept in mind. Often, designers have used the W103 module and W640 modules to generate the 1-µs pulse. This combination has since been replaced with the W109 module.

Since the I/O bus is ORed into the AC the read IOT instruction is usually microprogrammed to clear the AC prior to reading (i.e., MB14=1). I/O waveforms are shown.

# 3.1.4 Other I/O Bus Facilities Used in AC Transfers

3.1.4.1 Program Interrupt (PI) Facility - When computer time is at a premium, it is advantageous for the computer to perform other tasks rather than to wait in a skip loop for the peripheral to complete its operation. The program interrupt facility allows the computer program to enter a subroutine at device request in order to service it. If more than one device is tied to the PI, a series of skip tests must be made to identify the requesting device.

Figure 3–3 shows the device hardware required for PI. The device flag is connected to the PROG INT RQ line with a B163 module or equivalent. When an interrupt is recognized by the computer, it stops

execution of the main program, stores certain flags and the contents of the PC in memory location 000000. It then executes the instruction in location 000001, which should be a JMP to the skip subroutine. Interrupts occur only when the PI is enabled. The IOT instructions associated with the PI are:

IOF = 700002 /TURN OFF PI FACILITY ION = 700042 /TURN ON PI FACILITY

3.1.4.2 I/O Skip Facility - The skip subroutine referred to above must identify the interrupting device. The I/O skip facility performs this function in the following way (see Figure 3-3).

When the IOT1 pulse is used in an I/O skip instruction (example CLSF = IOT 0001 = 700001), it is gated with the device flag flip-flop through a diode gate and returned to the computer on the I/O skip request bus line. A positive pulse, 1 µs wide, is returned to the processor if the tested flag is a binary 1. The skip flip-flop in the processor is set, and the instruction following the IOT instruction in the program sequence is not executed -- it is skipped. The signal on the skip line is sampled 600 ns after IOP1 is issued. A B163 Diode Gate or equivalent must be used in the device, to gate the SKIP RQ onto the bus.

The following program sequence represents a single output transfer to a device.

LAC Y /LOAD AC WITH DATA

IOT SKIP /TEST DEVICE STATUS

Figure 3-3 Device Flag Hardware

JMP. -1 /TEST DEVICE UNTIL READY

IOT WRITE /TRANSMIT DATA TO DEVICE

An input transfer is represented by:

IOT SKIP /TEST DEVICE STATUS

JMP .- 1 /TEST UNTIL READY

IOT READ /READ DEVICE BUFFER

DAC Y /STORE AC IN Y

A skip subroutine might look like:

IOT SKIPD1/TEST DEVICE 1

JMP .+2 /DEVICE 1 NOT INTERRUPTING

JMS SUBD1 /GO TO DEVICE 2 SERVICE SUB-/ROUTINE

IOT SKIP D2 /TEST DEVICE 2

JMP .+2 /DEVICE 2 NOT INTERRUPTING

JMS SUB D2 /GO TO DEVICE 3 SERVICE SUB-/ROUTINE

3.1.4.3 Read Status Facility - The IOT instruction IORS = 700314 loads the AC with a word comprised of various device flags and control flip-flops. External devices with assigned status bits use the read

status level to gate their device flag onto the corresponding I/O bus line (Figure 3-3). The status word can be displayed in the REGISTER indicators by putting the console switch to status and stopping the computer. Figure 3-4 shows the bit positions associated with the commonly interfaced flags. The functions of the device flags normally interfaced to the IORS (input/output read status) facility are presented below.

Program Interrupt - a 1-bit indicates that the program interrupt control is enabled. A 0-bit indicates that it is disabled. The program interrupt control is automatically disabled upon granting of a program interrupt request.

Tape Reader - a 1-bit indicates that the reader was previously selected and has assembled a character in its buffer for transfer to the AC upon execution of a "read buffer" IOT instruction. This flag is also interfaced to the program interrupt control to request program interruption when the flag goes to the 1 state.

Tape Punch - a 1-bit indicates that the paper tape punch has punched a line of tape relating to the contents of the AC at the time of selection. The flag is also interfaced to the program interrupt control to request program interruption when the flag goes to the 1 state.

Teletype Keyboard - a 1-bit indicates that the key-board buffer has assembled a character code relating to a struck key. The flag is cleared when the assembled code is read into the AC by an IOT instruction. The flag is also interfaced to the program interrupt control to request program interruption when the flag goes to the 1 state.

Figure 3-4 IORS Word-Status Bit Assignment

Teletype Printer - a 1-bit indicates that the teleprinter is ready to accept a character code from the AC. The flag is cleared when the teleprinter buffer is loaded and it remains so until the action called by the code has been executed. The flag is then again set to 1. The flag is also interfaced to the program interrupt control to request program interruption when the flag goes to the 1 state.

Light Pen - a 1-bit indicates that the Type 370 Light Pen has detected the presence of illumination, normally a CRT-displayed point. The pen is equipped with a manually operated shutter which should be opened only when the pen is positioned on the face of the CRT display. The flag is also interfaced to the program interrupt control to request program interruption when the flag goes to the 1 state.

Real-Time Clock Overflow - a 1-bit indicates that the real-time clock counter (stored in memory location 000007 of bank 0) has overflowed; i.e., the initialized clock count (in 2's complement form) has been incremented to zero. The flag is also interfaced to the program interrupt control to request program interruption when the flag goes to the 1 state.

Real-Time Clock Enabled - a 1-bit indicates that the real time clock is enabled and incrementing the contents of location 00007 by one at the rate of 60 times per second (or 50 times per second for 50 Hz powered PDP-9 systems). A 0-bit indicates that the real time clock is disabled. The flag is not interfaced to the program interrupt control.

Tape Reader No Tape - a 1-bit indicates that the paper tape reader has detected a no-tape condition and has halted. In the case of a tape break, since the break may be skewed, approximately 12 lines of previously read tape is considered invalid data when the no-tape flag is detected going to a 1. Although this flag is not interfaced to the program interrupt control, it does force the tape reader flag to go to the 1 state and hence request program interruption for the no-tape condition. A program may make use of the no-tape flag by executing an IORS instruction and testing the AC contents prior to each selection of the reader. An alternate method calls for a program-interrupt accessed subroutine to execute the IORS instruction and check the states of the tape-reader and tape-reader-no-tape flags to determine which flag initiated the interruption. While the no-tape flag is a 1, the tape reader will not respond to IOT selection; i.e., the reader is inhibited from reading tape lines. Depressing the

FEED button on the tape reader after loading a tape for readin clears the no-tape flag.

Tape Punch No Tape - a 1-bit indicates that the supply of unpunched tape in the internal magazine has been exhausted except for approximately one inch. This length is adequate for punching several characters; it may be used also for splicing purposes. This flag does not request a program interruption. Users making use of this flag must include an execution of the IORS instruction and a test of the AC contents prior to each selection of the paper tape punch.

<u>DECtape</u> - a 1-bit indicates that the DECtape flag and/or the error flag (both contained in the TC02 DECtape control unit) are set. This flag is interfaced to the program interrupt control to request program interruption when the flag goes to the 1 state.

# 3.2 GENERAL USE OF IOP PULSES AND DEVICE SELECT CODES

The use of the three IOPs is summarized below:

IOP Pulse 1 - Normally used as an I/O skip instruction to test a device flag. May be used as a command pulse, such as to clear a register before loading it but not to initiate either load or read from a device.

IOP Pulse 2 - Usually used to transfer data from the device to the computer or to clear a register. May not be used to determine a skip condition. May be used to transfer data from computer to device.

IOP Pulse 4 - Usually used to transfer data from the computer to the device. May not be used to determine a skip condition or to effect transfer of data from a selected device to the processor.

It is important that the IOT device select codes are unique to each device. When designing a special system, the engineer will note which device codes are already taken by existing peripherals or options and which codes might be used by any future additions to his system. A summary of assigned codes is given in the User Handbook for the computer.

# 3.2.1 Timing Charts

Figure 3-5 and 3-6 are complete timing charts for non-API program controlled transfers in the PDP-9 and PDP-9/L. When applicable, all signals are measured at the computers.

# 3.3 PROGRAM CONTROLLED TRANSFERS USING THE API OPTION

The API option extends PDP-9 and PDP-9/L capabilities by providing servicing for as many as 28 I/O devices with minimum programming and maximum efficiency. Its priority structure permits high data-rate devices to interrupt the service routines of slower devices with a minimum of system "overhead." The option permits the device service routines to access directly from hardware-generated entry points, eliminating the need for time-consuming flag searches to identify the device that is causing the interrupt.

The option provides 32 unique channels, or entry points, for the device service routines, and 8 levels of priority. The four higher levels are for fast access to service routines in response to device-initi-

ated service requests. Each of these levels can be multiplexed to handle up to eight devices assigned an equal priority. The four lower levels are assigned to program-initiated software routines for transferring control to programs or subroutines on a priority basis. Four of the 32 channels are reserved for these software levels.

Each device interfaced to the API option specifies (sends) its "trap address" or unique service routine entry point to the processor when granted an API break by the processor. Core memory locations 40g through 77g are assigned as these entry points. JMS or JMS I instructions contained in these locations provide linkage to the actual service routines.

Of the 28 hardware channels, 3 are assigned internally to the paper tape reader, real-time clock, and optional power-failure detection system. The API interface logic for these devices is wholly contained within the I/O wing of the PDP-9.

Each API priority takes precedence over lower API priorities, program interrupts (PI facility, basic PDP-9), and the main program. The highest priority program segment interrupts lower priority program

Figure 3-5 PDP-9 Program Controlled Transfer Timing

Figure 3-6 PDP-9/L Program Controlled Transfer Timing

segments when activated. Above all of these in priority, the DMA, DCH, and RTC program segments hold highest priority.

The entire API system may be enabled or disabled by a single IOT instruction. With the exception of the paper-tape reader channel, it is not possible to enable or disable a single channel. For a detailed description of API logic in the PDP-9, refer to document number DEC-09-15AA-D.

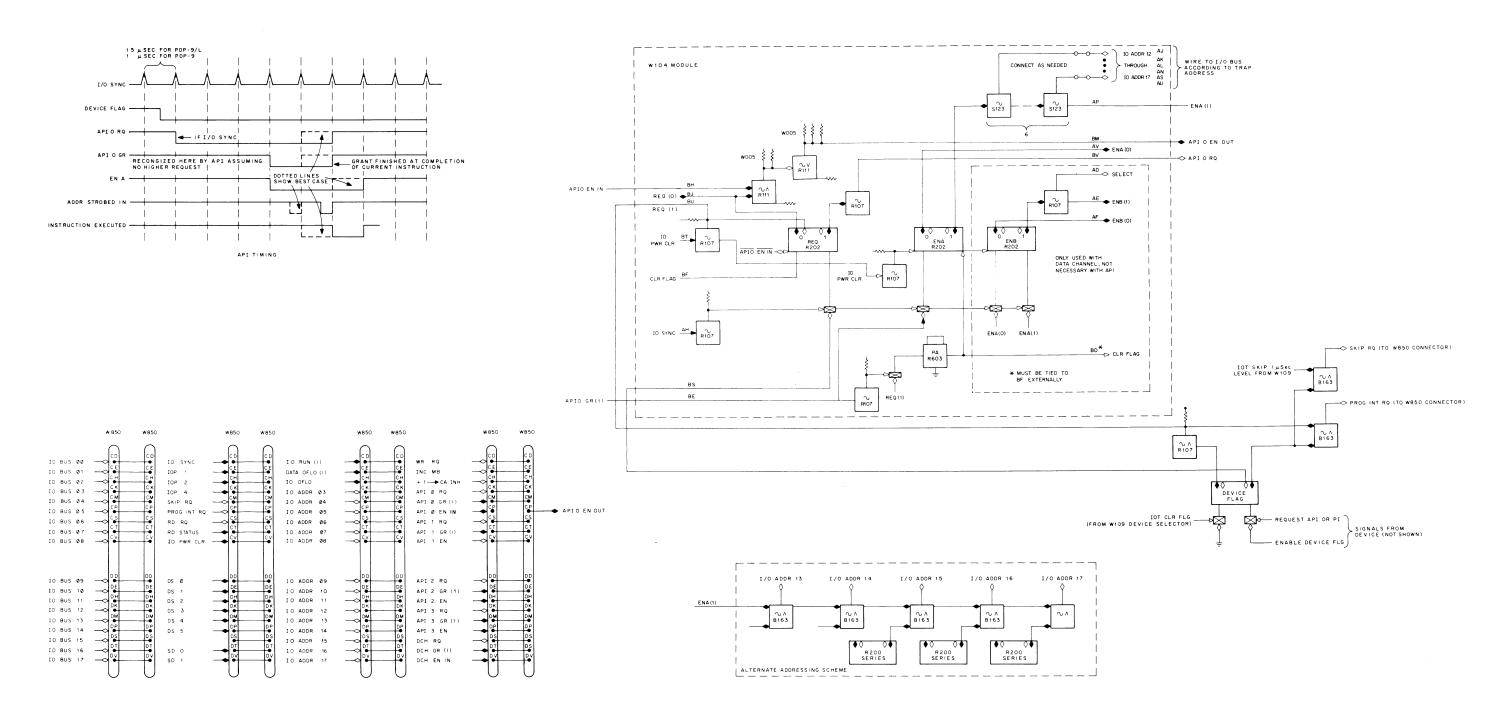

# 3.3.1 API Interface Logic

3.3.1.1 API I/O Bus Signals - The I/O bus contains 12 lines unique to the API; these include an API RQ (request), an API GR (1) (grant) and an API EN (enable) line for each of the four levels. Other I/O bus signals used by the API include I/O PWR CLR, I/O SYNC, and I/O ADDR 12-I/O ADDR 17. The API RQ lines are used by the device to request an interrupt from the computer at a particular priority level. The API GR is the computer's response to an API RQ. The API EN signal indicates to a device the status of another device on that interrupt level. (There can be as many as eight devices sharing any priority level.) I/O PWR CLR

is used to establish initial conditions, I/O SYNC is used for timing, and the I/O ADDR 12 to I/O ADDR 17 specify the unique entry point or trap address to a device service routine.

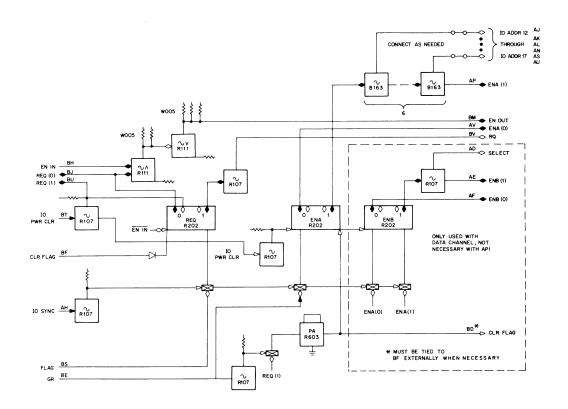

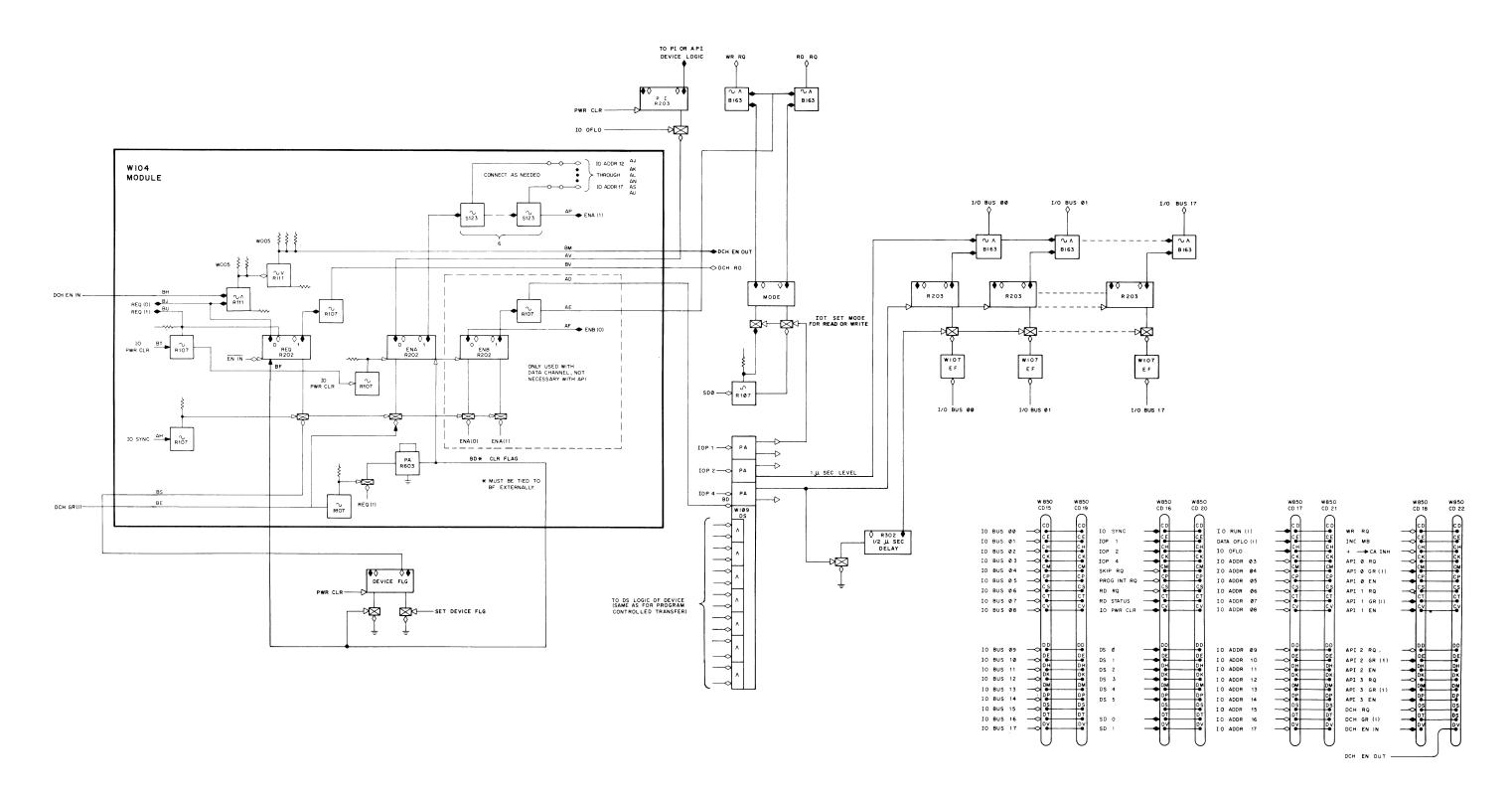

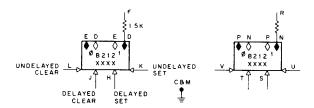

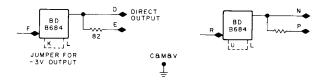

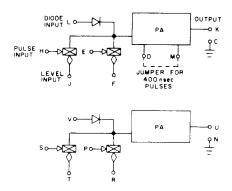

3.3.1.2 <u>The W104 Module</u> - DEC makes a double-height FLIP CHIP module, the W104, to handle much of the timing and hardware interface demands of the API. Its equivalent circuit is shown in Figure 3-7.

The W104 serves to establish priorities among devices tied to the same priority level; it also accepts the request for interrupt from the device and implements the necessary timing to place the trap address onto the I/O ADDR lines. The functions of the W104 signal and data lines are described below.

a. I/O Address Lines - Each W104 module contains six address selection lines (pins AJ, AK, AL, AN, AS, AU) which are normally connected to the I/O ADDR lines of the I/O bus to form the trap address. For a standard API device, pin AJ is connected to line 12 (40g) and pins AK-AU form the channel number. In some cases, trap addresses above 77g may be used, although standard PDP-9 peripherals should be restricted to 40g-77g. If a single device is required to generate a number of

Figure 3-7 Equivalent Circuit of the W104 Module

Figure 3-8 Using the API Facility of the PDP-9

different addresses on the basis of a single flag, the W104 can be used to gate the address from a flip-flop register onto the IO ADDR lines. Figure 3-9 shows an example of this.

b. RQ Lines - This signal requests an interrupt on level "N" and must be tied to API "N" RQ of the device I/O bus.

c. GR Lines - This signal is tied to the API "N" GR I/O bus signal. This is the computer's response to an API "N" RQ. It is used by the W104 to post the IO ADDR levels and thus indicate its trap address to the computer. The trailing edge of GR generates the CLR FLAG pulse.

Figure 3–9 Interfacing a Single Flag Device to the API

d. EN IN Lines – When more than one device is tied to any API priority level, the API "N" EN incoming I/O bus signal (refer to Appendix A) is tied to the W104s EN IN line. The outgoing API "N" EN I/O bus signal is jumped to the EN OUT signal of the W104. Thus, if the device closest to the computer requests API on a certain level, its EN OUT signal will prevent all other devices on the same API level from requesting an interrupt.

3.3.1.3 <u>Use of the W104 Module in a Device</u> - Two examples showing the use of the W104 module are presented below. The first deals with a single-flag device while the second explains multiple-flag devices.

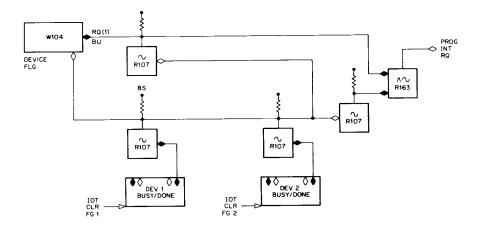

a. Single Flag Devices - The device using API connects to the W104 inputs called FLAG, REQ(1), and ENA(1). The other W104 signals usually go to the I/O bus or are not used. Figure 3-9 shows how a device flag is tied to the API lines of the I/O bus through the W104. In this case, API channel 0 is used. Note that the signal API 0 EN, usually jumpered between in-going and out-going cables, is cut and two new signals created; API 0 EN IN at the incoming cable and API 0 EN OUT at the outgoing cable. This was not done for API 1 EN to API 3 EN. Note also, that it is necessary that the PI facility operate when either API is shut off or when the W104 module is not plugged in (for this reason, PI logic is also shown in Figure 3–9). The circuitry-shown in Figure 3-9 operates in the following way.

The DEVICE FLAG is set by some device state change, enabling the RQ flop of the W104. The next I/O SYNC pulse issued by the computer after a 400 ns delay will set RQ, which then posts API 0 RQ. The computer, some time later, issues API 0 GR(1) which sets ENA(1). ENA(1) places the trap address onto the IO ADDR lines (in one of the two configurations shown) and the computer executes the instruction of the specified address. The next I/O SYNC pulse after API GR(1) clears ENA. An IOT instruction clears the device flag and thus RQ of the W104. While the RQ flip-flop is set, API 0 EN OUT goes to ground. This signal is passed onto the next device as API 0 EN IN. At ground, it will prevent the next device's RQ flag and any others down the line from setting. A PROG INT RQ will be raised simultaneously with the API RQ. However, API takes priority and the PI will be ignored. If the API is disabled, however, the PI will be raised instead. Removing the W104 module from the configuration (remembering to jumper the API 0 EN I/O cable lines together) leaves the device PI facility intact.

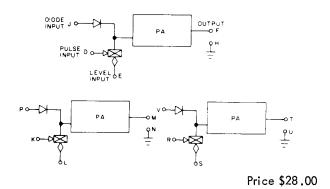

b. Multiple Flag Devices- The hardware shown in Figure 3-10 allows multiple flags to use API and PI facilties similar to the way shown in Figure 3-9. Note that when the last flag is cleared, the request flag of the W104 is cleared.

Each device interfaced to the automatic priority interrupt system must specify its "trap address" or unique entry point to its service routine. Locations 408-778 are reserved at these service routine entry

Figure 3-10 Multiple Flags Device Using Both API and PI Facilities

points. Trap addresses and channel numbers are related as follows:

$(\mathsf{TRAP}\ \mathsf{ADDRESS})_8 = (\mathsf{CHANNEL}\ \mathsf{NUMBER})_8 + (40)_8$

Locations  $40_8$ -77g should contain JMS or JMSI instructions to provide linkage to the actual service routine.

Table 3-1 shows the relationship between channel number and trap address, the channel assignments for standard PDP-9 I/O devices, and their suggested priority levels. All devices listed in Table 3-1 are connected to the API as shown. The channel number-assignments should remain fixed for software

compatibility but priority levels may be changed at the user's option.

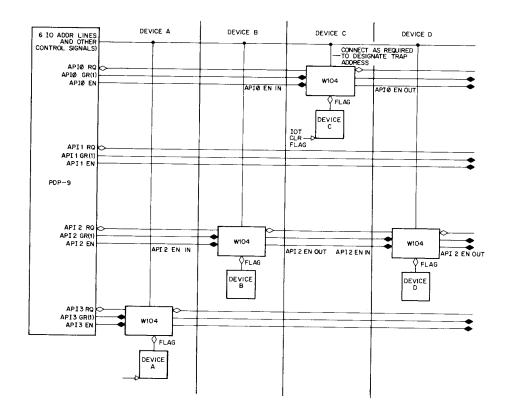

Figure 3-11 shows an example of four devices tied to the API (only API-related lines are shown). In this example, the following relationship exists between device number and priority level.

| Device | Priority Level |

|--------|----------------|

| Α      | 3              |

| В      | 2              |

| С      | 0              |

| D      | 2              |

Table 3-1

Channel and Priority Assignments

| Channel Number (Octal)  0 1 2 3 4 5 6 7 10 11 12 13 14 15 17                     | Trap<br>Address                                                                                                                                                      | Standard Device                                                                                                                                                                                                                                                                                                                                          | Suggested         |                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>10<br>11<br>12<br>13<br>14                    |                                                                                                                                                                      | Statidard Device                                                                                                                                                                                                                                                                                                                                         | Priority<br>Level | IO ADDR<br>Bits 12-17                                                                                                                                                                                                                          |