Gepufferter DMA- und IM2-fähiger ECB-Bus für GENIE I und II

Helmut BernhardtWährend bei Verzicht auf DMA- und IM2-Fähigkeit die Steuerung des Datenbuffers zwischen Computer und externem ECB-Bus relativ einfach zu realisieren ist (der Buffer darf nur in Richtung CPU treiben, wenn Daten von Baugruppen gelesen werden, die nicht auf der CPU-Seite des Buffers - also auf dem ECB-Bus - sitzen), sind bei der Einbindung dieser Features einige zusätzliche Aspekte zu berücksichtigen.

Der Interrupt-Mode2 der Z80-CPU setzt voraus, daß der Interrupt-Lieferant beim Interrupt-Acknowledge (M1* und IORQ* beide low) ein 8Bit-Wort auf den Datenbus legt, das die CPU als LSB einer Adresse in der Interrupt-Vektor- Tabelle interpretiert. Dieses Byte muß von einer Interrupt-Quelle vom ECB-Bus durch den Datenbuffer auch zur CPU gelangen. Der Buffer muß beim Interrupt-Acknowledge also auch in Richtung CPU treiben.

Bei Übernahme der Daten-, Adreß- und Steuerbusse durch einen DMA-Controller (DMAC) auf dem ECB-Bus muß dieser auch Zugriff auf RAM, EPROM und alle CPU-seitig des Buffers liegenden Baugruppen haben, für Adreß- und Steuerleitungen gestaltet sich diese Richtungssteuerung recht einfach. Hier genügt es, wenn durch das low aktive CPU-Signal BUSAK* (nur dann darf der DMAC arbeiten) die Buffer dieser Signale in Richtung zur CPU treiben, so daß der DMAC dort entsprechend adressieren kann. Für die Steuerung des Datenbuffers sind noch weitere Umstände zu berücksichtigen.

Wenn die CPU den Bus kontrolliert, kann beim Schreiben der Buffer immer in Richtung ECB-Bus treiben. Beim Lesen darf er nur dann nicht in Richtung CPU treiben, wenn interne Baugruppen (CPU-seitig des Buffers) adressiert werden, sonst würde ein von außen gelesenes FFH gegen ein von der intern adressierten Baugruppe ausgegebenes Datenwort arbeiten. Abgesehen davon, daß die gegeneinander arbeitenden Komponenten sich irgendwann gegenseitig zerstören, würde die CPU Fehlinformationen lesen.

Wenn der DMAC <4,5> den Bus steuert, ist Lesen und Schreiben für die Treiberrichtung des Buffers das ganze Gegenteil. Wenn der DMAC Daten einer CPU-seitigen Systemkomponente liest, wobei er dann auch die Leitung RD* low zieht, muß der Buffer in Richtung ECB-Bus treiben. Das darf er aber nur dann, wenn er auf CPU-seitige Komponenten zugreift. Wenn er von einer Baugruppe auf dem ECB-Bus liest, muß der Buffer in Richtung CPU treiben, um dann nicht auf dem ECB-Bus zwei Datenwörter gegeneinander arbeiten zu lassen.

Für die Treiberrichtung des Buffers muß also berücksichtigt werden, ob der DMAC oder die CPU den Bus kontrolliert, ob die adressierte Baugruppe auf dem ECB-Bus oder CPU-seitig des Buffers liegt und ob gelesen oder geschrieben wird.

|

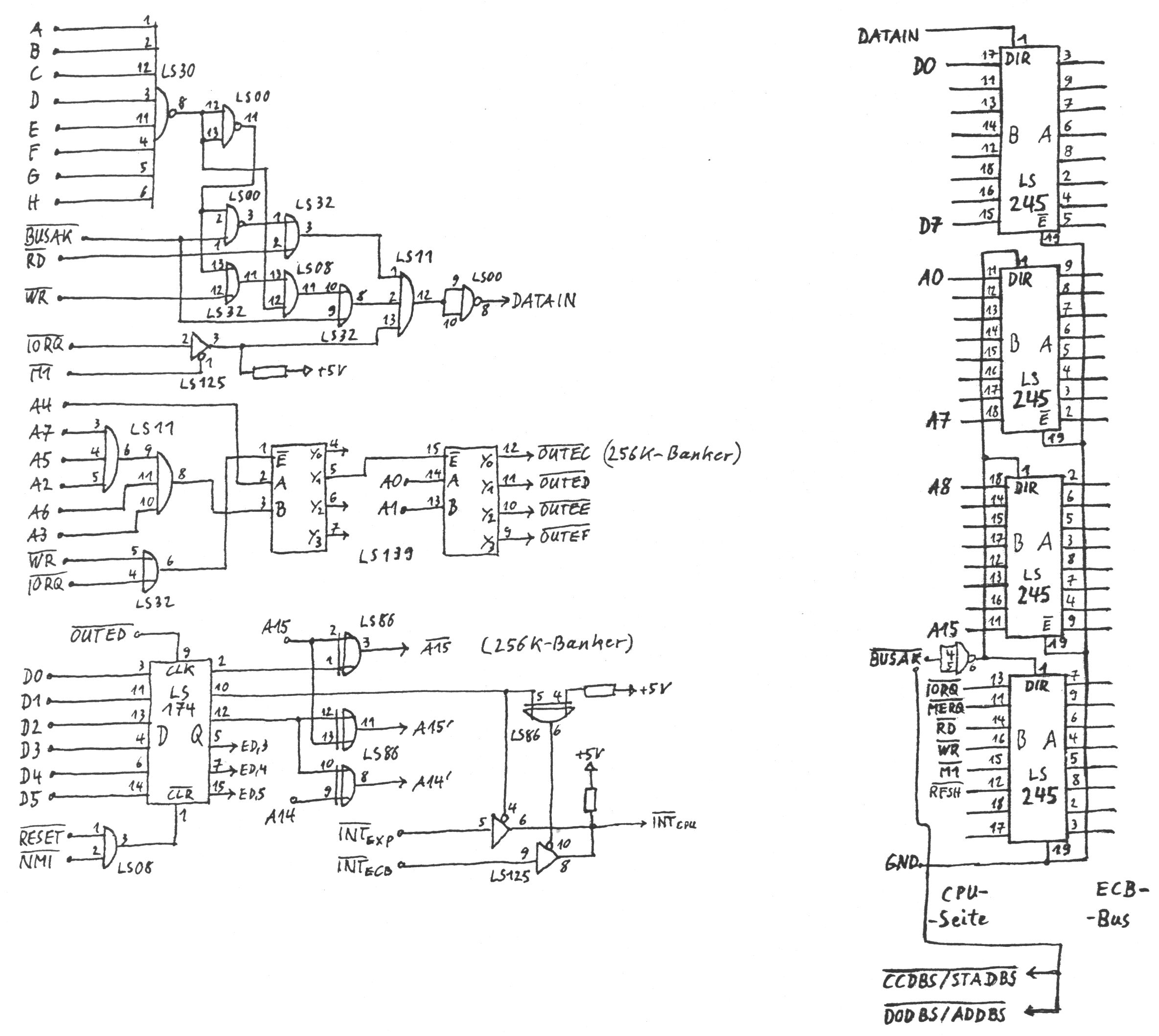

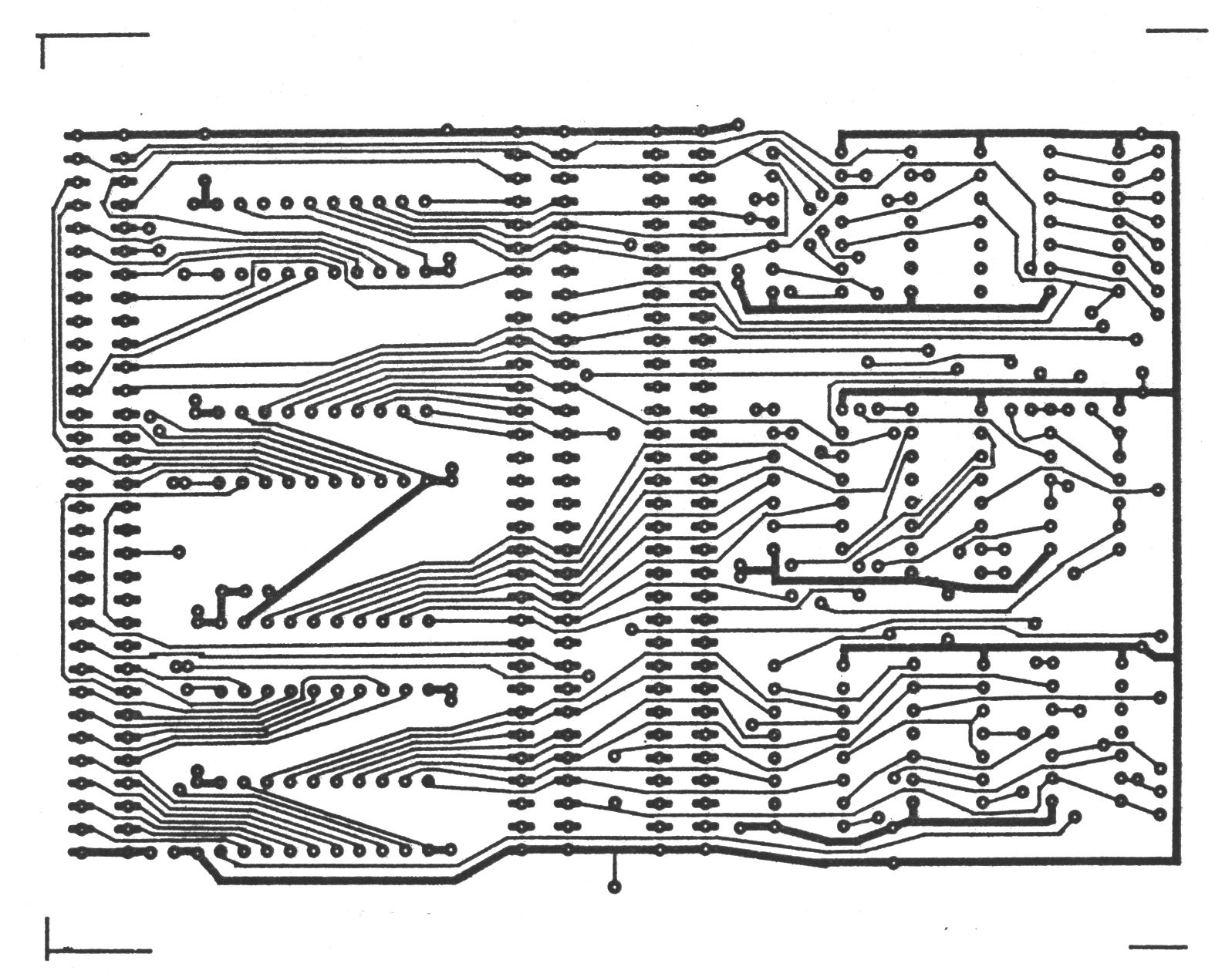

Abb.1) Steuerung des Databuffers, Portdecodierung, programmierbares Invertieren von A15 sowie A14 UND, A15 Umschalten der Interrupts |

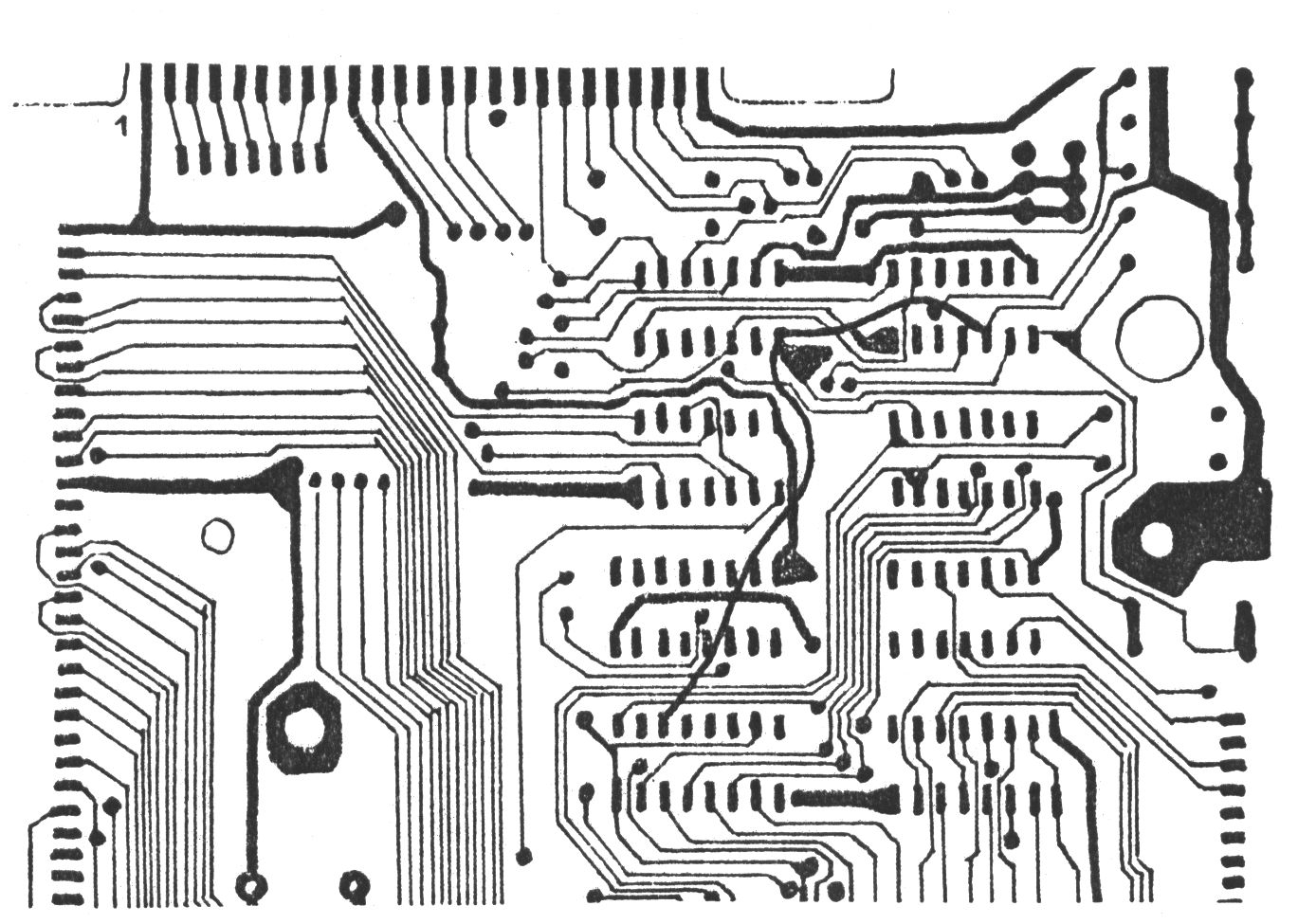

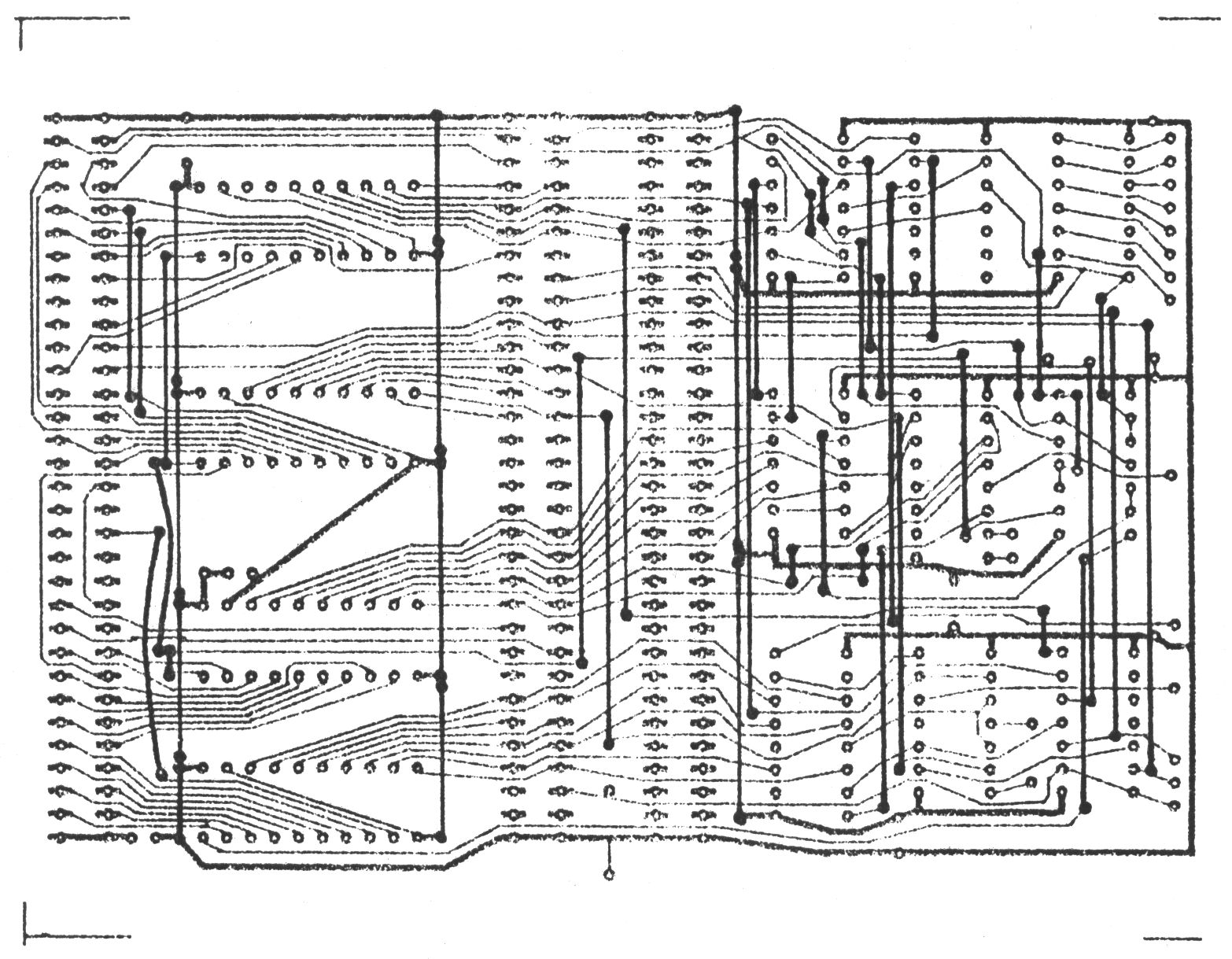

Abb.2) Pufferung des ECB-Bus |

In Tabelle 1 sind die für verschiedene Betriebszustände aus obigen Überlegungen abgeleiteten Treiberrichungen (von der CPU aus gesehen) zusammengestellt. Dabei ist zu berücksichtigen, daß zusätzlich auch noch beim Interrupt-Acknowledge die Richtung "rein" sein muß, weil der GENIE keine eigenen vektorisierten INT-Quellen hat. Diese Tabelle ist Grundlage der Schaltung in Abb.1. Die Richtungssteuerung soll ausschlielich aus Signalen, die von CPU-seitigen Baugruppen zu beziehen sind, erfolgen. Nur dann ist auch gewährleistet, daß auf dem ECB-Bus jede handelsübliche Karte funktioniert. Kommerzielle ECB-Bus-Karten legen ein aktives Signal auf den Bus, das in die Buffersteuerung einbezogen werden kann.

Tabelle 1: Treiberrichtung des ECB-Bus BuffersBus- interne Baugruppe externe Baugruppe Steuerung adressiert adressiert durch Read Write Read Write --------------------------------------------------------- CPU raus raus rein raus DMAC raus rein rein rein

Der Auwand dafür ist aber nicht unerheblich und der Anwender dieser Bussteuerung muß sein System genau kennen, um die nötigen Steuersignale an die Schaltung legen zu können. Einen Anhaltspunkt dafür, welche Freigabesignale vorkommen können, mag die Tabelle 2 geben. Darin sind die prinzipiell vorhandenen Baugruppen und einige häufig benutzte Hardware-Erweiterungen und die Punkte, wo deren Freigabesignale abzugreifen sind, zusammengestellt. Diese Punkte sind mit jeweils einem der Punkte A bis H auf der Eingangskarte zu verbinden.

Tabelle 2: Interne FeigabesignaleCPU-Board Adresse IC Typ Pin RAM 4000-FFFF 37 37 15 (3900-3BFF) <7> ROM1 0000-0FFF 10 3001 20 ROM2 1000-1FFF 11 3002 20 ROM3 2000-2FFF 12 3003 20 ROM4 3000-36FF(37FF) <7> 13 2716 20 Tastatur 3800-3BFF(38FF) <7> 7 368 1 Video-RAM 3C00-3FFF 35 32 3 Video-Board Cassette 1 Port FF 20 32 11 Cassette 2 Port FE bleibt unberücksichtigt #1 Expansion-Interace EG3014 RAM1 8000-BFFF 37 20 10 RAM2 C000-FFFF 37 20 9 Floppy 37E0-37FF 29 139 12 Drucker 37E8 u.Port FD 31 156 9 RS 232 EG3020 Ports F8-F9 37 20 10 EXP1 von RB 37E0-37FF 18 155 2,14 Port FD 14 32 3 RB V24 Ports 80-88 Z80-CTC 16 Z80-DART 35 HRG1B von RB Ports 00-7F ? 155 2,14 Schmidte 80Z.Karte B000-BFFF ? 245 1 Ports D0-D1 ? 138 15 EG64MBA Port DF bleibt unberücksichtigt #1 EG64MBA+ <6> Ports DE-DF " " 256K-Banker <10> Port EC " " (u. ED mit dieser Karte) " " CP/M-Banker <6> Ports 50-5F " "

#1 diese Baugruppen werden nicht gelesen und brauchen deshalb nicht in die Buffersteuerung mit einbezogen zu werden, das IN A(0DFH) des EG64MBA dient nicht der Datenaquisition, es setzt nur das 79LS259-Latch zurück, ein Datenwort wird nicht ausgegeben.

Im Normalfall liegen alle memory-mapped (mm) Baugruppen CPU-seitig des Treibers, so daß dann einzig MERQ* (IC3, 74LS367, Pin5) an die Schaltung geführt werden muß. Wenn aber auch nur eine mm Baugruppe auf dem ECB-Bus steckt, müssen alle anderen mm Freigabesignale einzeln an die Schaltung geführt werden.

Durch Vorschalten weiterer AND-Gatter vor die Eingänge des 74LS30-ICs (z.B. 74LS08, 74LS11, 74LS21) kann die Anzahl der verwendbaren Eingänge für Freigabesignale beliebig erhöht werden (Abb.1).

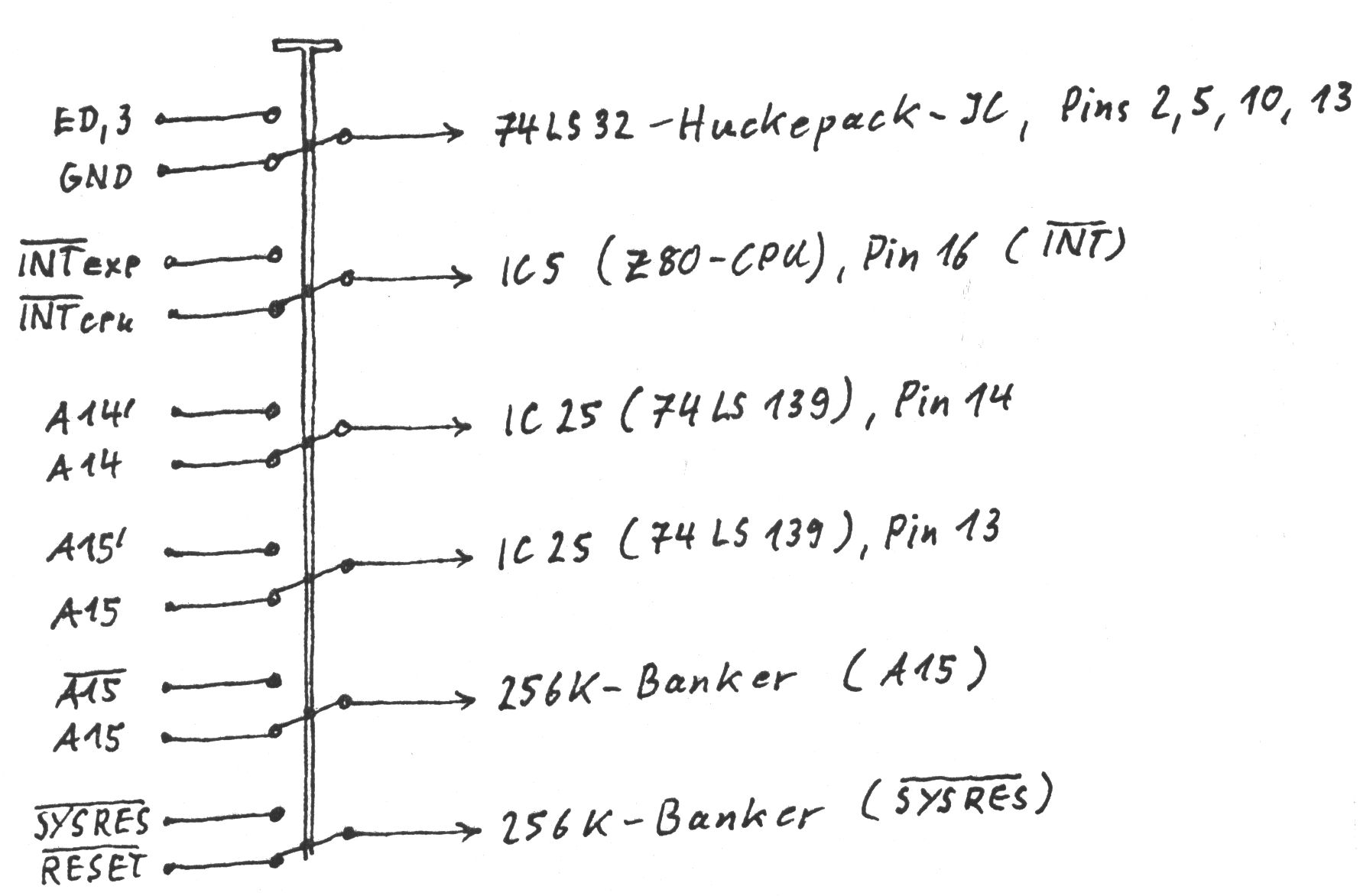

Abb.8) Verbinden von BUSAK* mit CCDBS/STADBS* und DODBS/ADDBS*

Abb.8) Verbinden von BUSAK* mit CCDBS/STADBS* und DODBS/ADDBS*Die DMA-Fähigkeit der ECB-Busbuffer alleine reicht nicht aus. Es muß durch Verbinden der Systembus-Leitung BUSAK* mit CCDBS/STADBS* und DODBS/ADDBS* auch dafür gesorgt werden, daß beim DMA-Zugriff die Buffer der CPU-Signale in den hochohmigen Zustand versetzt werden. Das kann entweder auf der Eingangskarte durch Querverdrahtung der entsprechenden Pins von CN2 bzw, CN3 oder durch feste Verdrahtung auf dem CPU-Board gemäß Abb.8 erreicht werden.

Da für die Richtungssteuerung des Datenbuffers ohnehin einige ICs nötig waren, und der ECB-Bus auch IM2-fähig ist, ließ sich mit etwas Mehraufwand auch gleich eine Vektorisierung der Interrupts des 25ms-Timers und des Floppy-Controllers realisieren. Dafür ist Voraussetzung, daß auf dem ECB-Bus auf einer Karte ein freier Z80-CTC-Kanal (2) vorhanden ist, über den durch Software das gemeinsame INT*-Signal des Systems umgeleitet werden kann. Der CTC-Kanal ist dann im Zähler-Modus mit der Zählkonstanten 1 und Triggern durch eine negative Flanke zu programmieren.

Die direkte Verbindung des INT*-Signals (im Schaltplan INTEXP*) von der Floppy-Baugruppe zur CPU ist dafür aufzutrennen. Das Signal INTEXP* ist stattdessen an den entsprechend bezeichneten Punkt der Schaltung und an den freien Triggereingang des CTC-Kanals zu legen. Die INT*-Leitung des ECB-Bus ist an den Punkt INTECB* zu legen und der Ausgang INTCPU* ist mit dem INT- Einang der CPU (Z80, Pin3) zu verbinden.

Damit ist gewährleistet, daß nach dem Einschalten oder Drücken des RESET- Knopfes immer der Interrupt vom FDC-Board direkt zur CPU durchgeschaltet wird und das Betriebssstem im IM1 arbeiten kann. Wenn allerdings andere Baugruppen auf dem ECB-Bus in Echtzeit im IM2 betrieben werden sollen, müssen auch die systemeigenen Interrupts dieses Spiel mitmachen können und das geht nur dann, wenn ihnen der CTC-Kanal beim INT-Acknowledge einen Vektor zur Verfügung stellt. Die Schaltung leistet es, daß ein LD A, xxxxxx1xB; OUT (0EDH),A das INT* Signal des FDC-Boards über den CTC umleitet.

Die Software muß dann aber Rücksicht auf diesen Umstand nehmen. In der INT- Vektor-Tabelle darf nicht einfach 40F2H stehen (INT-Vektor des DOS), da die Serviceroutine des DOS nicht mit RETI sondern mit RET endet und der Z80-CTC dann nicht weiß, wann er seinen IEO-Ausgang wieder auf High zurücknehmen soll. Es muß folgender Umweg eingeschlagen werden.

INTAB DEFW SERV1 ;Anfang INT-Tabelle DEFW SERV2 ;nächster Vektor DEFW .... ;u.s.w. .... .... DEFW CTCN ;Vektor für Serviceroutine des INT vom CTC-Kanal .... ;N, über den die System-Interrupts laufen DEFW LETZT ;Ende der Vetortabelle CTCN CALL 4032H ;Serviceroutine des D0S EI RETI

Außerdem bleibt es dem Anwender offen, während des IM2-Betriebes anderer Baugruppen den 25ms INT verhungern zu lassen. Wenn beim Lable CTCN einfach ein EI, RETI steht, wird 37E0H nicht mehr gelesen und darauhin erfolgt kein weiterer Interrupt des Timers mehr. Eine Reinitialisierung des Timer-INTs geschieht durch Umprogrammieren des Vektors auf ein anderes Lable, das wieder den CALL 4012H enthält, und einmaliges Lesen von 37E0H.

Durch Zurücksetzen von D1 in Port E0H wird wieder der INT des FDC-Boards direkt an die CPU durchgeschaltet und alle Interrupts des ECB-Bus werden unterbunden.

Mit der für die Interrupt-Steuerung benötigten Portdecodierung und mit dem Latch wurden noch einige zusätzliche Funktionen realisiert. Zunächst wurden auch die Portfreigabesignale OUTECH*, OUTEEH* und OUTEFH* hergeleitet. Davon kann OUTECH* zur Freigabe des 74LS273 Latch auf dem 256K-Banker <10> be- nutzt werden. Dieses Signal wird direkt an den Pin11 des 74LS273 geführt, wobei dann aber die bisher dahin führende Leitung zu durchtrennen ist. Damit ist dann das 74LS30 IC auf dem Banker überflüssig und auch die Leitungen A0 bis A5 sowie IORQ* und WR* brauchen nicht mehr dorthin geführt zu werden (A6 und A7 werden dort nicht nur zur Portdecodierung sondern auch noch zur Erzeugung der 8Bit-Refreshadresse benötigt und müssen deshalb weiterhin angeschlossen bleiben).

Mit Bit 0 in Port EDH wurde ein softgesteuertes Invertieren des zum 256K-Banker führenden Signals A15 realisiert. Damit läßt sich mit D0=0 an Port EDH (Einschaltzustand) vorgeben, daß die unteren 32K Adreßbereich des Z80 gebankt werden können, während D0=1 an Port EDH das Banking der oberen 32K festlegt.

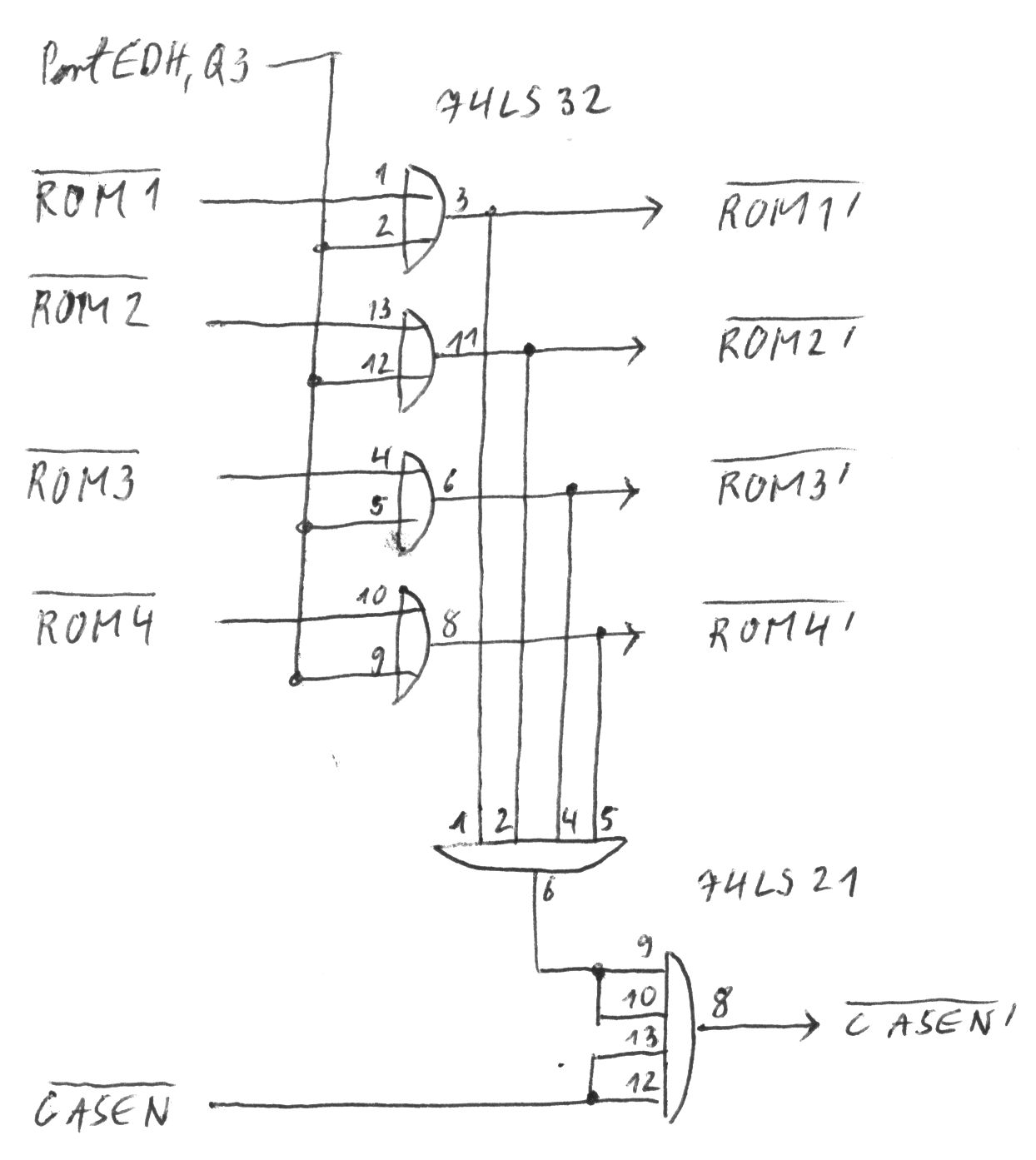

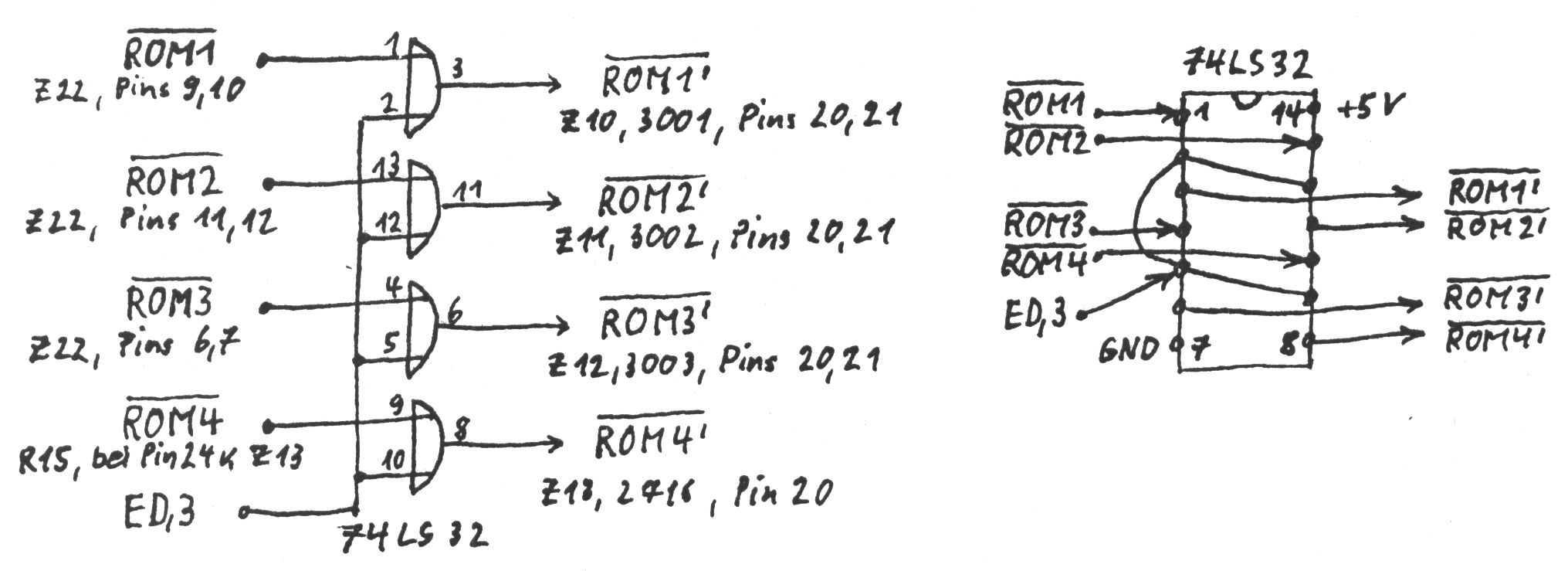

Und schließlich kann mit D2=1 an Port EDH ein gemeinsames Invertieren der Adressen A14 und A15 erreicht werden. Die dabei gewonnenen Signale A14' und A15' können anstelle der Signale A14 und A15 an die Decoderschaltung für die 16K (ROMs und mm I/O), IC25, 74LS139 Pins 14 und 13 geführt werden und ge- statten dadurch ein Verlegen dieser Komponenten an das obere Speicherende 48-64K. In diesem Bereich funktionieren dann zwar die ROMs nicht mehr, wenn man aber dann noch ein 74LS32 IC spendiert und mit dem Signal ED,3 (D3 von Port EDH) ein programmierbares Abschalten der ROMs einbaut (Abb.10), hat man auch noch die Funktionen des Omnicron Mappers (compatibler Selbstbau in <9>) für den Betrieb von CP/M realisiert. Dieser leistet (wenn auch mit einem anderen OUT-Befehl) ebenfalls das Einstellen der Systemkonfiguration.

Abb.10) programmierbares Abschalten der ROMs

|

0000H-F7DFH RAM <7<> #1

F7E0H-F7FFH Floppy, Drucker

F800H-FBFFH Tastatur (7)

FC00H-FFFFH Video-RAM

#1 der Omnicron Mapper für den TRS 80

leistet selbst eine vollständige

Decodierung des Bereichs des

Sonder-ROMs des GENIE

|

Ein Patchen der CP/M Systemdisette ist sehr einfach. Auf den Systemspuren läßt sich relativ einfach die Sprungleiste des Loader BIOS finden, die aus einer Reihe von Jumps besteht (C9 nn nn C9 nn....). Daran schließen sich die Disk Parameter Tabellen mit sehr vielen 00H an und unmittelbar danach stehen die Befehle LD A,40H; OUT (50H),A. Diese beiden Befehle sind durch die Befehle LD A,xxxx 11xxB; OUT (0EDH),A zu ersetzen. Damit läuft das CP/M des Omnicron Mappers dann auch ohne denselben.

Wenn diese Eingriffe auf dem CPU-Board gemacht werden, ist der Computer aber von der ECB-Bus-Eingangskarte abhängig, weil von dieser dann lebenswichtige Signale geliefert werden. Der ECB-Bus braucht selbst nicht angeschlossen zu sein.

Abb.9) Umschalter zwischen ursprünglichen Signalen des CPU-Boards und oder Steuersignale der ECB Eingangskarte"

Von dieser Abhängigkeit kann man sich durch einen Mehrfach- (oder mehrere Wenigfach-) Umschalter lösen. Abb.9 zeigt, wie man damit entweder die ursprünglichen Signale des CPU-Boards oder die steuerbaren Signale dieser Schaltung an die entsprechenden Stellen des CPU-Boards führt, und damit das Gerät entweder wie bislang ohne ECB-Eingangskarte oder mit derselben und allen ihren Mehrleistungen laufen lassen kann.

Um den Umfang der (zusätzlich zu denen des Systembus) an die Eingangskarte geführten Leitungen etwas zu reduzieren, bietet es sich an, IC7, 74LS30 auf der Eingangsarte nicht zu bestücken und dieses IC im Computer an geeigneter Stelle huckepack mit den Pins 7 und 14 auf ein anderes Dil14 IC zu löten und die internen Freigabesignale fest dorthin zu verlegen (Pins 1-6, 11-12). Dann braucht nur noch das Signal INTERN von Pin8 des 74LS30 an die Eingangskarte (CN2 Pin25c) geführt zu werden.

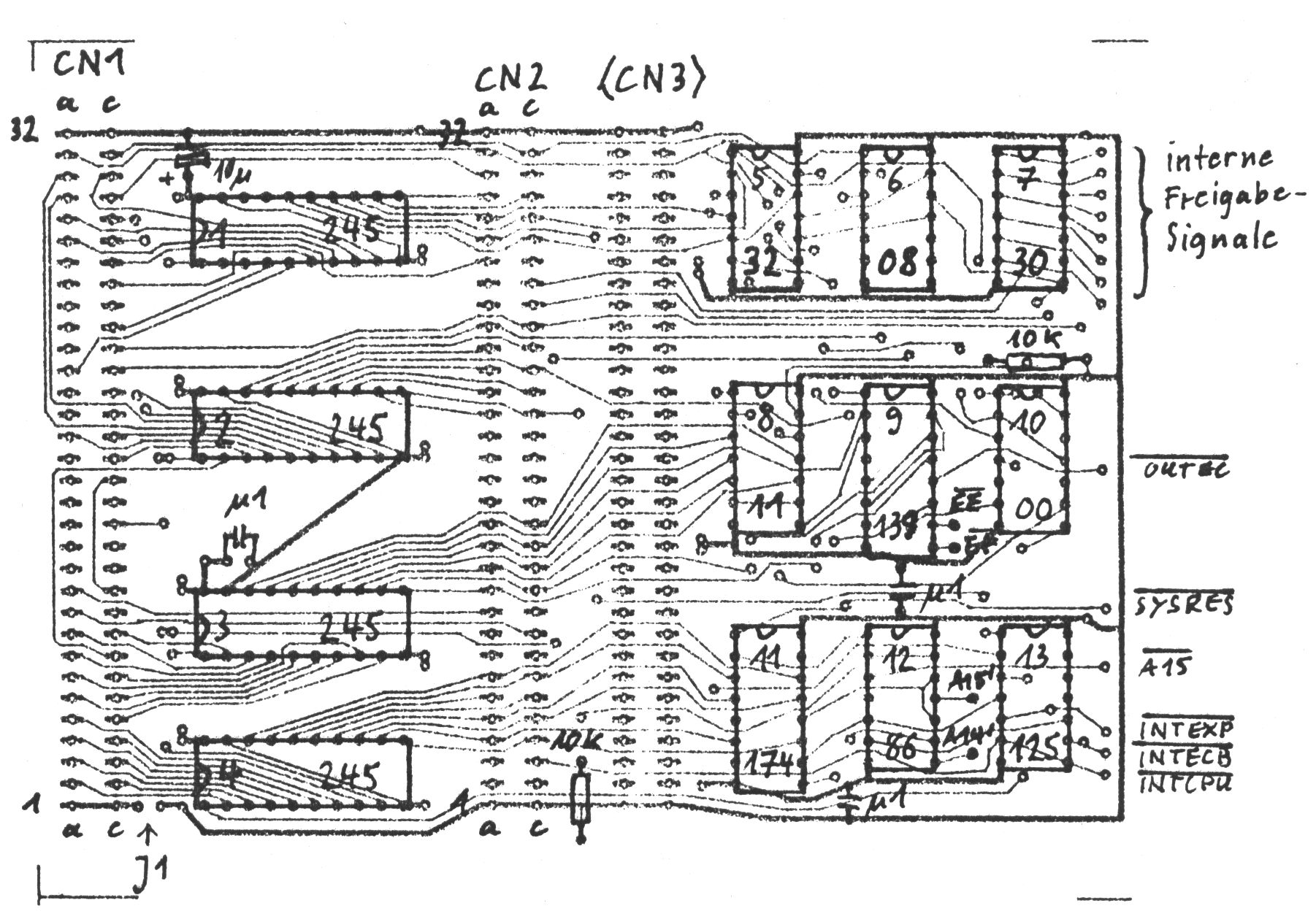

Abb.3) Layout der Eingangskarte

Abb.3) Layout der EingangskarteWenn die zusäztlichen Features der Eingangskarte voll genutzt werden sollen, können alle benötigten Signale (SYSRES* A15* A14' A15' ED,3 OUTECH*) über freie Verdrahtung an unbelegte Pins von CN2 gelötet werden. Im Layout sind nur die Sinale INTCPU* INTEXP* INTECB* und INTERN über CN2 geführt, Dadurch können alle Verbindungen mit dem Computer (nicht nur der Systembus) über CN2 laufen.

Abb.4) Drahtbrückenplan Bestückungsseite

Abb.4) Drahtbrückenplan BestückungsseiteWer diese Variante des ECB-Bus bauen möchte, kann bei mir für 10 DM (incl. Rückporto) eine geätzte aber ungebohrte Karte im Europaformat bekommen. Sollte irgendjemand die Karte am Komtek 1 betreiben wollen, kann ich entsprechende Informationen zur Verfügung stellen, die eine Nutzung auch dort ermöglichen. Der Anschluß an den TRS 80 ist nicht ohne Sondermaßnahmen möglich, weil die internen Datentreiber IM2-Betrieb verhindern. Ein Hard- ware-Patch der dagegen hilft, ist in <8> beschrieben. Eine Herleitung der Signale IORQ* MERQ* RD* und WR* aus den daraus gewonnenen Signalen IN* OUT* MWR* und MRD* des TRS 80 Systembus mit Gattern erzeugt Signale mit nicht ganz richtigem Timing, die eventuell Schwiedigkeiten bereiten können; hier ist das Abgreifen der originalen Signale eine bessere Lösung.

Aufbau und Anschließen der Karte

Entgegen der üblichen Technik, solche Karten doppelseitig geätzt zu entwerfen, wurde hier ein einseitiges Layout mit einer unverschämten Menge Drahtbrücken bevorzugt, was das Durchkontaktieren an IC-Sockel-Pins vermeidet. Damit wird beim Aufbau aber viel Fummelei und beim Testen viel Ärger erspart.

Abb.5) Bestückungsplan, J1 ist nur dann zu legen, wenn im GENIE ein stärkrtre Netzteil eingebaut wurde, das den ECB-Bus mitversorgen soll.

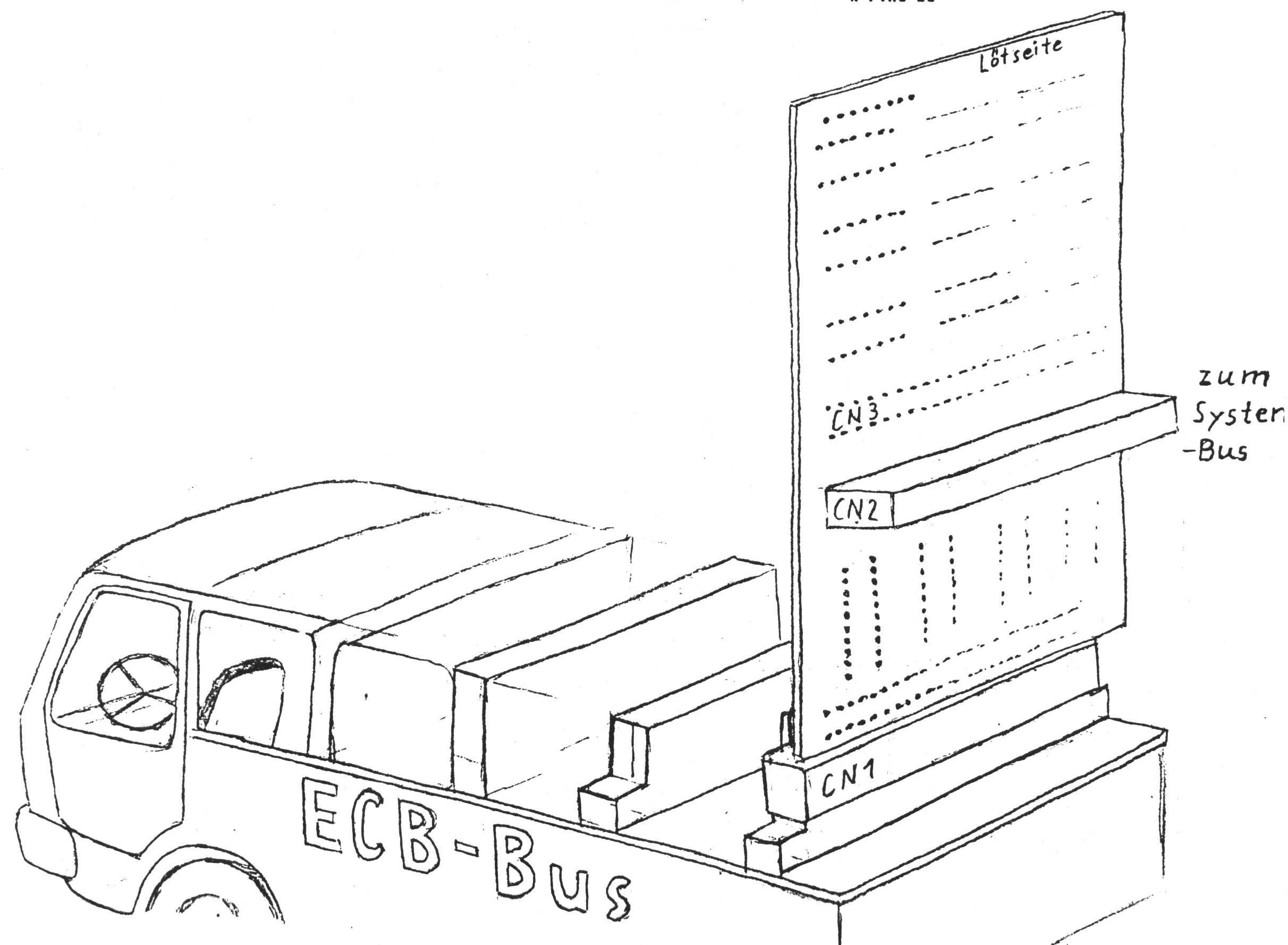

Der Stecker CN1 (VG64, ac, Stifte, gewinkelt) wird auf den ECB-Bus gesteckt. Für den Anschluß an den Systembus wurden 2 Varianten vorgesehen. Durch Einbau einer VG64 a,c-Buchsen- leiste bei CN2 von der Lötseite (Abb.7) muß durch einen entsprechenden Drahtverhau zum Gegenstück für den 50poligen Platinenrandstecker des CPU-Boards die Anordnung der Signale umsortiert werden. Wer allerdings ein ästhetisches 50poliges Flachkabel bevorzugt, kann CN2 unbestückt lassen und stattdessen in die nicht angeschlossenen Lötaugen von CN3 von der Lötseite einen geeigneten 50poligen Stecker einlöten. Dann wird aber der zum Umsortieren der Signale nötige Drahtverhau nur auf die Karte zwischen CN2 und CN3 verlagert.

Außer den reinen Bus-Signalen des Computers müssen bei Bedarf auch noch die aktiven Steuersignale der Eingangsarte an den Computer zurückgeührt werden und die im Computer abzugreifenden Freigabesignale an die Eingangskarte geführt werden. Dafür sind am oberen Platinenrand entsprechende Lötpunte vorhanden. Die wichtigeren Signale sind aber auch an Lötpunte von CN2 geführt, womit dann alle Signale über CN2 (und bei entsprechender Querverdrahtung auch CN3) mit dem Computer verbunden werden können. Dafür reicht dann aber der 50polige Platinenrandstecker des CPU-Boards mit seinen 3 freien Pins nicht mehr aus. Da muß dann noch eine zusätliche fliegene Steckverbindung herhalten, die diese zusätzlichen Signale übergibt.

Steckerbelegungen Stückliste

CN1 (ECB-Bus) CN2 (vom Systembus)

Reihe a NR. Reihe c Reihe a Nr. Reihe c ICs;

--------------------- --------------------- 4 x 74LS245

GND 32 GND GND 32 GND 1 x 74LS174

BUSK* 31 RESET* BUSAk* 31 RESET* 1 x 74LS139

A9 30 MERQ* CLOCK 30 nc 1 x 74LS125

A13 29 CLOCK MERQ+ 29 RFSH* 1 x 74LS88

RFSH* 28 A15 IORQ* 28 RD* 1 x 74LS32

IORQ* 27 A12 M1* 27 WR* 1 x 74LS30

#1 26 #1 HALT* 26 nc 1 x 74LS11

#1 25 HALT* nc 25 INTERN 1 x 74LS08

#1 24 RD* nc 24 INTEXP* 1 x 74LS00

#1 23 #1 NMI* 23 INTECB*

-12V #2 22 WR* A11 22 A8 Widerstände;

01 21 INT* A10 21 A14 2 x 10k

M1* 20 INT A13 20 A9

#1 19 #1 A12 19 A15 Sonstiges;

A14 18 A10 nc 18 nc 1 x VG64 a,c Stifte

#1 17 A11 nc 17 nc gewinkelt

#1 16 IEO nc 16 nc 1 x VG64 a,c Buchsen

-5V 15 #1 nc 15 nc gerade

#1 14 D1 A7 14 A6 1 x Leiterplatte

+12V 13 #1 A5 13 A4 jede Menge Draht

#1 12 A14 A3 12 A2 viel Geduld

BUSRQ* 11 IEI A1 11 A0

WAIT* 10 #1 BUSRQ* 10 nc

A6 9 A7 nc 9 WAIT* ----------------------------------

A5 8 A8 nc 8 nc #1 diese Pins sind zum Teil nicht

A4 7 A1 D5 7 D0 belegt oder führen Signale die

A2 6 A3 D6 6 D7 hier nicht benutzt werden

D4 5 A0 D3 5 D2 #2 die Lage von -12V wird nicht

D3 4 D2 D4 4 D1 einheitlich gehandhabt, diese

D6 3 D7 nc 3 INTCPU* Spannung kann auch woanders

D5 2 D0 nc 2 nc liegen (muß bei jeder gekauften

+5V 1 +5V +5V I +5V Karte geprüft werden)

--------------------- --------------------- ----------------------------------

Literatur

<1> Verbindend - Der ECB-Bus / Johannes Assenbaum / c't 12/85, 60-61

<2> Z80 CTC - Einsatz und Progmmmierung / Rolf Keller / c't 4/85, 92-94

<3> Interrupt-Priority-Encoder und Vektorgenerator für IM2 mit dem Z80 CTC /

H. Bernhardt / Info des GENIE/TRS 80- User-Club Bremerhaven 32/85, 10-11

<4> Direkter Speicherzugriff; Schneller als die CPU - So arbeiten DMA-Con-

troller-ICs / Rolf Keller / c't 8/85 80-83

<5> Z80 DMA - Schnell, aber compliziert / Rolf Keller / c't 12/85, 76-79

<6> Hardware-Umschaltung für den Betrieb von CP/M bei den Computern TRS 80

GENIE I und II und Komtek 1 / H. Bernhardt / Info des GENIE/TRS 80-User-Club

Bremerhaven, Hardware-Sonderheft 11/85, 1-5

<7> GENIE I und II: Voll decodierter Sonder-ROM; RAM im Bereich 3900H bis

3BFFH / H. Bernhardt / Info des GENIE/TRS 80-User-Club Bremerhaven

11/85,...?

<8> Interrupt Your 80 - Without a Hardware Mod Your 80 is immune to rude

Interruptions / Douglas C. Fisher / 80 micro, January 1983, 258-266

<9> CP/M Hardware für TRS 80 GENIE I und II und Komtek 1 / H. Bernhardt,

C. Ueberschaar / Info des TRS 80/GENIE-User-Clubs Bremerhaven 02/86, 11-17

<10> 255K (1M-) RAM für Z80-Systeme / H. Bernhardt / Info des

TRS 80/GENIE-User-Clubs Bremerhaven 03/86, 5-10

Abb.6) Beschaltung des Huckepack 74LS32 auf dem CPU-Board zum Ausblenden der

ROMs

ROM1* Z22, 74LS156, Pins 9,10 ROM1'* Z10, 3001, Pins 20,21 ROM2* " " " 11,12 ROM2'* Z11, 3002, Pins 20,21 ROM3* " " " 6,7 ROM3'* Z12, 3003, Pins 20,21 ROM4* R15, Seite zu Pin24 von Z13 (R4) ROM4'* Z13 2716, Pin 20 diese Signale sind an die aus der Fassung gebogenen Pins zu lȯtenAbb.7) Verbinden des ECB-Bus mit dem Systembus des Computers über die Eingangskarte

ECB-BUS Belegung (CONITEC-Norm)

ECB-BUS Belegung (CONITEC-Norm)

Reihe a b c Bedeutung: 1 +5U xxx +5U : +/-5V/12V: Betiebsspannungen 2 D5 xxx D0 : UBAT: Akku C+3,6 Volt 3 D6 xxx D7 : GND: Gemeinsame Masse 4 D3 xxx D2 : 5 D4 xxx A0 : DO-D7: 8-Bit-Datenbus 6 A2 xxx A3 : A0-A15: 16-Bit-Adressbus 7 A4 xxx A1 : A16-A19: 20-Bit-Adressen 8 A5 xxx A8 : A19/MS; MASTER/SLAVE-Signal 9 A6 xxx A7 : 10 /WAIT xxx xxx : /RD: Lesen 11 /BUSRQ xxx ...IEI : /WR: Schreiben 12 A18 ! xxx : A19/MS !: /MERQ: Speichezugiff 13 +12V xxx : xxx : /I0RQ: Ein-/Ausgabe 14 -12V ! xxx : D1 : 15 -5V xxx : - : /NMI: Vorang-Interupt 16 - xxx :..IEO : /INT: normaler Interupt 17 A17 ! xxx A11 ; IET: INT-Ketteneingang 18 A14 xxx A10 : IE0: INT-Kettenausgang 19 - xxx Ą16 ! : 20 /M1 xxx /NMI : /BUSRQ: DMA-Busanforderung 21 xxx xxx /INT : /BUAAK: DMA-Busfreigabe 22 - xxx /WR : /BAI: DMA-Ketteneingang 23 .../BAI ! xxx - : /BAO: DMA-Kettenausgang 24 : UBAT xxx /RD : /RDY: DMA-Handshake 25 :../BAO ! xxx /HALT : 26 /RDY ! xxx /PCL : /RESET: Rücksetz-Eingang 27 /IORQ xxx A12 : /PCL: Initialisieren 28 /RFSH xxx A15 : /WAIT: CPU-Wartezyklus 29 A13 xxx ClOCK : /HAlT; CPU gestoppt 30 A9 xxx /MERQ : /M1: 1. Maschinenzyklus 31 /BUSAK xxx /RESET : /RFSH: Auffischzyklus 32 GND GND GND : CLOCK: CPU-Takt (4-8 MHz) xxx reserviert für Erweiteungen ... Kettenleitungen (Daisy Chain) - zur freien Verwendung ! abweichend von der KONTRON-Norm

ECB-Busnormen anderer Hesteller auf einen Blick

CONITEC E-LAB ELZET J&K KONTRON MARFLOW miro o+r c10 xxx A21 -- A16 MBSO PHI/2 -- A16 a12 A18 A18 A18 /BAI /BAI A8 A18 /BAI c12 A19 A19 A19 A7 MBS1 A19 A19 A17 c13 xxx -12V -- A18 MBS2 -12V A20 A18 a14 -12V /MMUDIS -12V A19 MBS3 xxx -- A19 a16 -- 2PHI 2PHI 2PHI 2PHI nPHI 2PHI -- a17 A17 A17 A17 /BAO /BAO A17 A17 /BAO c19 A16 A16 A16 -- MBS5 A16 A16 -- a21 xxx BDCL -- -- MBS6 xxx A22 -- a22 -- /RY /BOOT /RDY MBS7 xxx A23 -- a23 /BAI /BAI /BAI /PF DPR /BAI /BAI -- c23 -- A20 /VBLANK /SEL MBS4 xxx A21 -- a25 /BAO /BAO /BAO -- nPHI /BAO /BAO -- a26 /RDY MEMD -- DESLCT WREN xxx /RDY /DESLCT | Nebenstehende Tabelle ohne Gewähr. Achtung! Die unterschiedliche Belegung der -12V-Leitungen kann bei einigen Kombinationen von Karten und Bussen veschiedener Hersteller zu starker Rauchentwicklung bei der Inbetriebnahme fühen! Deshalb -12V vorsichtshalber immer vorher abklemmen. |