EPSON TERMINAL FLOPPY

# TF-20

# TECHNICAL MANUAL

This Technical Manual provides technical information on the structure, maintenance, and repairs of the EPSON TERMINAL FLOPPY TF-20.

Major technical modifications, if made in the future, will be notified through Service Bullentins, and the Technical Manual should be revised accordingly. The details of the Manual are subject to change without notice.

All the information given in the Manual concerns the TF-20, and we are not responsible for any troubles with the industrial copyright of a third party that might arise from your application or connection of the TF-20 to other products.

Duplication or transcription of the Technical Manual, in part or in whole, is prohibited.

| CUA | מידים 1                                | CENEDAL                                                           |  |  |  |  |  |

|-----|----------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|

|     | IAPTER 1 GENERAL                       |                                                                   |  |  |  |  |  |

| 1.1 |                                        | Features of TF-20                                                 |  |  |  |  |  |

| 1.2 |                                        | actory Option                                                     |  |  |  |  |  |

| 1.3 |                                        | ceability                                                         |  |  |  |  |  |

| 1.4 |                                        | ction of TF-20 with Personal Computer                             |  |  |  |  |  |

| 1.5 |                                        | al Specifications of TF-20 (Standard)                             |  |  |  |  |  |

| 1.6 |                                        | s of Interface Signals of TF-20 (Standard)                        |  |  |  |  |  |

| 1.7 | Main (                                 | Components                                                        |  |  |  |  |  |

| CHA | PTER 2                                 | PRINCIPLES OF OPERATION                                           |  |  |  |  |  |

| 2.1 | Genera                                 | al (Standard Model)                                               |  |  |  |  |  |

| 2.2 | Block                                  | Diagram                                                           |  |  |  |  |  |

| 2.3 | Princip                                | ples of Operation (TF-20 Standard Model)                          |  |  |  |  |  |

| 2.4 | Electri                                | cal Circuit                                                       |  |  |  |  |  |

|     | 2.4.1                                  | Fuse and filter circuit                                           |  |  |  |  |  |

|     | 2.4.2                                  | Power transformer                                                 |  |  |  |  |  |

|     | 2.4.3                                  | Switching regulator circuit                                       |  |  |  |  |  |

|     | 2.4.4                                  | Mini-floppy disk drive control circuit                            |  |  |  |  |  |

|     | 2.4.                                   | 1.1 Read/write logic and amplifier circuit                        |  |  |  |  |  |

|     | 2.4.4                                  | 1.2 Voice coil motor control circuit                              |  |  |  |  |  |

|     | 2.4.4                                  | 1.3 Track 00 sensor circuit                                       |  |  |  |  |  |

|     | 2.4.4                                  | 2.4.4.4 Head load drive circuit                                   |  |  |  |  |  |

|     | 2.4.4                                  | 1.5 Index sensor circuit                                          |  |  |  |  |  |

|     | 2.4.4                                  | 4.6 Side select circuit                                           |  |  |  |  |  |

|     | 2.4.4                                  | 1.7 Write protect circuit                                         |  |  |  |  |  |

|     | 2.4.4                                  | 1.8 Drive select circuit                                          |  |  |  |  |  |

|     | 2.4.4                                  | 1.9 Drive motor control circuit                                   |  |  |  |  |  |

| CHA | PTER 3                                 | B DISASSEMBLY & ASSEMBLY                                          |  |  |  |  |  |

| 3.1 | Genera                                 | al                                                                |  |  |  |  |  |

| 3.2 | Tools                                  | and Measuring Instruments                                         |  |  |  |  |  |

| 3.3 | Disassembly and Assembly               |                                                                   |  |  |  |  |  |

|     | 3.3.1 Removal of upper and lower cases |                                                                   |  |  |  |  |  |

|     | 3.3.2                                  | Dismounting of disk drive SD-320                                  |  |  |  |  |  |

|     | 3.3.3                                  | 3.3.3 Dismounting of power supply unit                            |  |  |  |  |  |

|     | 3.3.4                                  | Dismounting of power filter circuit board and power transformer   |  |  |  |  |  |

|     | 3.3.5                                  | Dismounting of switching regulator circuit board                  |  |  |  |  |  |

|     | 3.3.6                                  | Removal of power switch and power cord                            |  |  |  |  |  |

|     | 3.3.7                                  | Dismounting of power lamp and front cover                         |  |  |  |  |  |

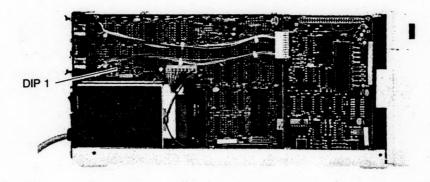

|     | 338                                    | Dismounting of SD320 mini-floppy disk drive control circuit board |  |  |  |  |  |

3.4 Adjustments and Settings

#### CHAPTER 4 HX-20 FACTORY OPTION

#### 4.1 General

- 4.1.1 Features of TF-20 (HX-20 Type Model)

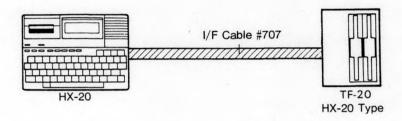

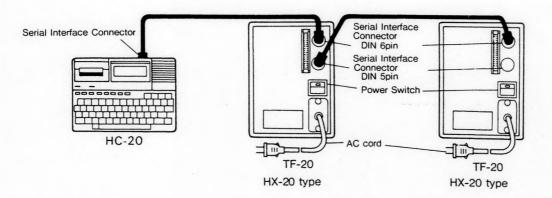

- 4.1.2 Connection

- 4.1.3 Specifications

- 4.1.4 Format specification

- 4.1.5 Interface connector

- 4.1.6 Constitution of TF-20 (HX-20 Type Model)

#### 4.2 Princhples of Operation

- 4.2.1 General

- 4.2.2 Block Diagram

- 4.2.3 Principles of operation

- 4.2.4 Electrical Circuit

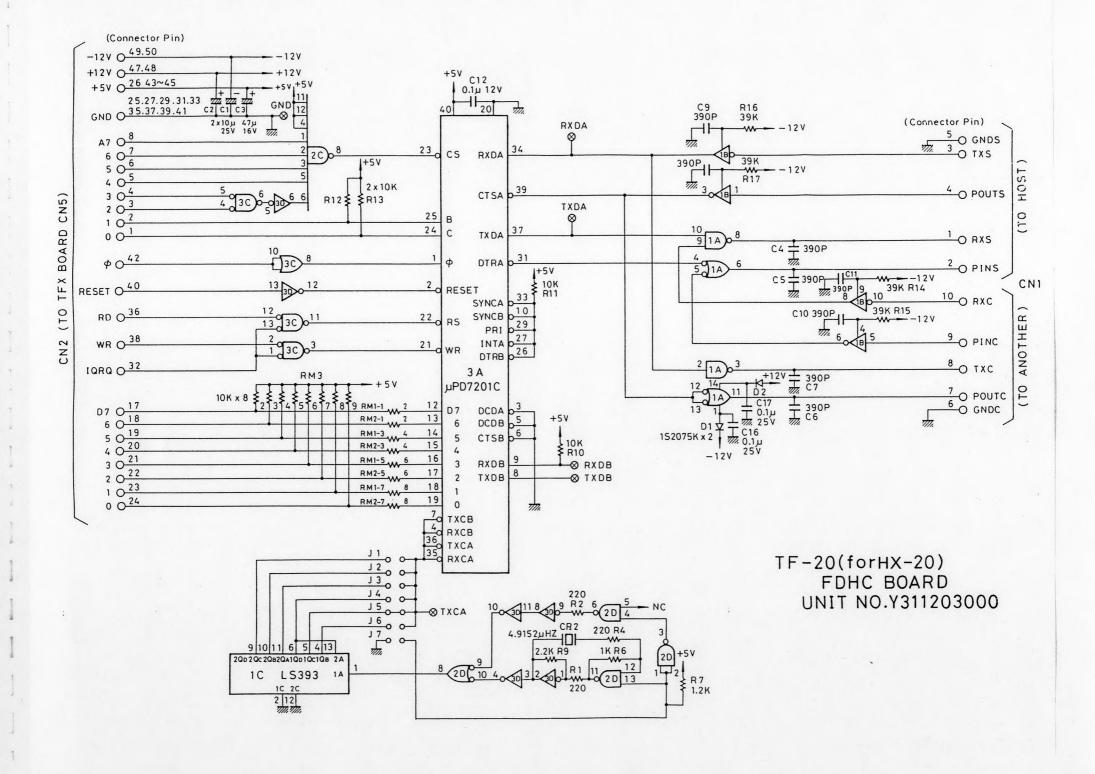

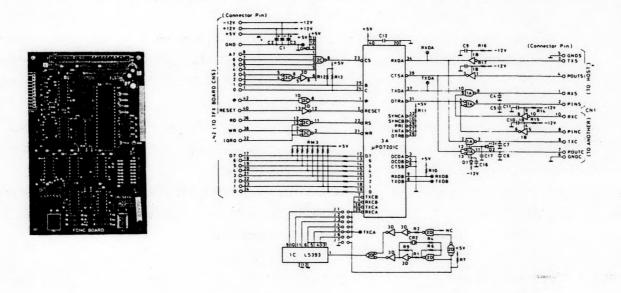

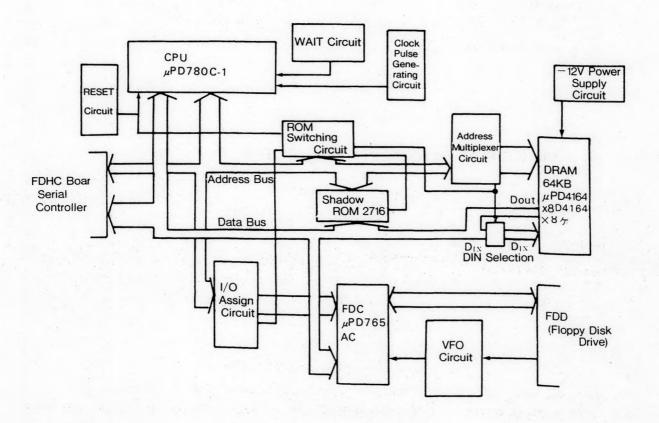

- 4.2.4.1 Function and role of multi-protocol serial controller μPD7201C

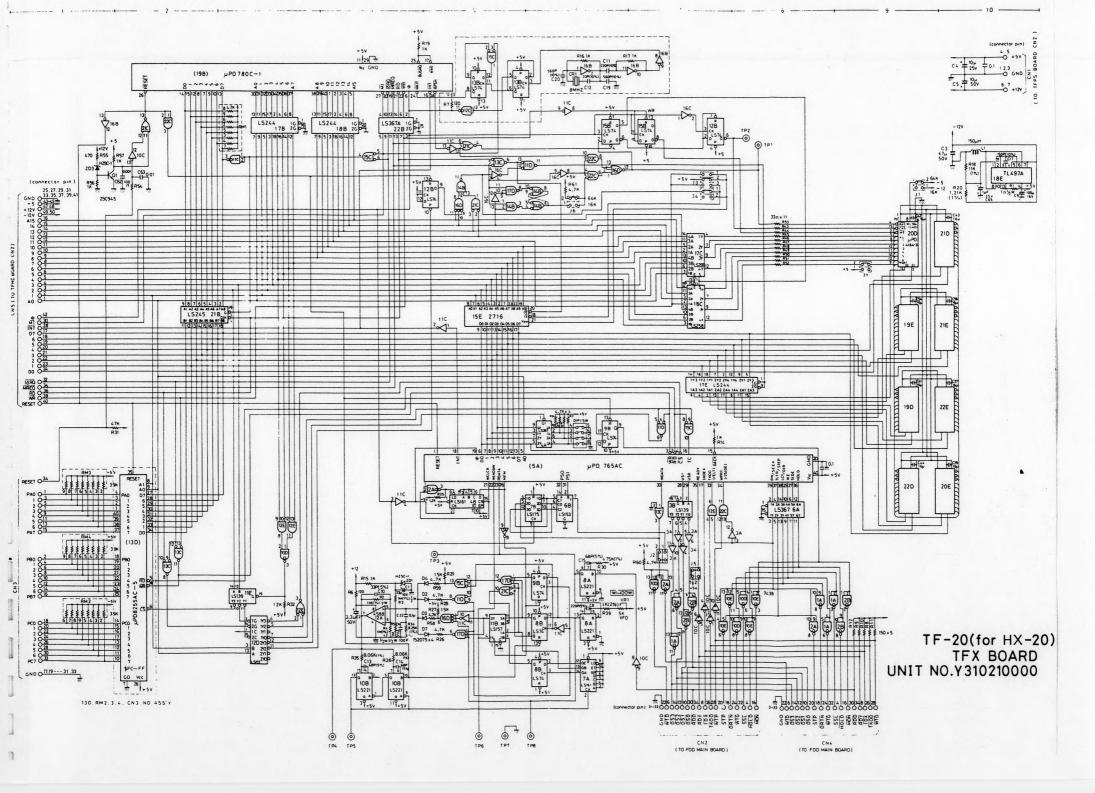

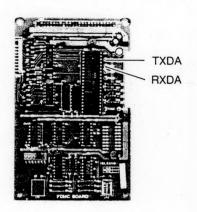

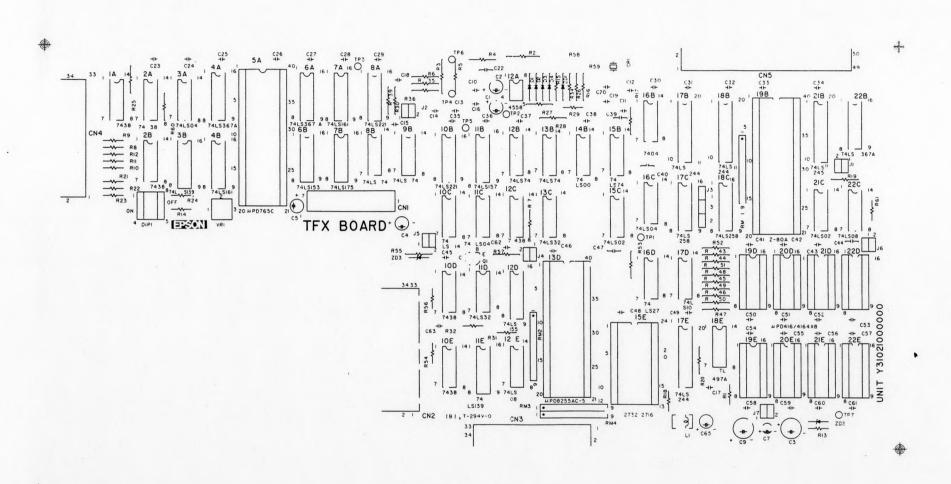

- 4.2.4.2 Function and role of TFX board

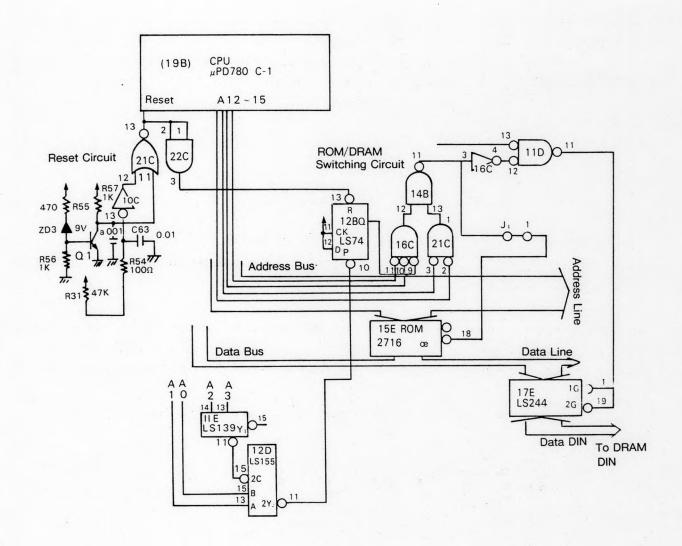

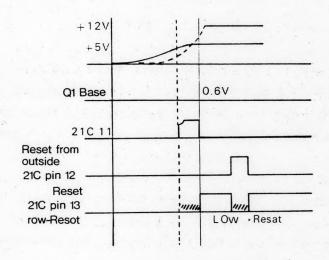

- 4.2.4.3 RESET circuit and ROM/RAM switching circuit

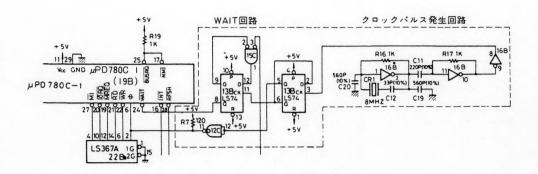

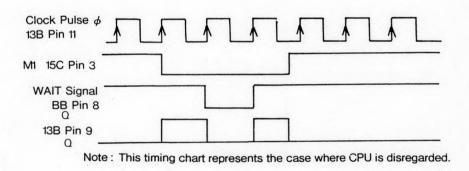

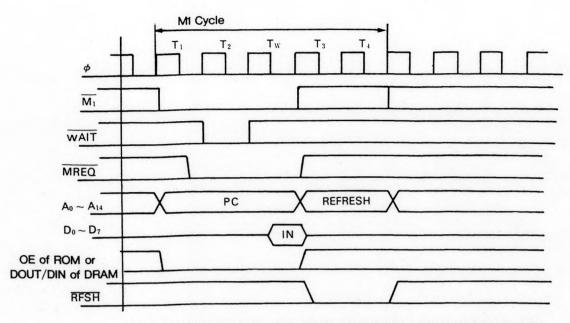

- 4.2.4.4 Clock pulse and WAIT signal

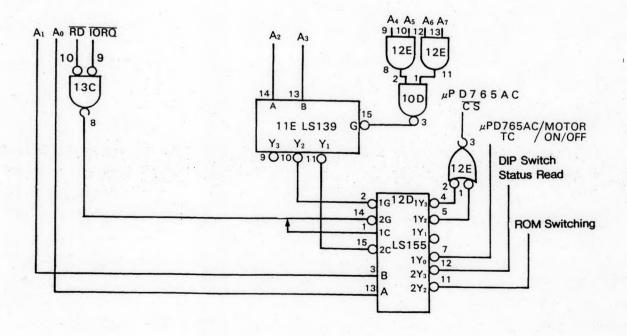

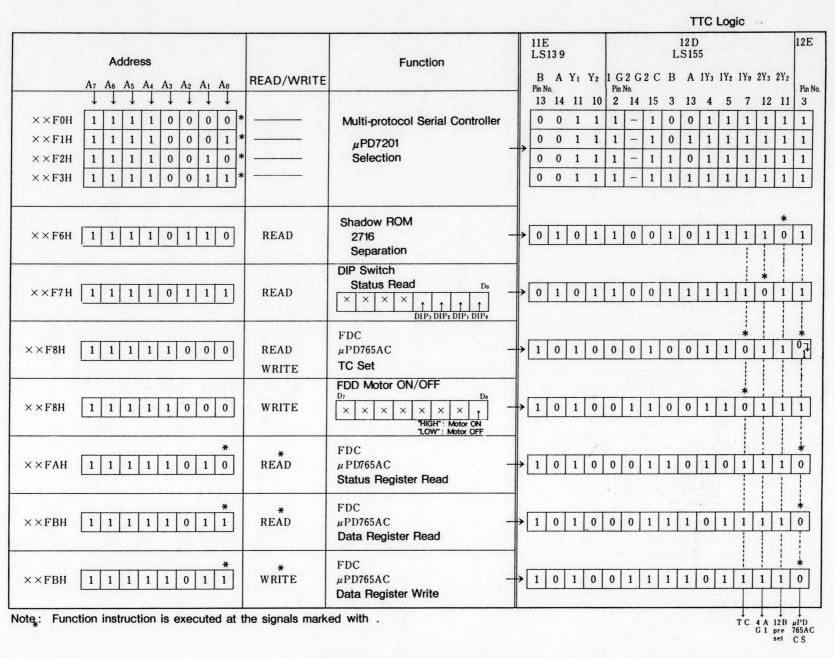

- 4.2.4.5 I/O assign circuit

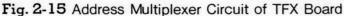

- 4.2.4.6 Address multiplexer circuit

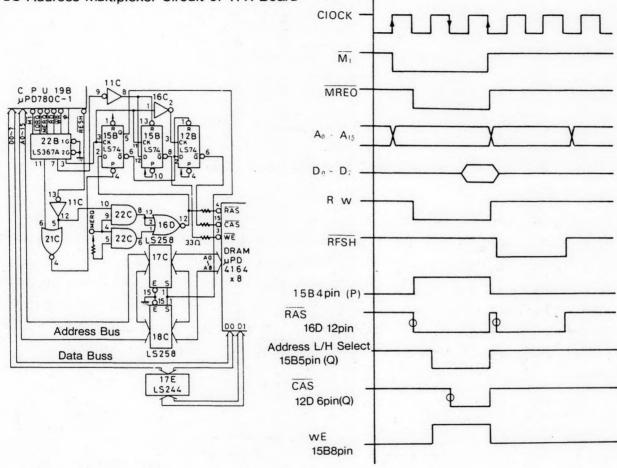

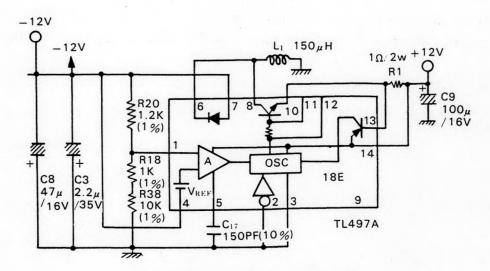

- 4.2.4.7 -12V chopper type regulator circuit

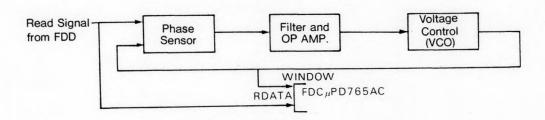

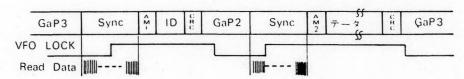

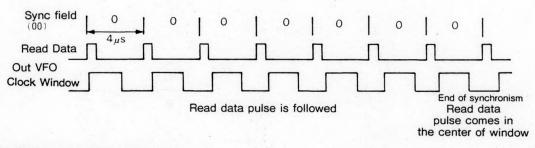

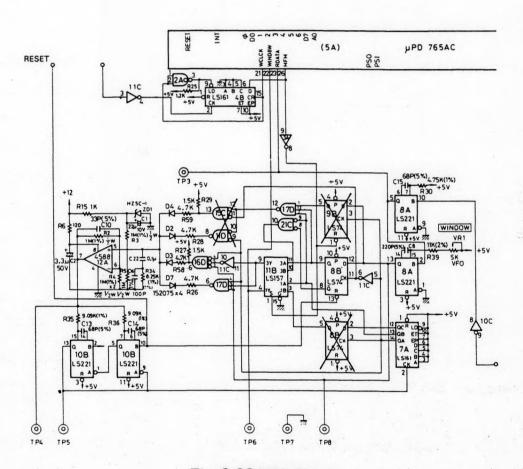

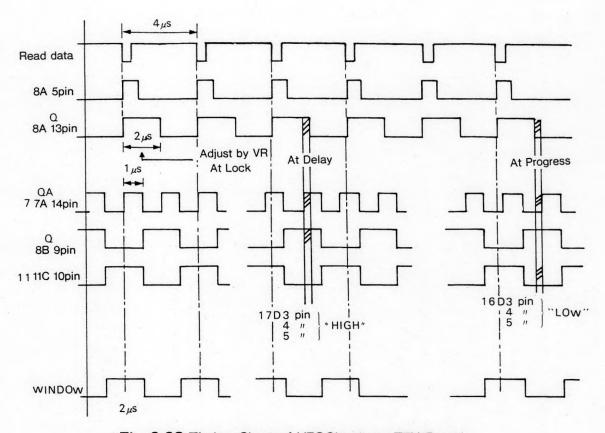

- 4.2.4.8 VFO circuit

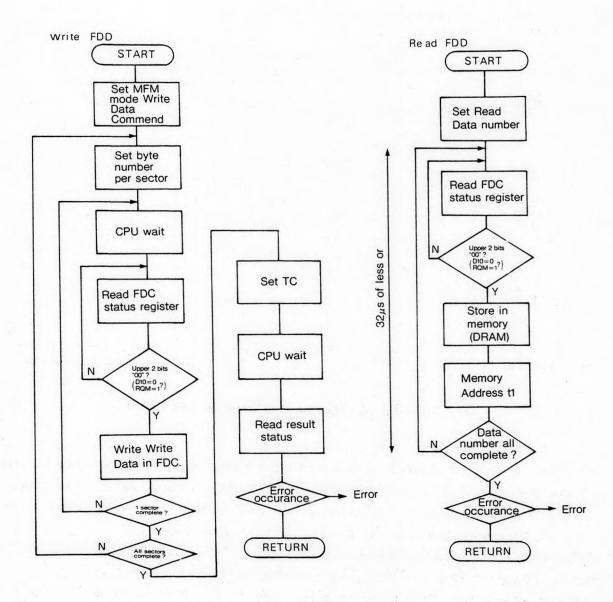

- 4.2.4.9 FDC μPD765AC

#### 4.3 Adjustments

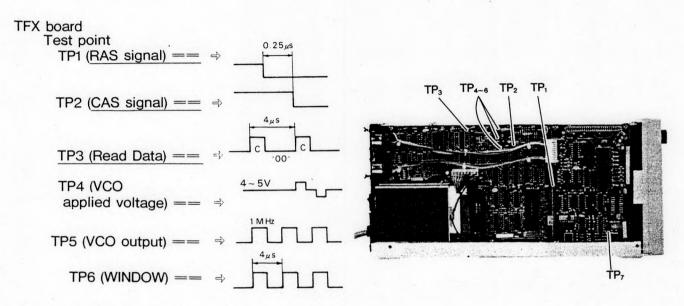

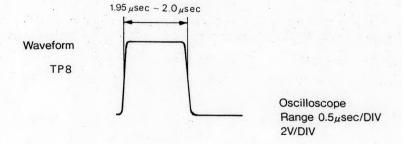

- 4.3.1 Adjustment and test points

- 4.3.2 Drive extension of TF-20 (HX-20 type model)

#### CHAPTER 5 TROUBLESHOOTING

#### 5.1 General

- 5.1.1 How to use Troubleshooting Flow Charts

- 5.1.2 Check-out Flow Chart

- 5.1.3 Repair by unti replacement

#### 5.2 Repair by Component Replacement

- 5.2.1 Trouble shooting of SD-320 main board and DM control board

- 5.2.2 Repair of HX-20 factory option

#### CIRCUIT DIAGRAMS

# CHAPTER 1 GENERAL

#### 1.1 Features of TF-20

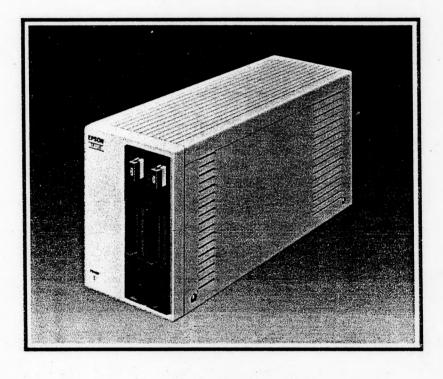

The TF-20 is a compact terminal floppy disk drive unit incorporating two ultra-thin 5.25-inch floppy disk drives.

It is a fruit of EPSON's unrelenting efforts in pursuit of miniaturization, light weight and high performance.

The TF-20 will thus display its intended performance fully, used in linkage with various computers. It can also have "factory option" interface boards to permit its connection to any of the computers which are provided with various interfaces. Merely adding these optional interface boards to the TF-20 will make desired data transfer possible between the computer and the TF-20.

# 1.2 Factory Option

The standard TF-20 comprises the power circuit and two 5.25-inch floppy disk drives with the interface compatible with Shugart's SA450(U.S.A.). In addition, the TF-20 can be an exclusive-use floppy disk drive unit with the following factory option board incorporated in it. The factory option unit, however, can not be added or remodeled once the TF-20 is shipped from the factory.

HX-20 Factory Option:

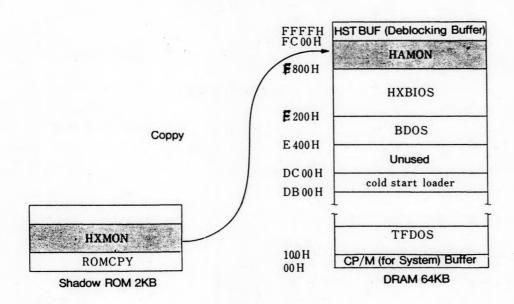

With this factory option incorporated, the TF-20 becomes an intelligent type of exclusive-use terminal floppy for the HX-20, having the CPU, I/0, 64 KB memory and high-speed serial interface within it.

### 1.3 Serviceability

The TF-20 has been designed to minimize maintenance and repair in its normal use.

Should maintenance or repair be required, the floppy disk drive mechanism and circuit boards of the TF-20 are readily replaceable. Therefore, the user can perform maintenance and repair quite easily by referring to this manual.

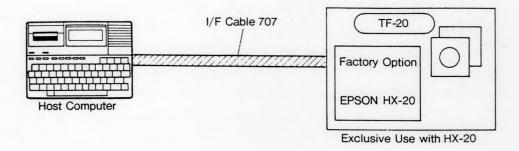

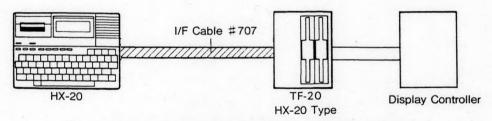

# 1.4 Connection of TF-20 with Personal Computer

Connection with the EPSON HX-20

# 1.5 General Specifications of TF-20 (Standard)

(1) Memory capacity (unformat)

Memory capacity per unit: 1000 KB(double density recording)

: 500 KB(single density recording)

(2) Memory system (format, double-side double-density recording)

Memory capacity per unit: 656 KB

Memory capacity per drive: 328 KB

No. of tracks per drive: 80 tracks

No. of sectors per track: 16 sectors

Memory capacity per sector: 256 B

- (3) Memory density: 5876 BPI

- (4) Data transfer speed: 250 Kbits/sec

- (5) Av. track rotation waiting time: 100 msec

- (6) Access time

Inter-track access time: 15 msec

Av. inter-track transfer access time: 220 msec

Settling time: 15 msec

- (7) Head loading time: 35 msec

- (8) Motor start time: 0.5 sec

- (9) Motor speed: 300 r.p.m.

- (10) R/W head positioning system: Voice coil motor system

- (11) Disk drive motor: Outer rotor type brushless transistor motor

(12) Power supply

Voltage: AC115/220/240V

Frequency: 49.5 to 60.5 Hz

Power consumption: 40W

(13) Dimensions

Width: 120 mm

Depth: 350 mm

Height: 165 mm

(14) Weight: 6 kg

(15) Ambient conditions

Temperature (operating): 5° C to 30° C

(non-operating): -30° C to 65° C

Relative humidity (operating): 20% to 80% (no condensation)

(non-operating): 5% to 85% (no condensation)

Shock resistance (operating): 1G for 1ms maximum

(non-operating): 2G for 1ms maximum

Vibration resistance

(operating): No R/W error at 0.6G, 5 to 60Hz

(non-operating): No abnormality at 1.0G, 5 to 60Hz

(16) Insulation resistance/strength

Insulation resistance:  $10M\Omega$  min. between AC power supply and case

Insulation strength: Can withstand 1kV (R.M.S.) 50/60Hz applied between AC power supply and

case for a minute.

## 1.6 Timings of Interface Signals of TF-20 (Standard)

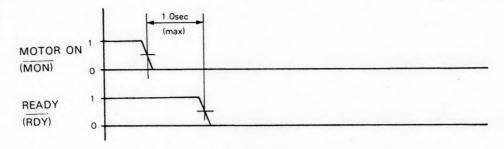

#### (1) Power up mode

The READY signal becomes "LOW" when the INDEX pulse is counted four times or more in one second with the disk rotating, and the Seek and R/W operation become possible.

Fig. 1-1 Power Up Timing

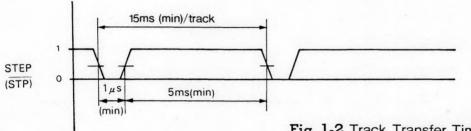

#### (2) Track transfer time

By inputting the "LOW" pulse to the STEP (STP) signal line, the read/write head positioning voice coil motor can be driven in the moving direction specified by the DRTN signal.

Fig. 1-2 Track Transfer Timing

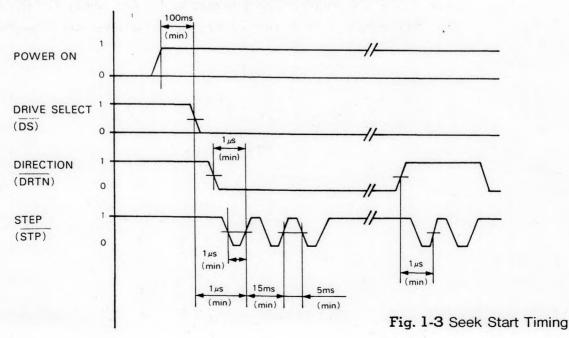

#### (3) Seek operation

This is the action timing for moving the magnetic head to the desired track. For a Seek operation, select a drive, set the DIRECTION signal for "LOW" or "HIGH" (specification of direction), then give pulses corresponding to the number of tracks for transfer from the present position to the STEP signal, and the magnetic head is set properly on the specified track.

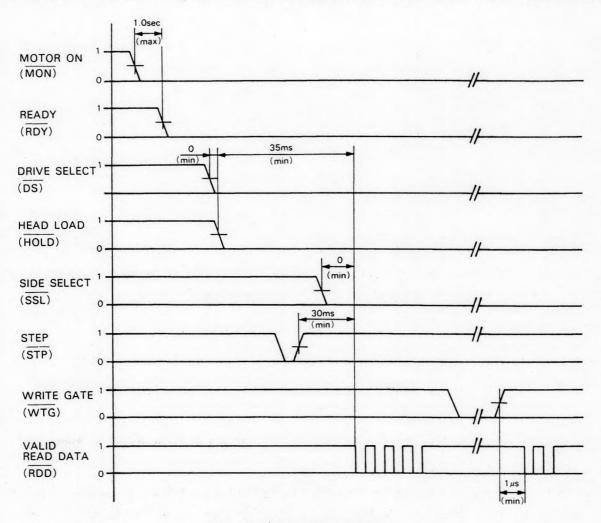

#### (4) Road Operation

In this mode, data written in the disk is read out. For a Read operation, make certain that the READY signal is "LOW", and select the drive to be used.

Then set the HEAD LOAD signal for "LOW" and specify Side 0 or 1 by the SIDE SELECT signal.

Fig. 1-4 Read Start Timing

The read data to be output is a pulse string of raw data read by the read circuit. The READ DATA signal is normally "HIGH", and outputs a "LOW" pulse where there is an inversion of magnetization on the disk.

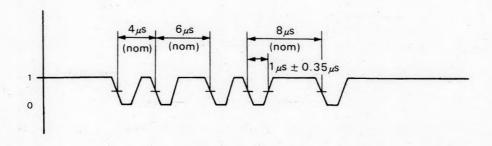

Fig. 1-5 Read Data Timing MFM System

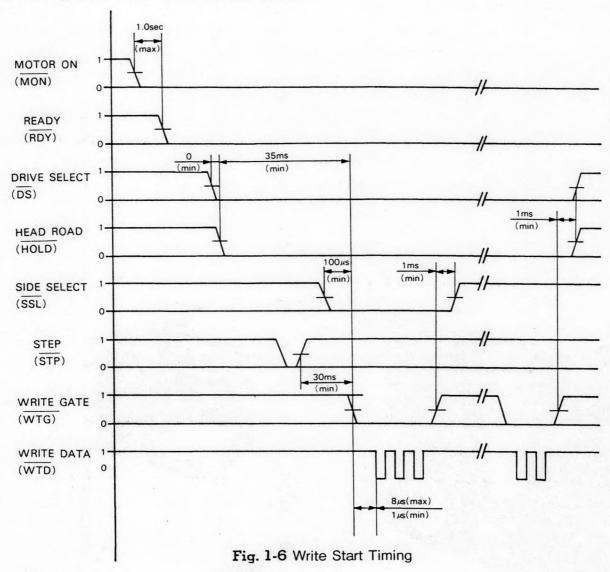

#### (5) Write operation

In this mode, data is written into the disk. For a Write operation, operate from the READY signal to the SIDE SELECT signal the same way as explained in "Read operation". Then set the WRITE GATE signal for "LOW" and send write data.

The WRITE DATA timing in which data is written into the disk is as follows.

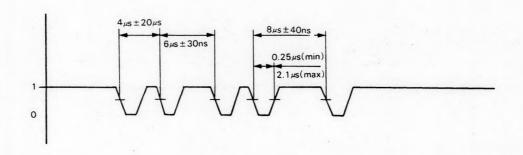

Fig. 1-7 Write Data Timing MFM System

### 1.7 Main Components

The TF-20 consists mainly of the following four units:

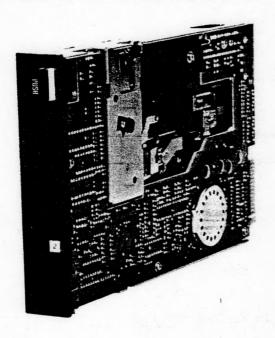

(1) SD-320 mini-floppy disk drive unit

This floppy disk drive unit of the TF-20 comprises the read/write head section, the head access mechanism, the head load mechanism, the disk drive mechanism, the disk protection mechanism, the disk eject mechanism, the index sensor section, the write protect sensor section and the control circuit section with the main and other PC boards.

The R/W head positioning system employs a VCM (voice coil motor) type linear actuator. And most of the control circuits are on the two chips of LSI developed by EPSON. As a result, the disk drive unit features high reliability and an ultra-thin size of 28 mm.

Furthermore, the maintenance is quite easy as is instructed in the Technical Manual of the 5.25 -lnch Floppy Drive Unit SD-320. The TF-20 has two of this drive unit on it.

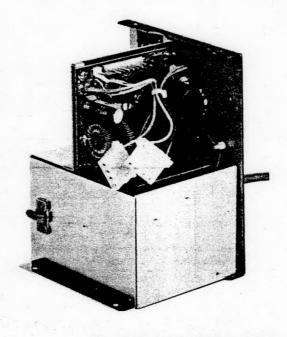

Fig. 1-8 SD-320 Mini-Floppy Disk Drive Unit

Fig. 1-9 Power Supply Unit

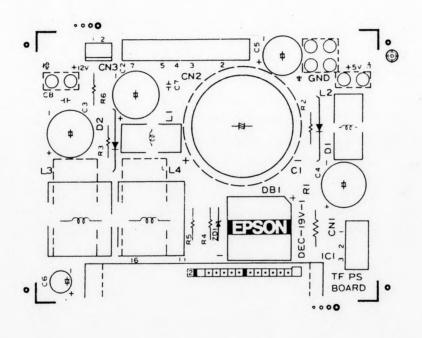

#### (2) Power supply unit

The power supply unit has the switching regulator circuit board mounted on the heat radiation plate. And the power transformer is mounted within the heat radiation plate and the line filter circuit board on it.

This power supply unit supplies all the voltages required for the TF-20. The line filter, consisting of a capacitor, suppresses noise to and from outside.

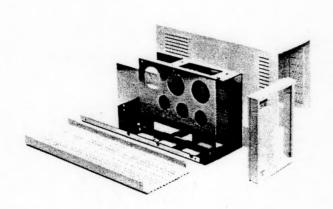

#### (3) Frame and case unit

The bottom panel and the floppy mounting plate permit easy installation of the mini-floppy drive unit. The disk drive unit, the power supply unit and the frame components are housed in the cover, bottom plate, front panel and rear panel.

Fig. 1-10 Frame and Case Unit

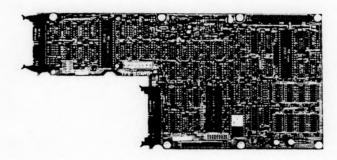

Fig. 1-11 Factory Option Unit

#### (4) Factory option unit

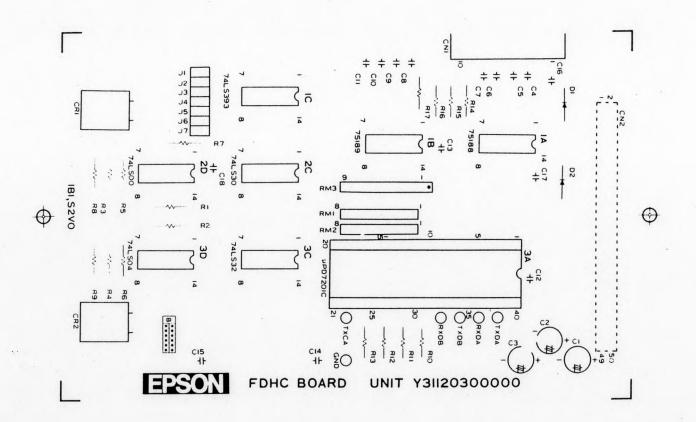

As a factory option, the following unit can be incorporated at the request of the user. The factory option unit, however, can not be added or remodeled once the TF-20 is shipped from the factory. Factory Option: FDHC circuit board + TFX circuit board exclusive use with the EPSON HX-20

# CHAPTER 2 PRINCIPLES OF OPERATION

# 2.1 General (Standard Model)

This chapter provides descriptions of the signals at the various connectors of the terminal floppy TF-20 and of the principles of operation of the floppys electric circuits and mechanisms.

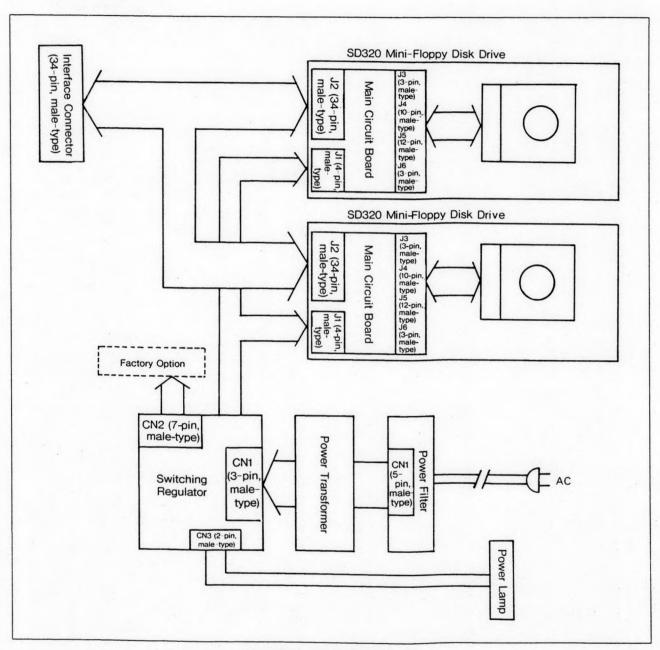

# 2.2 Block Diagram

Fig. 2-1 Block Diagram

#### (1) Interface Connector

(a)Use: This connector is used for data exchange between the TF-20 and an external computer.

(b) Number of pins: 34 pins

(c)Part number: DDK FRC2-PA34-30LN

(d)Pin assignment: Refer to Table 2-1 below.

Table 2-1 Pin Assignment of Interface Connector

| Interface<br>Connector<br>Signal<br>Pin No. | Drive SD-320<br>J2Connector<br>Signal<br>Pin No. | Signal | Direc-<br>tion | Description                                                                                                                                                                                                                             |

|---------------------------------------------|--------------------------------------------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                           |                                                  | NC     |                |                                                                                                                                                                                                                                         |

| 4                                           | 4                                                | HOLD   | ln             | The HEAD LOAD signal at Logic "0" causes the read/write head to be loaded on the disk.  (Pin 5 and Pin 6 of the DIP switch SS1 in the SD 320 mini disk drive can make head loading possible at a DRIVE SELECT signal.)                  |

| 6                                           | 6                                                | DS3    | In             | This is the DRIVE SELECT 3 signal. Up to 4 mini disk drives can be connected in a daisy chain by the switching of the DRIVE SELECT signals. (The drive selection is made by pin 4 of the DIP switch SS1 on the SD-320 mini disk drive.) |

| 8                                           | 8                                                | ĪDX    | Out            | The INDEX signal causes a Logic "0" pulse to be generated at each complete revolution of the floppy disk. The trailing edge of Logic "1" to Logic "0" indicates the beginning of data on the specified track.                           |

| 10                                          | 10                                               | DS0    | In             | This is the DRIVE SELECT 0 siganl. (The drive selection is made by pin 1 of the DIP switch SS1 on the SD-320 mini disk drive.)                                                                                                          |

| 12                                          | 12                                               | DS1    | In             | This is the DRIVE SELECT 1 signal. (The drive selection is made by pin 2 of the DIP switch SS1 on the SD-320 mini disk drive.)                                                                                                          |

| 14                                          | 14                                               | DS2    | In             | This is the DRIVE SELECT 2 signal.  Up to 4 mini disk drives can be connected in a daisy chain.  (The drive selection is made by pin 3 of the DIP switch SS1 on the SD-320 mini disk drive.)                                            |

| 16                                          | 16                                               | MON    | In             | The MOTOR ON signal at Logic "0" causes the disk drive motor to start.                                                                                                                                                                  |

| 18                                          | 18                                               | DRTN   | In             | The DIRECTION signal determines the moving direction of the voice coil motor.  The motor moves from track 00 to track 39 at Logic "0" or from track 39 to track 00 at Logic "1".                                                        |

| Interface<br>Connector<br>Signal<br>Pin No. | Drive SD-320 J₂Connector Signal Pin No. | Signal | Direc-<br>tion | Description                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------|-----------------------------------------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20                                          | 20                                      | STP    | . In           | When a pulse is input to the STEP signal line, the voice coil motor, which controls the position of the read/write head, moves in the direction specified by the DRTN signal.  When the WRITE GATE signal is at Logic "0", the STEP signal is inhibited.                                                                      |

| 22                                          | 22                                      | WTD    | In             | The WRITE DATA signal line transfers data to be written into the disk. When the input pulse falls from Logic "1" to Logic "0", the write current flows in the opposite direction and enters the read/write head, causing a change in the magnetic flux. This signal is valid only when the WRITE GATE signal is at Logic "0". |

| 24                                          | 24                                      | WTG    | In             | The WRITE GATE signal controls both Read Data and Write Data signals. When this signal is at Logic "0", the Write Data is valid, whereas when it is at Logic "1", the Read Data is valid.                                                                                                                                     |

| 26                                          | 26                                      | TKOO   | Out            | The TRACK 00 signal becomes Logic "0" when the read/write head is at the track 00 position.                                                                                                                                                                                                                                   |

| 28                                          | 28                                      | WPT    | Out            | The WRITE PROTECT signal notifies the host of the disk attached with a write protect label. It becomes Logic "0" when the disk has a write protect label attached.                                                                                                                                                            |

| 30                                          | 30                                      | RDD    | Out            | The READ DATA signal causes a pulse string of raw data to be output from the read circuit.  Normally, this signal becomes Logic "0" when the inversion of magnetization exists on the disk at logic level "1".                                                                                                                |

| 32                                          | 32                                      | SSL    | In             | The SIDE SELECT signal is used to select the upper or the lower read/write head. Side 1 (upper head) is selected at Logic "0", and Side 0 (lower head) at Logic "1".                                                                                                                                                          |

| 34                                          | 34                                      | RDY    | Out            | The READY signal becomes Logic "0" when the power is turned on and a disk loaded rotates normally (INDEX pulse : 4 pulses).                                                                                                                                                                                                   |

| 1<br>add<br>pin                             | 1<br>, add<br>, pin<br>33               | GND    |                | Twisted Pair Return signal GND Level.                                                                                                                                                                                                                                                                                         |

Section 2

Bearing and

Section 1

Benchmannen

Management of the

Management of the second

the control of

Samooned .

Secondary .

Bercoons

Second second

\* ,

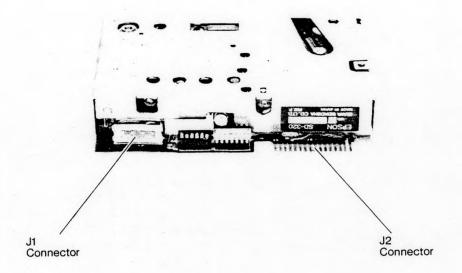

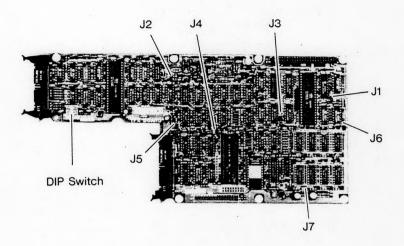

#### (2) SD-320 Mini-Floppy Disk Drive Connectors

#### 1) J1 Connector

(a)Use: This connector is used to supply + 5V and + 12V from constant-voltage power supply to

the mini-floppy disk drive.

(b)Number of pins: 4 pins (c)Part number: Japan AMP C-172349

(d)Pin assignment: Refer to Table 2-2 below.

Table. 2-2 Pin Assignment of J1 Connector

| Pin No. | Signal | Lead Wire Color | Use              |

|---------|--------|-----------------|------------------|

| 1       | +12V   | Orange          | +12V             |

| 2       | GND    | Black           | Signal GND level |

| 3       | GND    | Black           | Signal GND level |

| 4       | +5V    | Red             | +5V DC           |

#### 2) J2 connector

(a)Use: This connector is used for data exchange between the interface connector and the

SD320 mini-floppy disk drive.

(b)Number of pins: 34 pins

(c)Part number: DDK 225F-A34-3 (d)Pin assignment: Refer to Table 2-1.

#### 3) J3 connector

(a)Use: This connector is used to send the drive motor control signal from the main circuit board to the DM control circuit board.

(b) Number of pins: 3 pins

(c)Part number: Japan MOLEX 3022-3A

(d)Pin assignment: Refer to Table 2-3 below.

Table. 2-3 Pin Assignment of J3 Connector

| Pin No. | Signal | Mating Connector                              | Use              |

|---------|--------|-----------------------------------------------|------------------|

| 1       | CONT   | P3 connector pin 1 Drive motor control signal |                  |

| 2       | +12V   | P3 connector pin 2 +12V DC                    |                  |

| 3       | GND    | P3 connector pin 3                            | Signal GND level |

#### 4) J4 connector

(a)Use: This connector is used to transfer the control signals of the main circuit board and the VCM adjustment circuit board.

(b)Number of pins: 10 pins

(c)Part number: Japan MOLEX 3022-10A

(d)Pin assignment: Refer to Table 2-4 below.

Table. 2-4 Pin Assignment of J4 Connector

| Pin No. | Signal           | Mating Connector   | Use                                                                                                           |

|---------|------------------|--------------------|---------------------------------------------------------------------------------------------------------------|

| 1-      | HEAD LOAD<br>SOL | P4 connector pin 1 | The HEAD LOAD SOL signal at Logic "O" causes the read/write head to be loaded on the disk                     |

| 2       | +12V             | P4 connector pin 2 | +12V DC                                                                                                       |

| 3       | VELOCITY<br>DET  | P4 connector pin 3 | The speed detection voltage of the VCM adjustment circuit boad is input.                                      |

| 4       | NEUTRAL          | P4 connector pin 4 | The reference voltage of the speed detection coil of the VCM adjustment circuit board is output.              |

| 5       | VCM FWD          | P4 connector pin 5 | When the VCM FWD signal is more than +6V the read/write head moves in the direction of track 00 to track 39.  |

| 6       | VCM BWD          | P4 connector pin 6 | When the VCM BWD signal is less than +6V, the read/write head moves in the direction of track 39 to track 00. |

| 7       | GND              | P4 connector pin 7 | Signal GND level                                                                                              |

| 8       | TRACK 00 IN      | P4 connector pin 8 | When the read/write head is on track00 the TRACK 00 IN signal is at Logic "0".                                |

| Pin No. | Signal     | Mating Connector    | Use                                                                                               |

|---------|------------|---------------------|---------------------------------------------------------------------------------------------------|

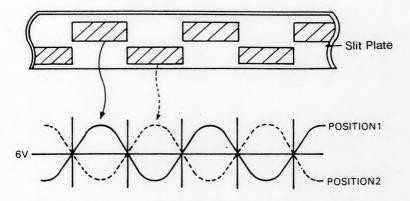

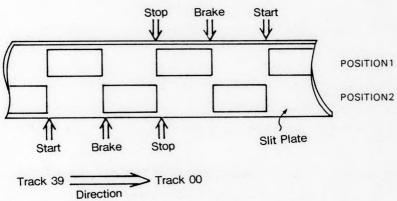

| 9       | POSITION 1 | P4 connector pin 9  | Step Timing signal from the position sensor of the VCM adjustment circuit.                        |

| 10      | POSITION 2 | P4 connector pin 10 | Step Timing signal from the position sensor of the position sensor of the VCM adjustment circuit. |

#### 5) J5 connector

(a)Use:This connector is used to transfer the signals of the main circuit board and the read/write head.

(b)Number of pins: 12 pins

(c)Part number: Honda HKP-12ML2L-4B

(d)Pin assignment: Refer to Table 2-5 below.

Table. 2-5 Pin Assignment of J5 Connector

| Pin No. | Signal   | Use                                                                           |

|---------|----------|-------------------------------------------------------------------------------|

| 1       | ERASE    | The signal is transferred to the erase coil of the read/write head of Side 1. |

| 2       | ERASE    | The signal is transferred to the erase coil of the read/write head of Side 0. |

| 3       | R/W COIL | The signal is transferred at the read/write head of Side 1.                   |

| 4       | R/W COIL | The signal is transferred at the read/write head of Side 0.                   |

| 5       | CENTER   | +5V is supplied to the read/write coil of Side 1.                             |

| 6       | CENTER   | +5V is supplied to the read/write coil of Side 0.                             |

| 7       | NC       |                                                                               |

| 8       |          |                                                                               |

| 9       | R/W COIL | The signal is transferred at the read/write head of Side 1.                   |

| 10      | R/W COIL | The signal is transferred at the read/write head of Side 0.                   |

| 11      | GND      | Signal GND of Side 1.                                                         |

| 12      | GND      | Signal GND of Side 0.                                                         |

#### 6) J6 conector

(a)Use: This connector is used to transfer the signals of the main circuit board and the index sensor.

(b)Number of pins: 3 pins

(c)Part number: Honda FFC-(3) TAMEP-1

(d)Pin assignment: Refer to Table 2-6 below.

Table 2-6 Pin Assignment of J6 Connector

| Pin No. | No. Sigal Mating Connector |                    | Use                                              |

|---------|----------------------------|--------------------|--------------------------------------------------|

| 1       | +5V                        | P6 connector pin 1 | +5V DC is supplied to the index sensor.          |

| 2       | GND                        | P6 connector pin 2 | Signal GND level                                 |

| 3       | INDEX IN                   | P6 connector pin 3 | The signal is transferred from the index sensor. |

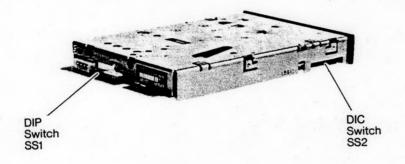

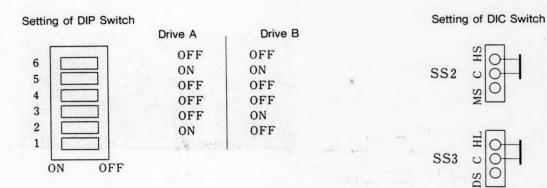

#### 7) Functions of DIP and DIC switches

Table 2-7 Functions of DIP switches SS1

| Switch No. | Function                                  |

|------------|-------------------------------------------|

| SS-1       | Drive 1 is set at ON.                     |

| 2          | Drive 2 is set at ON.                     |

| 3          | Drive 3 is set at ON.                     |

| 4          | Drive 4 is set at ON.                     |

| 5          | Head loading is made at HDLD signal by ON |

| 6          | Head loading is made at DS signal by ON   |

Table 2-8 Functions of DIC switches SS2 and SS3

| Switch No. |        | Function                                                          |

|------------|--------|-------------------------------------------------------------------|

| CCO        | COM-MS | Head loading is made at MON signal.                               |

| SS2        | COM-HS | Head loading is made at the signal selected by switch SS1-5 or 6. |

| SS3        | COM-DS | LED comes on at DS signal                                         |

|            | COM-HL | LED comes on at HDLD signal.                                      |

#### (3) Switching Regulator Connectors

#### 1) CN1 connector

(a)Use: This connector is used to supply voltage from the power transformer to the switching regulator board.

(b) Number of pins: 3 pins

(c)Part number: MOLEX 5239-3

(d)Pin assignment: Refer to Table 2-9 below.

Table 2-9 Pin Assignment of CN1 Connector

| Pin No. | Signal | Leab Wire Color | Use                                                |

|---------|--------|-----------------|----------------------------------------------------|

| 1       | AC 20V | Purple          | AC voltage is supplied from the power transformer  |

| 2       | NC     |                 |                                                    |

| 3       | AC 20V | Purple          | AC voltage is supplied from the power transformer. |

#### 2) CN2 connector

(a)Use: This connector is used to supply + 5V and + 12V from the switching regulator board to

the factory option board. (b)Number of pins: 7 pins

(c)Part number: MOLEX 5265-7

(d)Pin assignment: Refer to Table 2-10 below.

Table 2-10 Pin Assignment of CN2 Connector

|   | Signal | Lead Wire Color | Use              |

|---|--------|-----------------|------------------|

| 1 | GND    | Black           | Signal GND level |

| 2 | GND    | Black           | Signal GND level |

| 3 | GND    | Black           | Signal GND level |

| 4 | +5V    | Red             | +5V DC           |

| 5 | +5V    | Red             | +5V DC           |

| 6 | +12V   | Orange          | +12V DC          |

| 7 | +12V   | Orange          | +12V DC          |

#### 3) CN3 connector

(a)Use:This connector is used to supply voltage from the switching regulator board to the power

(b) Number of pins: 2 pins

(c)Part number: MOLEX 5051-02

(d)Pin assignment: Refer to Table 2-11 below.

Table 2-11 Pin Assignment of CN3 Connector

| Pin No. | Signal | Lead Wire Color | Use                       |

|---------|--------|-----------------|---------------------------|

| 1       | GND    | Black           | Cathode of the power lamp |

| 2       | LED    | Red             | Anode of the power lamp   |

#### (4) Power Filter Connector

#### 1) CN1 connector

(a)Use: This connector is used to supply AC voltage from the power filter to the power transformer.

(b) Number of pins:5 pins

(c)Part number: MOLEX 5239-5

(d)Pin assignment: Refer to Table 2-12 below.

Table 2-12 Pin Assignment of CN1 Connector

| Pin No. | Signal     | Lead Wire Color | Use                                        |

|---------|------------|-----------------|--------------------------------------------|

| 2       | AC voltage | White           | AC voltage is supplied to the transformer. |

| 5       | AC voltage | Blue            | AC voltage is supplied to the transformer. |

### 2.3 Principles of Operation (TF-20 Standard Model)

The SD-320 mini-floppy disk drive outputs the IDX signal to determine the beginning of track, the TK00 signal to show the read/write head in the track 00 position, and the RDY signal to identify the normal rotation of the disk. Also, the WPT signal is output to identify the presence or absence of writing into the disk.

These four signals determine the operation of the floppy disk. The signals sent to the disk drive are the drive signal for the drive head solenoid, the drive signal for the disk drive motor and the control signal for the head positioning VCM mechanism.

All these signals are converted to match the operation timings of the various mechanisms by the custom LSI SDF 9401F on the control circuit board within the disk drive. And the mechanisms of the disk drive performs operations according to these signals.

Refer to 2.4 and the separate SD-320 Technical Manual for detailed description of the electric circuits and mechanical operations.

Also, refer to chapter 4 for the operation principles of the control circuit of the factory option unit.

#### 2.4 Electrical Circuit

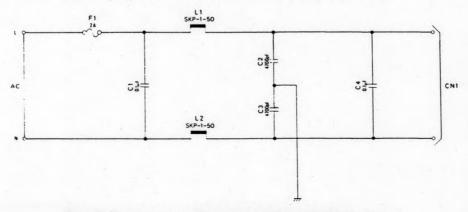

#### 2.4.1 Fuse and filter circuit

The fuse and filter circuit is located on a Bakelite circuit board, together with the power switch which turns on and off the primary AC input voltage. Fig.2-2 shows the layout of the respective components on the fuse and filter circuit, and Fig.2-3 shows the connection diagram of this circuit.

Fig. 2-2 Component Layout of Fuse & Filter Circuit

Fig. 2-3 Conection Diagram of Fuse & Filter Circuit

The AC Voltage from the power line first flows through the double-throw power switch and enters fuse F1.

Noise suppressing choke coils L1 and L2 are connected to this line. And between this line and ground, four noise suppressing capacitors C1 to C5 are connected. They function to filter the line noise from the power source as well as the noise from the disk drive unit to the power line, so that the digital circuits within the disk are not affected by external noise and any noise from the disk does not leak out to external lines.

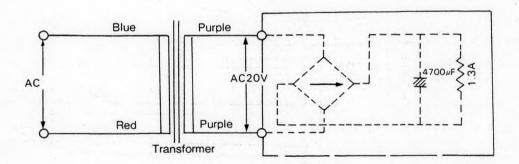

#### 2.4.2 Power transformer

The power transformer of the TF-20 lowers the AC Voltage from the primary side and supplies the voltages required for the floppy disk drive circuit and the control circuit of the factory option unit. Fig. 2-4 shows the layout of the power transformer, and Fig. 2-5 shows the circuit diagram.

Fig. 2-4 Layout of Power Transformer

Fig. 2-5 Circuit Diagram of Power Transformer

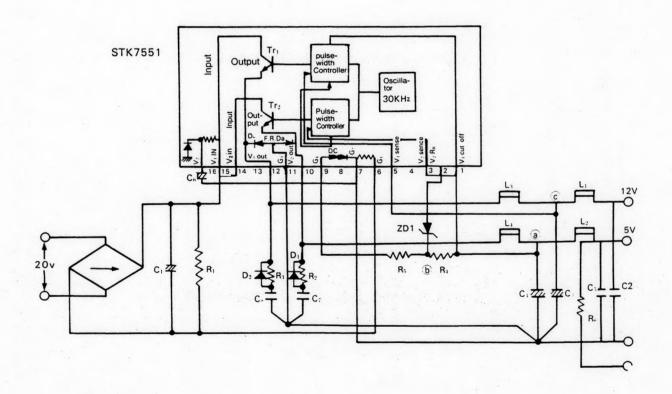

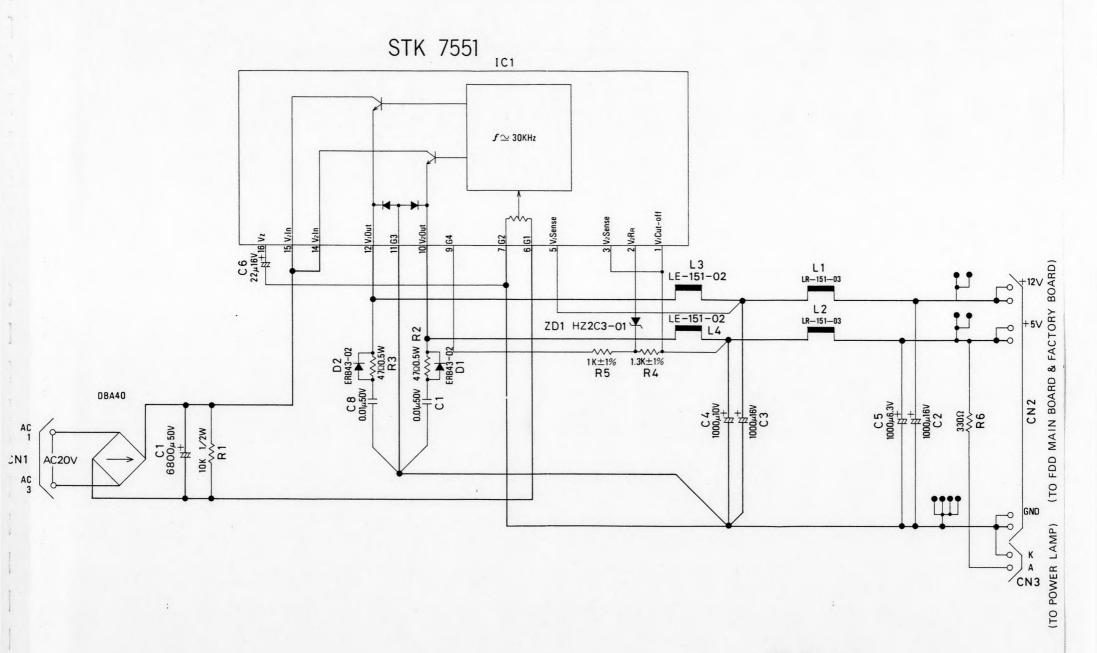

#### 2.4.3 Switching regulator circuit

The voltages lowered by the power transformer are converted into required voltages by the rectifier and switching regulator circuit. Fig. 2-6 shows the layout of the switching regulator circuit board, and Fig. 2-7 shows the circuit diagram.

Fig. 2-6 Layout of Switching Regulator

Fig. 2-7 Circuit Diagram of Switching Regulator

In the switching regulator circuit, the following voltages are produced:

$<sup>\</sup>left. \begin{array}{l} +5V \\ +12V \end{array} \right\} Power \ supply \ for \ floppy \ disk \ drive \ and \ factory \ option. \\ \left. \begin{array}{l} K \\ A \end{array} \right\} Power \ supply \ for \ power \ lamp. \end{array}$

#### 2.4.4.1 Read/write logic and amplifier circuit

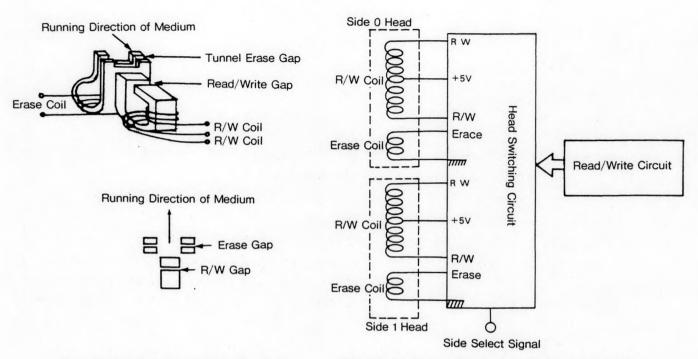

Fig. 2-12 shows the structure and the block diagram of the magnetic head.

Fig. 2-11 Structure of Magnetic Head

Fig. 2-12 Block Diagram of Magnetic Head

The magnetic head is of such a structure that it has an erase gap on both sides of the read/write gap. The erase gaps are located behind the read/write gap as viewed in the running direction of the medium. These erase gaps are designed to trim through data of one track and prevent interference by data of the adjacent tracks.

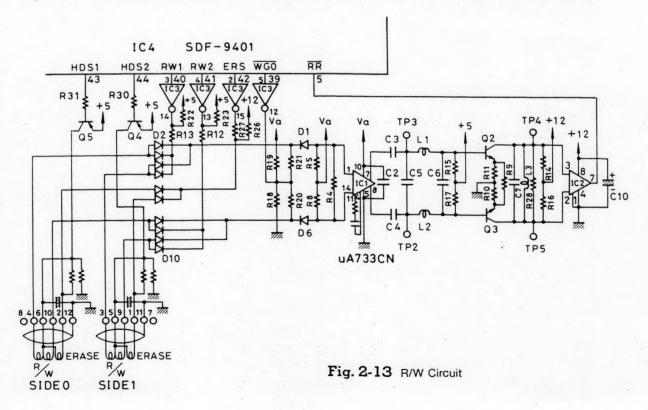

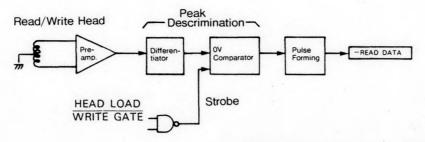

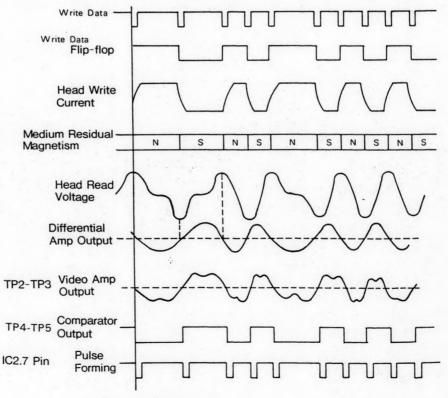

Fig.2-13 shows the read/write amp circuit diagram, and Fig.2-14 the block diagram of the read amp circuit. And Fig-15 shows the waveforms at various parts of write/read operations.

Fig. 2-14 Block Diagram of Read Amp Circuit

Write data sent to the drive from the controller has gone through FM modulation. It is frequency -divided by the flip-flop in IC4 to become a rectangular signal to be inverted at the Write Data pulse. This signal inverts the polarity of the head current, thus causing a flux inversion in synchronism with the Write Data pulse.

When pin 43 (HDSI) of IC4 becomes "LOW", a voltage of +5V is supplied to the R/W coil and erase coil of Side 0 from the current driver TrQ5. When pin 44 (HDS2) of IC4 becomes "LOW", a voltage of +5V is supplied to the R/W coil and erase coil of Side I from the current driver TrQ4. Selection of Side 0 or Side 1 is controlled by the Side Select signal sent to the drive from the controller.

At Read, the magnetic flux caused by the residual magnetism on the disk is detected by the head and is amplified by the preamplifier of IC1, Then it is passed through the low-pass filter circuit of differentiator C3, C4, C5, C6, L1 and L2 and the peak is detected by the 0V comparator at TrQ2 and Q3. And after going through the pulse forming by the comparator IC2, it is output at pin 5 (RR) of IC4.

Read data is not output when the Wait Gate (pin 39 of IC4) is at the "LOW"level.

n. Thus, tra-thin

nbining

?-18 the

029 |> |> |30

3 W TIOD BOILD B BELL TO B B ELL TO T

uit

nade by nals of the pin

19 is as

output TrQ8 in

oin 7 of

ig. 2-19

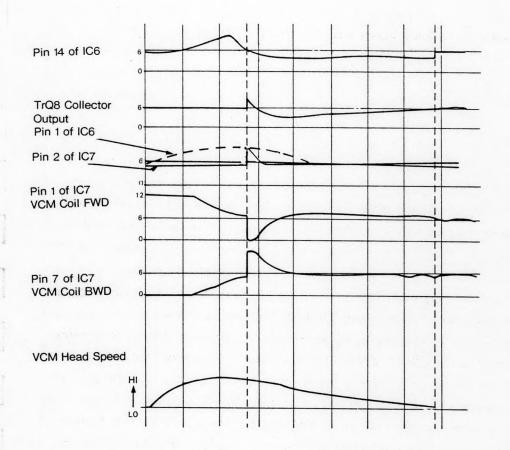

IC7 becomes a 2V level through inversion as shown in Fig. 2-18. Thus, a voltage is applied in the forward direction to the voice coil, which triggers the movement of the head from track 00 to track 39.

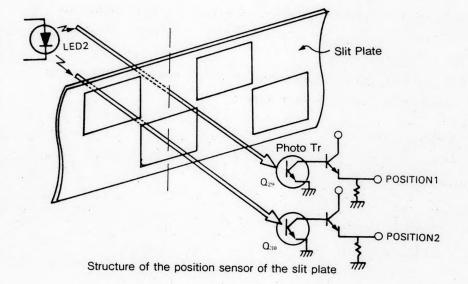

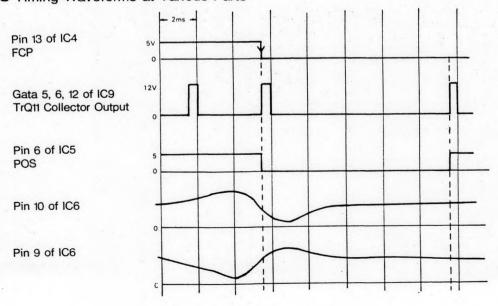

The voltage in proportion to the movement of the head is detected by the speed sensor coil and amplified by OP AMP, and it is subjected to a negative feedback in a voltage of +6V or above from pin 1 of IC6 to pin 2 of IC7. By this signal, the speed of the VCM head is kept constant. When it is 4.8 to 5.0 msec after the rising of pin 13 (FCP) signal of IC4 to +5V, the timing of the position sensor signals position 1 and 2 of the slit plate Where it is inputed to pin 9 and pin 10 of IC6 goes through an inversion. At the same time, pin 13 (FCP) signal of IC4 becomes 0V and TrQ8 is cut off. Since the voltage from the speed sensor coil at pin 1 of IC6 is +6V or above, the voltages at pin 1 and pin 7 of IC7 become 2V and +10V respectively as shown in Fig. 2-18. Thus the voice coil motor is braked once by the application of a voltage in the reverse direction. Then a voltage of +6V or below is supplied from pin 14 of IC6, and as a result a voltage in the forward direction works on the voice coil, thus decelerating the head gradually.

Now the timing of Positions 1 and 2 is inverted again, and out put at pin14 of IC6 become a low impedance, by the gate signal of pin 5,6,12 of IC9. which causes the voltage rise to +6V by charging the capacitor C20. The pulse at this time passes through the capacitor C21 and is input to pin 2 of IC7. This will brake the voice coil again and stops the head.

Fig. 2-19 shows the structure of the position sensor of the slit plate, the output voltage from the phototransistor of the position sensor of the slit plate and the start position. braking position and stop position of the position sensor of the slit plate. Then the movement of the VCM head from track 39 to track 00 is made on the same principle as that of the head from track 00 to track 39. In the operation, the pin 14 (BCP) signal of IC4 becomes 0V, and turns on TrQ7 to output + 12V. This will apply a voltage in the reverse direction to the voice coil and move the head from track 39 to track 00. Except for the gate pulse voltages at pin 5 of IC5 and pin 5, 6, 12 of IC9, the timing voltages at various parts are all opposite to those of the head movement from track 00 to track 39. Fig. 2-19 shows the start position, braking position and stop position of the position sensor of the slitplate.

As was mentioned already, the voice coil motor reaches the maximum speed at the middle position and after that is rapidly decelerated by the speed sensor.

Fig. 2-18 Timing Waveforms at Various Parts

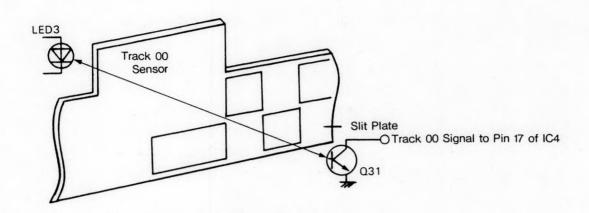

#### 2.4.4.3 Track 00 sensor circuit

When the read/write head is at track 00, a Track 00 sensor signal is given. As shown in Fig. 2 -20. the light from LED3 passes through the track 00 sensor part of the slit plate, turns off the phototransistor Q31 and makes a "HIGH" evel at pin 17 of IC4, thus signaling the track 00 position of the R/W head.

Fig. 2-20 Structure of Track 00 Signal Sensor

#### 2.4.4.4 Head load drive circuit

At a "HIGH" signal from pin 4 (HEAD) of IC5, the head load solenoid is energized, causing the pad lever to be pulled downward.

With the DIP and DIC switches set as in Table 2-13, the head load timing can be changed:

Tnble 2-13

DIP Switch SS1-5:ON Head loading at HOLD signal

6:ON Head loading at DS signal

DIC Switch SS2=CM-MS: Head loading at MON signal

COM-HS: Head loading at signal selected by DIP switch SS1-5 and 6

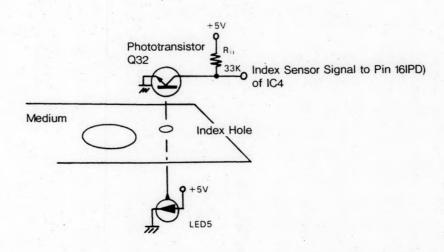

#### 2.4.4.5 Index sensor circuit

As shown in Fig. 2-21, the index sensor consists of a pair of light emitting diode LED and phototransistor Q32.

Fig. 2-21

POSITION1,2のスリット板の位置とフォト Tr からの出力電圧

moving the head from track 00 to track 39 or from track 39 to track 00

#### 2.4.4.6 Side select circuit

See the read/write circuit.

#### 2.4.4.7 Write protect circuit

The write protect circuit, consisting of a pair of LED and phototransistor Q1, detects the presence or absence of a write protect lable attached to the notch in the jacket.

#### 2.4.4.8 Drive select circuit

Drives 1 to 4 are respectively selected by the DIP switch SS1-1 to 3.

#### 2.4.4.9 Drive motor control circuit

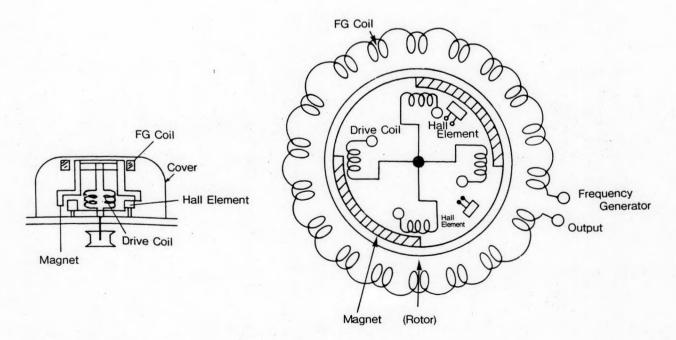

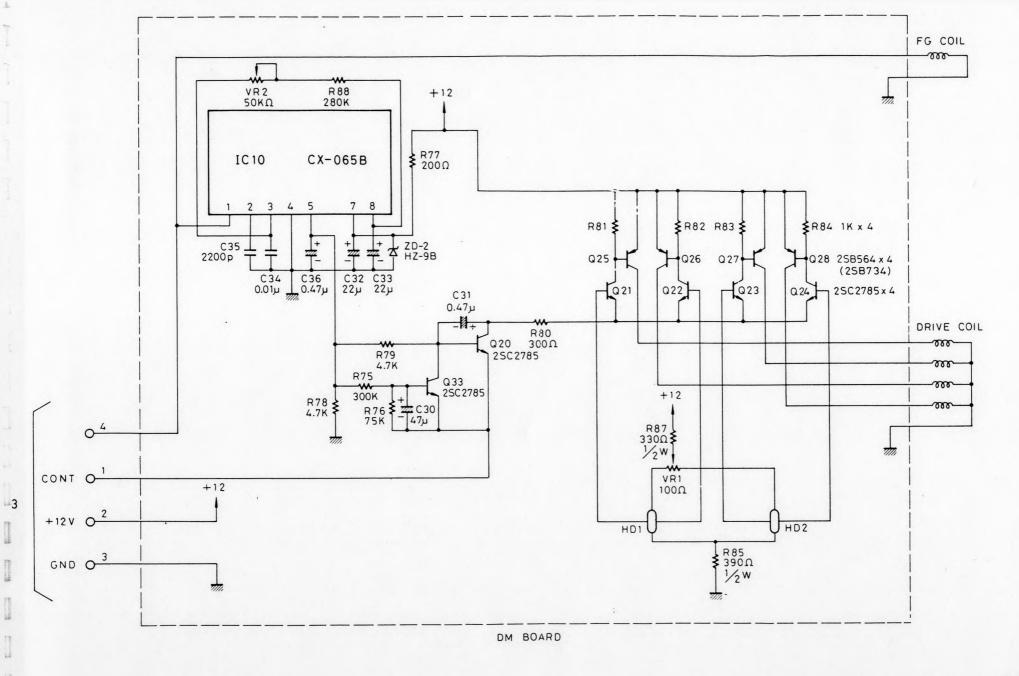

The disk drive motor is an outer-rotor-type DC motor featuring long service life.

As shown in Fig. 2-22, the motor mechanism consists of a frequency generator (FG) to generate the frequency proportional to the rotation of the rotor and a motor drive section.

When a current is fed to the drive coil in a stepping manner, the magnet rotor starts to run. With the magnet rotating, the frequency generator (FG) coil becomes a generator outputting the frequency proportional to the speed of rotation. The timing of the current sent to the drive coil is determined by the notch in the magnet passing the Hall element.

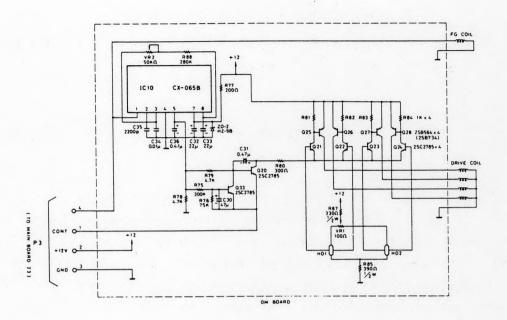

When the motor control output at pin 33 (MS) of IC4 becomes "HIGH", pin 10 of IC3 becomes "LOW", thus setting the emitters of TrQ33 and Tr Q20 for GND. At the same time, the base of TrQ33 becomes 0V and TrQ20 reseats switching by the pulse voltage from pin 5 of IC10.

When TrQ20 is on, the emitters of TrQ21, Q22, Q23 and Q24 are set at the 0V level. And the transistor selected by the Hall element of HD1 and HD2 turns on to supply current to the drive coil and causes the drive motor to run. The speed of the drive motor is determined by the pulse width from pin 5 of IC10, and the frequency at pin 5 of IC10 is determined by the frequency of the frequency generator (FG) coil and the variable resistance VR2.

Fig. 2-22 Principle of Operation

Fig. 2-23 shows the drive motor control circuit Fig. 2-23 DM Control Circuit

# CHAPTER 3 DISASSEMBLY & ASSEMBLY

# CHAPTER 4 HX-20 FACTORY OPTION

#### 4.1 General

#### 4.1.1 Features of TF-20 (HX-20 Type Model)

With the HX-20 factory option incorporated, the TF-20 becomes an intelligent type of exclusive -use terminal floppy for the HX-20, having the CPU, 64KB memory and high-speed serial interface within it. The TF-20 performs all the file manage-ment and exchanges necessary information with the HX-20. Accordingly, this TF-20 lightens the burden of file management on the HX-20 and reduces the OS of the HX-20's memory.

#### 4.1.2 Connection

#### (1) Connection with the HX-20

#### (2) Connection with the HX-20 and Display-Controller

Fig. 1-1 Connection of HX-20 Factory Option TF-20

#### 4.1.3 Specifications

(1) Memory capacity

Memory capacity per unit: 656 KB Memory capacity per drive: 328 KB

No. of tracks per drive: 80 tracks (40x2)

No. of sectors per track: 16 sectors

Memory capacity per sector: 256 B

(2) Access time

Inter-track access time: 15 msec

Communication with HC-20: 38.4 KBps

(3) Power supply

Voltage: AC115/220/240 V Frequency: 49.5 to 60.5 Hz

Power consumption: 40 VA max.

(4) Dimensions and weight

Width: 120mm Depth: 350mm Height: 165mm Weight 6kg

(5) Ambient conditions

Temperature (operating): 5°C to 30°C

(non-operating): -30°C to 65°C

Relative humidity (operating): 20% to 80% (no condensation)

(non operating): 5% to 85% (no condensation)

(6) Insulation resistance/strength

Insulation resistance: 10 M min. between AC power

supply and case (by DC500V megger)

Insulation strength: Can withstand 1KV (R.M.S.) 50/60Hz

applied between AC power supply and case for 1 min or more.

Shock resistance (operating): 1G for 1ms maximum

(non-operating): 2G for 1ms maximum

Vibration resistance

(operating):0.25G, 5-55Hz (non-operating): 1G, 5-55Hz

#### 4.1.4 Format specification

|             |      |        |             |             | -    | -        |    |      |       | - Se     | ector 01 |          |          |        |     |          |      | Secotr 02 |

|-------------|------|--------|-------------|-------------|------|----------|----|------|-------|----------|----------|----------|----------|--------|-----|----------|------|-----------|

| G<br>A<br>P | SYNC |        | I<br>A<br>M | G<br>A<br>P | SYNC | Al       | И1 | ID   | CRC   | GAP<br>2 | SYNC     | AM       | 2        | DATA   | CRC | GAP<br>2 | SYNC | GAP4      |

| 80          | 12   | 1      | 1           | 50          | 12   | 3        | 1  | 4    | 2     | 22       | 12       | 3        | 1        | 256    | 2   | 51       | 12   |           |

| 4 E         | 00   | C<br>2 | F           | 4 E         | 00   | *<br>A 1 | FE | (ID) | (CRC) | 4E       | 00       | *<br>A 1 | FB<br>F8 | (DATA) | CRC | 4 E      | 00   | 4E        |

<sup>\*....</sup> Missing clock is present.

Fig. 1-2 Format

One floppy disk has a memory capacity of 278KB. It is divided into blocks of 2KB each. Accordingly, a floppy disk has 139 blocks.

The floppy disk is used block by block in filing. Disk BASIC assigns one block for each 16 records, namely, one block for records 1 to 16 and another for records 17 to 32.

(One record consists of 128B. 16 records are 16x128=2048B, or 2KB.)

When a file requires a newblock, Disk BASIC secures for the file a block which has not been used on the floppy disk. At an erasure of a file, all the block having been used by the file are vacated for use by other files.

With the blocks used in this manner, the memory area on the floppy disk is utilized effectively.

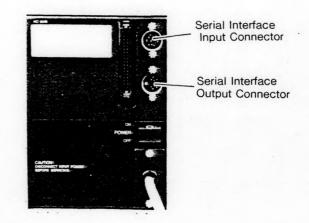

#### 4.1.5 Interface connector

Fig. 2-3 Interface Connector

(1) Serial Interface Input Connector

(a) Use

: This connector is used for data exchange between the TF-20 and the HX

-20 computer.

(b) Number of pins

: 6 pins

(c) Part number

: TCS0260-01-1101 (Hoshi Denki)

(d) Pin assignment

: Refer to Table 1-1 below.

Table 1-1 Pin Assignment of Serial Intertace Connector for HX-20.

| Pin No.    | Signal | Direction<br>(as viewed<br>from floppy) | Description                                                                                                                                                                     |  |  |

|------------|--------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1 RXS Out  |        | Out                                     | This signal output from the terminal floppy is connected to another terminal or HX-20 serial input.                                                                             |  |  |

| 2 PINS Ou  |        | Out                                     | This is the OR signal of PINC and DTRA of serial controller $\mu$ PD7201 inside. This signal is not used usually.                                                               |  |  |

| 3          | TXS In |                                         | This is a serial input signal to the terminal floppy from the HX-20.                                                                                                            |  |  |

| 4 POUTS In |        | lĥ                                      | This input signal is connected to the CTSA terminal of serial controller $\mu$ PD7201 inside via the line receiver. It means that a serial output at "HIGH" level is permitted. |  |  |

| 5          | GNDS   | _                                       | GND                                                                                                                                                                             |  |  |

#### (2) Serial Interface Output Connector

(a) Use

: This connector is used for data exchange between the TF-20 and the HX

-20 display controller or some other terminal.

It is an interface connector for the extension drive of the TF-20 (exclusive use

with HX-20).

(b) Number of pins

: 5 pins

(c) Part number

: TCSO250-01-1301

(d) Pin assignment

: Refer to Table 1-2 below.

**Table 1-2** Pin Assignment of Serial Interface Connector for HX-20 Display Controller

| Pin No.     | Signal   | Direction<br>(as viewed<br>from floppy) | Description                                                                                                                        |  |  |

|-------------|----------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1           | GNDC     |                                         | GND                                                                                                                                |  |  |

| 2 TXC Out   |          | Out                                     | This serial signal output from the terminal floppy is connected to another teminal (display controller) of the HX-20.              |  |  |

| 3           | 3 RXC In |                                         | When this input signal is at "LOW" level, a signal from the terminal floppy is output from RXS.                                    |  |  |

| 4 POUTC Out |          | Out                                     | This output signal functions the same way as the POUTS signal. (It is not use in this application.)                                |  |  |

| 5           | PINC     | In                                      | The OR signal of this signal and DTRA of the serial controller<br>µPD7201 is output at PINS. (It is not used in this application.) |  |  |

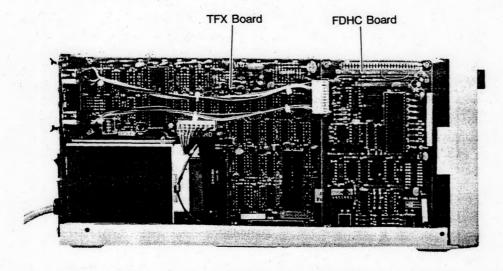

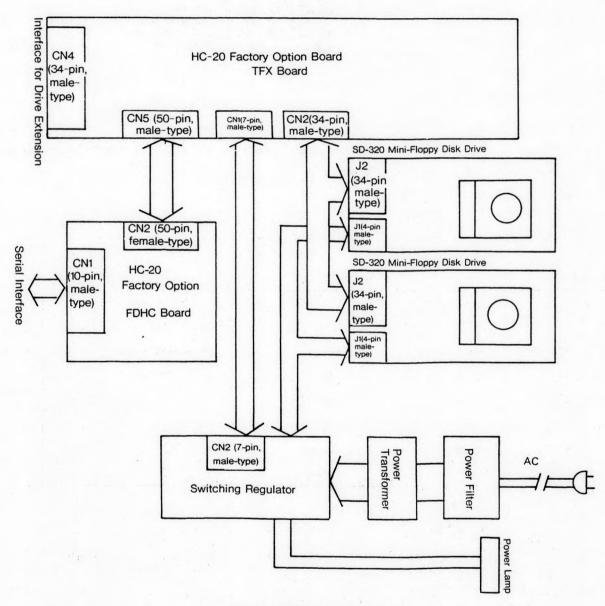

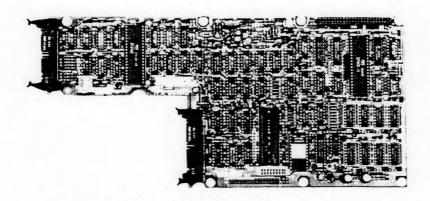

#### 4.1.6 Constitution of TF-20 (HX-20 Type Model)

The TF-20 (exclusive use with HX-20) consists of the TF-20 standard model section and the HX-20 factory option section. The HX-20 factory option comprises the FDHC board and the TFX board as shown in Fig. 1-3.

Fig. 1-3 Constitution of TF-20 (Exclusive Use with HX-20)

# 4.2 Principles of Operation

#### 4.2.1 General

This chapter provides descriptions of the signals at the various connectors of the TF-20 for exclusive use with the HX-20 and of the principles of operation of the floppy's electric circulits. For detailed description of the operation of the drive SD-320 and the power supply unit,refer to the chapter on the TF-20 (Standard Model) and the separate SD-320 Technical Manual.

#### 4.2.2 Block Diagram

Fig. 2-1 BlockDiagram

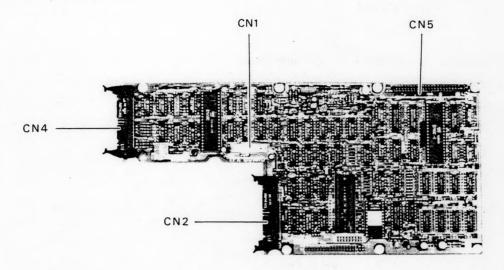

#### (1) TFX Board Connectors

1) CN1 connector

(a) Use : This connector is used to supply +5V and +12V from the switching

regulator board.

(b) Number of pins : 7 pins

(c) Part number : MOLEX 5275-07

(d) Pin assignment : Refer to Table 2-1 below.

Table 2-1 Pin Assignment of CN1 Connector

| Pin No. | Signal | Lead Wire Color | Use              |

|---------|--------|-----------------|------------------|

| 1       | GND    | Black           | Signal GND level |

| 2       | GND    | Black           | Signal GND level |

| 3       | GND    | Black           | Signal GND level |

| 4       | +5V    | Red             | +5V DC           |

| 5       | +5V    | Red             | +5V DC           |

| 6       | +12V   | Orange          | +12V DC          |

| 7       | +12V   | Orange          | +12V DC          |

2) CN2 connector

(a) Use

: This connector is used to transfer the signals of floppy disk drive

(b) Number of pins

: 34 pins

(c) part number

: DDK FRC2-AA34-30S

(d) Pin assignment

: Refer to Table 2-2 below.

# Table 2-2 Pin Assignment of CN2 connector

| CN2<br>Connector<br>Signal<br>Pin No. | Signal<br>Pin No. | Signal | Direc-<br>tion | Description                                                                                                                                                                                                                             |

|---------------------------------------|-------------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                     |                   | NC     |                |                                                                                                                                                                                                                                         |

| 4                                     | 4                 | HOLD   | In             | The HEAD LOAD signal at Logic "O" causes the read/write head to be loaded on the disk. (Pin 5 and Pin 6 of the DIP switch SS1 in the SD 320 mini disk drive can make head loading possible at a DRIVE SELECT signal.)                   |

| 6 6 DS3                               |                   | DS3    | In             | This is the DRIVE SELECT 3 signal. Up to 4 mini disk drives can be connected in a daisy chain by the switching of the DRIVE SELECT signals. (The drive selection is made by pin 4 of the DIP switch SS1 on the SD-320 mini disk drive.) |

| 8                                     | 8                 | ĪDX    | Out            | The INDEX signal causes a Logic "0" pulse to be generated at each complete revolution of the floppy disk. The trailing edge of Logic "1" to Logic "0" indicates the beginning of data on the specified track.                           |

| 10                                    | 10 10 DSO         |        | ln             | This is the DRIVE SELECT 0 siganl. (The drive selection is made by pin 1 of the DIP switch SS1 on the SD-320 mini disk drive.)                                                                                                          |

| 12                                    | 12                | DS1    | ln             | This is the DRIVE SELECT 1 signal.  (The drive selection is made by pin 2 of the DIP switch SS1 on the SD-320 mini disk drive.)                                                                                                         |

| 14 14                                 |                   | DS2    | In             | This is the DRIVE SELECT 2 signal.  Up to 4 mini disk drives can be connected in a daisy chain.  (The drive selection is made by pin 3 of the DIP switch SS1 on the SD-320 mini disk drive.)                                            |

| 16                                    | 16                | MON    | In ·           | The MOTOR ON signal at Logic "0" causes the disk drive motor to start.                                                                                                                                                                  |

| 18                                    | 18                | DRTN   | ln :           | The DIRECTION signal determines the moving direction of the voice coil motor.  The motor moves from track 00 to track 39 at Logic "0" or from track 39 to track 00 at Logic "1".                                                        |

## 2) CN2 connector

(a) Use : This connector is used to transfer the signals of floppy disk drive

(b) Number of pins : 34 pins

(c) part number : DDK FRC2-AA34-30S

(d) Pin assignment : Refer to Table 2-2 below.

## Table 2-2 Pin Assignment of CN2 connector

| CN2<br>Connector<br>Signal<br>Pin No. | Signal<br>Pin No. | Signal | Direc-<br>tion | Description                                                                                                                                                                                                                             |

|---------------------------------------|-------------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                     |                   | NC     |                |                                                                                                                                                                                                                                         |

| 4                                     | 4                 | HOLD   | In             | The HEAD LOAD signal at Logic "O" causes the read/write head to be loaded on the disk. (Pin 5 and Pin 6 of the DIP switch SS1 in the SD 320 mini disk drive can make head loading possible at a DRIVE SELECT signal.)                   |

| 6 6 DS3                               |                   | DS3    | In             | This is the DRIVE SELECT 3 signal. Up to 4 mini disk drives can be connected in a daisy chain by the switching of the DRIVE SELECT signals. (The drive selection is made by pin 4 of the DIP switch SS1 on the SD-320 mini disk drive.) |

| 8                                     | 8                 | ĪDX    | Out            | The INDEX signal causes a Logic "0" pulse to be generated at each complete revolution of the floppy disk. The trailing edge of Logic "1" to Logic "0" indicates the beginning of data on the specified track.                           |

| 10                                    | 10 10 DSO         |        | In             | This is the DRIVE SELECT 0 siganl. (The drive selection is made by pin 1 of the DIP switch SS1 on the SD-320 mini disk drive.)                                                                                                          |

| 12                                    | 12                | DS1    | In             | This is the DRIVE SELECT 1 signal. (The drive selection is made by pin 2 of the DIP switch SS1 on the SD-320 mini disk drive.)                                                                                                          |

| 14                                    | 14                | DS2    | In             | This is the DRIVE SELECT 2 signal.  Up to 4 mini disk drives can be connected in a daisy chain.  (The drive selection is made by pin 3 of the DIP switch SS1 on the SD-320 mini disk drive.)                                            |

| 16                                    | 16                | MON    | In             | The MOTOR ON signal at Logic "0" causes the disk drive motor to start.                                                                                                                                                                  |

| 18                                    | 18                | DRTN   | In             | The DIRECTION signal determines the moving direction of the voice coil motor.  The motor moves from track 00 to track 39 at Logic "0" or from track 39 to track 00 at Logic "1".                                                        |

| CN2<br>Connector<br>Signal<br>Pin No. | Signal<br>Pin No.    | Signal | Direc-<br>tion | Description                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------|----------------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20 20                                 |                      | STP    | In             | When a pulse is input to the STEP signal line, the voice coil motor, which controls the position of the read/write head, moves in the direction specified by the DRTN signal.  When the WRITE GATE signal is at Logic "0", the STEP signal is inhibited.                                                                          |

| 22 22                                 |                      | WTD    | In             | The WRITE DATA signal line transfers data to be written into the disk.  When the input pulse falls from Logic "0", the write "0", the write current flows in the opposite direction and enters the read/write head, causing a change in the magnetic flux.  This signal is valid only when the WRITE GATE signal is at Logic "0". |

| 24 24                                 |                      | WTG    | In             | The WRITE GATE signal controls both Read Data and Write Data signals. When this signal is at Logic "0", the Write Data is valid, whereas when it is at Logic "1", the Read Data is valid.                                                                                                                                         |

| 26                                    | 26 26 TKOO           |        | Out            | The TRACK 00 signal becomes Logic "0" when the read/write head is at the track 00 position.                                                                                                                                                                                                                                       |

| 28                                    | 28 28                |        | Out            | The WRITE PROTECT signal notifies the host of the disk attached with a write protect label. It becomes Logic "0" when the disk has a write protect label attached.                                                                                                                                                                |

| 30 30                                 |                      | RDD    | Out            | The READ DATA signal causes a pulse string of raw data to be output from the read circuit.  Normally, this signal becomes Logic "0" when the inversion of magnetization exists on the disk at logic level "1".                                                                                                                    |

| 32                                    | 32                   | SSL    | In             | The SIDE SELECT signal is used to select the upper or the lower read/write head.  Side 1 (upper head) is selected at Logic "0", and Side 0 (lower head) at Logic "1".                                                                                                                                                             |

| 34                                    | 34                   | RDY    | Out            | The READY signal becomes Logic "0" when the power is turned on and a disk loaded rotates normally (INDEX pulse: 4 pulses).                                                                                                                                                                                                        |

| 1 add<br><sub>1</sub> pin<br>33       | 1 add<br>, pin<br>33 | GND    |                | Twisted Pair Return signal GND Level.                                                                                                                                                                                                                                                                                             |

3) CN4 connector

(a) Use

: Connector for daisy chain

(b) Number of pins

: 34 pins

(c) Part number

: FRC2-C34U3-OL DDK

(d) Pin assignment

: Refer to Table 2-2

4) CN5 connector

(a) Use

: This connector is used to transfer the signals of the TFX board and

the FDHC board.

(b) Number of pins : 50 pins, male-type

(c) Part number

: Honda HKP-50MS3A

(d) Pin assignment

: Refer to Table 2-3

Table 2-3 Pin Assignment of CN5 Connector

| Pin No. | Signal    | Direction | Description                                                      |

|---------|-----------|-----------|------------------------------------------------------------------|

| 1       | ADDRESS 0 | Out       | These signals represent bits of ADDRESS signal line No. 0 to 15. |

| 16      | 15        |           |                                                                  |

| 17      | DATA 7    | In/Out    | These signals represent bits of DATA signal line                 |

| 1       | 1         |           | No. 0 to 7.                                                      |

| 24      | 0         |           |                                                                  |

| 25      | GND       |           | Twisted Pair Return signal GND level                             |

| 26      | +5V       |           | +5VDC                                                            |

| 27      | GND       |           | Twisted Pair Return signal GND level                             |

| 28      | ĪNT       | ln :      | Interrupt signal "Active LOW"                                    |

| 29      | GND       |           | Twisted Pair Return signal GND level                             |

| 30      | MI        | Out       | Machine Cycle "Active LOW"                                       |

| 31      | GND       |           | Twisted Pair Return signal GND level                             |

| 32      | IORQ      | Out       | I/O Request signal "Active LOW"                                  |

| 33      | GND       |           | Twisted Pair Return signal GND level                             |

| 34      | MERQ      | Out       | Memory Request signal "Active LOW"                               |

| 35      | GND       |           | Twisted Pair Return signal GND level                             |

| 36      | RD        | Out .     | Data Read signal "Active LOW"                                    |

| 37      | GND       |           | Twisted Pair Return signal GND level                             |

| 38      | WR        | Out       | Data Write signal "Active LOW"                                   |

| 39      | GND       |           | Twisted Pair Return signal GND level                             |

| 40      | RESET     | Out       | Reset at "HIGH"                                                  |

| 41      | GND       |           | Twisted Pair Return signal GND level                             |

| 42      | φ         | Out       | Clock Pulse                                                      |

| 43 | +5V  | Out |         |  |

|----|------|-----|---------|--|

| 44 | +5V  | Out | +5V DC  |  |

| 45 | +5V  | Out |         |  |

| 46 |      |     |         |  |

| 47 | +12V | Out | 1407.00 |  |

| 48 | +12V | Out | +12V DC |  |

| 49 | -12V | Out | 401/ 00 |  |

| 50 | -12V | Out | -12V DC |  |

Market Company

The second second

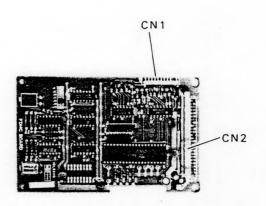

#### (2) FDHC Board Connectors

1) CN1 connector

(a) Use : This connector is used to transfer data from the FDHC board and the

HX-20 serial interface or HX-20 display controller serial

interface connector.

(b) Number of pains : 10 pins,male-type

(c) Part number : MOLEX 5049-10A

(d) pin assignment : Refer to Table 2-4 below.

Table 2-4 Pin Assignment of CNI Connector

| Pin No.    | Signal | Direction<br>(as viewed<br>from floppy) | Description                                                                                                                                                                 |

|------------|--------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | RXS    | Out                                     | This signal output from the terminal floppy is connected to another terminal or HX-20 serial input.                                                                         |

| 2 PINS Out |        | Out                                     | This is the OR signal of PINC and DTRA of serial controller $\mu$ PD7201 inside. This signal is not used usually.                                                           |

| 3          | TXS    | In                                      | This is a serial input signal to the terminal floppy from the HX-20.                                                                                                        |

| 4 POUTS    |        | In                                      | This input signal is connected to the CTSA terminal of serial controller μ PD7201 inside via the line receiver. In means that a serial output at "HIGH" level is permitted. |

| 5          | GNDS   | _                                       | GND                                                                                                                                                                         |

| 6          | GNDC   |                                         | GND                                                                                                                                                                         |

| 7          | POUTC  | Out                                     | This output signal functions the same way as the POUTS signal. (It is used in this application.)                                                                            |

| 8 TXC      |        | Out                                     | This serial signal output from the terminal floppy is connected to another terminal (display controller) of the HX-20.                                                      |

| 9 PINC In  |        | In                                      | The OR signal of this signal and DATA of the serial controller μPD7201 is output at PINS. (It is not used in this application)                                              |

| 10 RXC In  |        | In                                      | When this input signal is at "LOW" level, a signal from the terminal floppy is output from RXS.                                                                             |

#### 2) CN2 connector

(a) Use

: This connector is used to transfer the signals of the TFX board and

the FDHC board.

(b) Number of pains

: 50 pins,male-type

(c) Part number

: HKD-50FD2-3A

(d) pin assignment

: Refer to Table 2-5 below.

Tab. 2-5 Pin Assignment of CN2 connector

| Pin No. | Signal   | Direction | Description                                                     |

|---------|----------|-----------|-----------------------------------------------------------------|

| 1       | ADRESS 0 | IN        | These signals represent bits of ADDRESS signal line Nos. 0 to 7 |

| 2       | 1        | IN        |                                                                 |

| 3       | 2        | IN        |                                                                 |

| 4       | 3        | IN        |                                                                 |

| 5       | 4        | IN        |                                                                 |

| 6       | 5        | IN        |                                                                 |

| 7       | 6        | IN        |                                                                 |

| 8       | 7        | IN        |                                                                 |

| 9       | NC       |           |                                                                 |

| 10      | NC       |           |                                                                 |

| 11      | NC       |           |                                                                 |

| 12      | NC       |           |                                                                 |

| 13      | NC       |           |                                                                 |

| 14      | NC       |           |                                                                 |

| 15      | NC       |           |                                                                 |

| 16      | NC       |           |                                                                 |

| 17      | DATA 7   | In/Out    | These signals represent bits of DATA signal line Nots. 0 to 7.  |

| 18      | 6        | OUT       |                                                                 |

| 19      | 5        | In/Out    |                                                                 |