JK82 CPU III

Rev. 2.0.

# TECHNISCHE BESCHREIBUNG

#### Bestellnummern:

| TIJ-Z-1250   | CPU III  | unbestück | < t    |       |     |             |

|--------------|----------|-----------|--------|-------|-----|-------------|

| TIJ-Z-1252   | CPU III  | bestückt  | (64K,  | 4MHz) |     |             |

| TIJ-Z-1253   | CPU III  | bestückt  | (64K,  | 5MHz, | DMA | selektiert) |

| TIJ-Z-1254   | CPU III  | bestückt  | (64K,  | 6МHz, | DMA | selektiert) |

| TIJ-Z-1255 · | CPU III  | bestückt  | (256K, | 4MHz) |     |             |

| TIJ-Z-1256   | CPU III  | bestückt  | (256K, | 5MHz, | DMA | selektient) |

| TIJ-Z-1257   | CPU III  | bestückt  | (256K, | 6MHz, | DMA | selektiert) |

| TIJ-Z-1258   | PROM/PAI | Satz      |        | ·     |     |             |

Ihr autorisierter Händler: \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

(C) 1984 by Janich & Klass Wuppertal

14.07.84

# Inhaltsverzeichnis:

| 1.1                                       | Allgemeine Beschreibung:<br>Jumperstellungen:                                                                                                                                                      | Se i<br>Se i                           |                            | 3<br>4                     |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------|----------------------------|

| 2.1.<br>2.2.<br>2.3.<br>2.4.              | Speicherverwaltung: Banking: Adreßumrechnung: Schaltungsbeschreibung der Adreßumrechnung: Laden des Bank-Description-Registers: Aufbau eines Bank-Description-Vektors:                             | Sei<br>Sei<br>Sei<br>Sei<br>Sei        | te<br>te<br>te<br>te       | 5<br>6<br>9<br>10          |

| 3.1.                                      | Inter-Bank-Move:<br>Inter-Bank-Move mit DMA oder LDIR:<br>RD/WR-Steuerung beim DMA-Transfer:<br>RD/WR-Steuerung beim LDIR-Transfer:                                                                | Sei<br>Sei<br>Sei<br>Sei               | te<br>te                   | 12<br>12                   |

| 4.                                        | Beschaltung des CTC:                                                                                                                                                                               | Sei                                    | te                         | 13                         |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5 | I/O-Portbelegung: Die I/O-Ports im einzelnen: Bank-Latche CWB, TSB und TDB: BOOT/LDIR-Flipflop: Basisadresse des Common: Bank-Description-Vektor: (siehe 2.5.) Set Watch Latch: Read Watch Output: | Sei<br>Sei<br>Sei<br>Sei<br>Sei<br>Sei | te<br>te<br>te<br>te<br>te | 14<br>14<br>14<br>14<br>14 |

|                                           | Bussteuerung:<br>Inhalt des PROMs 1208:                                                                                                                                                            | Se i<br>Se i                           |                            |                            |

| 7.1.<br>7.2.                              | Internes Memory:<br>Dynamisches RAM:<br>EPROM der CPU III:<br>Speicheraufteilung:                                                                                                                  | Sei<br>Sei<br>Sei                      | te<br>te                   | 16<br>16                   |

|                                           | Schaltungsbesonderheiten:<br>RESET-Generierung:<br>CMOS-Bestückung:<br>Takterzeugung:                                                                                                              | Sei<br>Sei<br>Sei                      | te<br>te                   | 18<br>18                   |

| 9.                                        | Beispielsoftware:                                                                                                                                                                                  | Sei                                    | te                         | 19                         |

| 10.                                       | Busbelegung:                                                                                                                                                                                       | Sei                                    | te                         | 27                         |

| 11.                                       | Stückliste:                                                                                                                                                                                        | Sei                                    | te                         | 28                         |

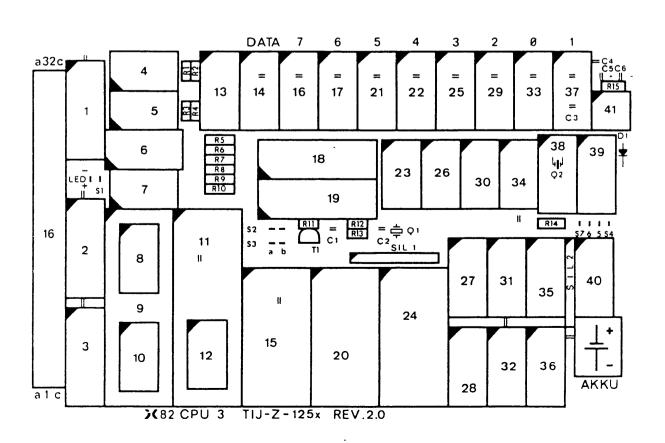

| 12.                                       | Bestückungsdruck:                                                                                                                                                                                  | Sei                                    | te                         | 28                         |

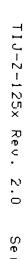

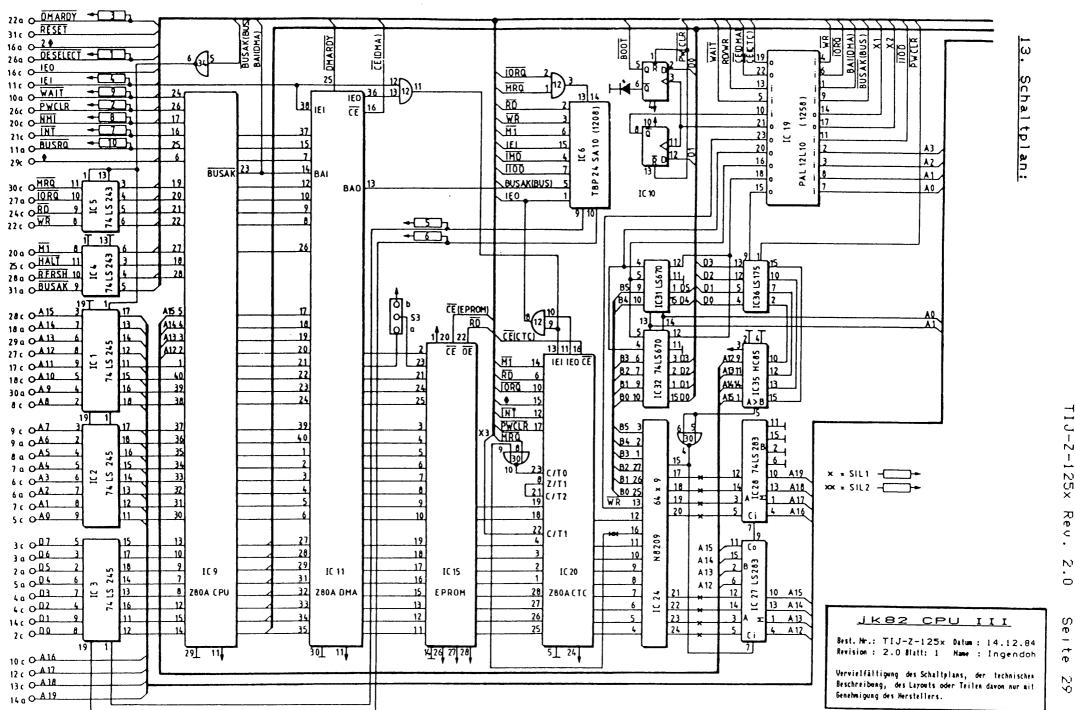

| 13.                                       | Schaltplan:                                                                                                                                                                                        | Sei                                    | te                         | 29                         |

## 1. Allgemeine Beschreibung:

Die jk82 CPU III findet ihre Anwendung in größeren Z80-Multiprozessorsystemen, die bereits mit einigen Slave-CPUs oder intelligenten I/O-Karten ausgerüstet sind. Sie besitzt eine Speicherverwaltung über 1MByte mit Adreßumrechnung, 64KB oder 256KB RAM, einen Z80-DMA, eine Z80-CTC sowie eine akkugepufferte Echtzeituhr.

Die CPU III erzeugt vier zusätzliche Adressen (A16 - A19), die den Adreßraum auf 1MByte erweitern. Es wird eine Umrechnung vom logischen Adreßraum in den physikalischen Adreßraum vorgenommen. Logisch existieren 64 Banks mit einer programmierbaren Größe von 0 - 60K (in 4K-Schritten). Die Basisadresse einer Bank wird durch die Hardware-Adreßumrechnung jeweils so verschoben, daß kein einziges Byte verloren geht.

Je nach Bestückung finden 64KB (4164) oder 256KB (41256) dynamisches RAM auf der Platine Platz. Die Refresh-Adresse ist 8Bit breit. Ein unter Software-Kontrolle ausblendbares EPROM von 2KB bis 16KB Größe ermöglicht BOOT-Betrieb.

Auf der Karte befindet sich ein Z80A-DMA Baustein, der einen schnellen Inter-Bank-Move ausführen kann. Auch schnelle I/O-Bausteine Können mit dem DMA bedient werden. Der interne DMA besitzt immer die höchste Priorität.

Zusätzliche Logik ermöglicht den Inter-Bank-Move mittels LDIR/LDDR-Befehlen. Dabei ist die Programmierung ebenso transparent, wie bei der Verwendung des DMA.

Eine Echtzeituhr hat ebenfalls Platz gefunden. Die Uhr zeigt das Jahr, das Datum, den Wochentag sowie die Zeit in Stunden, Minuten und Sekunden. Zum Lieferumfang gehören Source-Listings zum Setzen und Lesen der Uhr. über einen Kanal des 280-CTC kann die Uhr auch Interrupts auslösen.

Die technischen Daten in Stichworten:

- effektive Speicherverwaltung von max. 1MByte Adresraum

- 64KByte oder 256KByte Speicher auf der Karte

- Z80-DMA für schnellen Datentransfer

- Inter-Bank-Move mittels LDIR/LDDR-Befehlen

- Echtzeituhr mit Akkupufferung

- Einfach-Europakarte mit ECB-kompatiblen jk82-Bus

- Stromaufnahme typisch: 5V, 1,2A

#### 1.1 Jumperstellungen:

#### Jumper Si:

Der Jumper S1 schließt die BAI-BAO-Dasy-Chain. Dies ist erforderlich, falls mehr als ein zusätzlicher DMA im System betrieben wird. Der DMA der CPU III ist nicht in die Daisy-Chain eingebunden. Er liegt zwischen der CPU und der Busleitung BUSAK.

Im Auslieferzustand ist der Jumper offen.

# Jumper S2:

Die Stellung "a" ist erforderlich, falls die Karte mit RAMs des Typs 4164 bestückt ist. Die Stellung "b" ist erforderlich, falls die Karte mit RAMs des Typs 41256 bestückt ist.

Auslieferzustand ist "a"

#### Jumper S3:

Die Stellung "a" ist erforderlich, falls die Karte mit einem EPROM des Typs 2732, 2764 bestückt ist. Die Stellung "b" ist erforderlich, falls die Karte mit einem EPROM des Typs 2716 bestückt ist.

Auslieferzustand ist "a"

### Jumper SA4 - SA7:

Die Basisadresse wird mit den Jumpern SA7 bis SA3 eingestellt. Dabei repräsentiert ein gesetzter Jumper eine logische 0. Die Adresse 20H ist also wie folgt einzustellen:

SA7 SA6 SA5 SA4

11:1

Auslieferzustand!

## 2. Speicherverwaltung:

Viele neuere Betriebssysteme (CP/M PLUS) für 8Bit Prozessoren sind sogenannte "Banking" Systeme. Sie setzen das Vorhandensein mehrerer Speicherbanks von (64KB sowie einer Hardware, die das Umschalten zwischen einzelnen Banks gestattet, voraus.

Die jk82 CPU III wurde speziell für derartige Betriebssysteme entwickelt.

#### 2.1. Banking:

Definition: Eine "Bank" ist ein Speicherbereich von K64KB, der von einem Programm aus in den Adreßbereich der CPU eingeblendet werden kann.

Definition: Als "Common" wird der Speicherbereich in einem Banking-System benannt, der außerhalb jeder Bank liegt.

Grundsätzlich kann eine Z80-CPU nur einen Adreßraum von 64KB Größe adressieren. Nun könnte ein System aber beispielsweise 8 Speicherbanks mit je 48KB besitzen, von denen immer jeweils eine in den Adreßraum der CPU eingeblendet wird. Das folgende Bild zeigt dies schematisch.

| I I I I I I I I I I I I I I I I I I I |              |        |            |

|---------------------------------------|--------------|--------|------------|

| *<br>************<br>*                | ********     | ****** |            |

|                                       | <del>*</del> |        | *          |

| I                                     | I            |        | ı          |

| I Bank 1 I                            | I Bank 2 I   |        | I Bank 8 I |

| I 48 K I                              | I 48 K I     |        | I 48 K I   |

| I I                                   | I I          |        | II         |

|                                       |              |        |            |

Die 16KB Common-Memory kann die CPU immer adressieren. Dort steht das Betriebssystem und auch das Unterprogramm zur Umschaltung auf eine andere Bank. Die einzelnen Banks können nun spezielle Programme (Multi-Tasking) oder Dateien enthalten. Müssen übergabeparameter zwischen den Banks ausgetauscht werden, so kann das in den oberen 16KB des Common-Memory geschehen. Es wäre jedoch auch denkbar, daß ein DMA-Baustein einen "Inter-Bank-Move", also einen direkten Datentransfer zwischen zwei Banks durchführt.

Es tritt nun ein Problem auf. Unter der Voraussetzung, daß der Speicher mit RAMs vom Typ 4164 mit 64Kx1 aufgebaut wird, gehen jeder, außer der Bank O, 16KB Speicherbereich verloren, da die einzelnen 64KB Blöcke adreßmäßig hintereinander liegen. Bei 5 Banks sind somit schon 64KB Speicher nicht mehr adressierbar.

Um dieses Problem zu umgehen, wurde auf der CPU III eine im folgenden beschriebene Adreßumrechnung auf Hardware-Ebene vorgenommen.

# 2.2. Adresumrechnung:

Die grundsätzliche überlegung zeigt das folgende Bild:

| 00000СН          | logisch | ADRESSRAUM | physikalisch |

|------------------|---------|------------|--------------|

|                  | BANK O  |            | BANK 0       |

| 010000 H         | COMMON  |            | COMMON       |

|                  | BANK 1  |            | BANK 1       |

| 020000 H         | COMMON  |            |              |

|                  | BANK 2  |            | BANK 2       |

|                  |         |            |              |

| 030000Н          | COMMON  |            | BANK 3       |

|                  | BANK 3  |            | BANK 4       |

| 040000 H         | COMMON  |            |              |

| 3 <b>50000 H</b> | BANK 4  |            |              |

| 050000Н          | COMMON  |            |              |

Der logische Adreßraum wird mit einer Abbildungsfunktion, dargestellt durch die Pfeile, auf den physikalischen Adreßraum abgebildet. Dabei wird der Common-Bereich nur einmal in den physikalischen Adrefraum abgebildet. Das Common-Memory ist normalerweise am oberen Ende des 64KB Adregraums der CPU zu finden.

Größe des eingesparten Speicherraums ist nach folgender Formel zu berechnen:

A = Anzahl der Banks

B = Speichergröße des Common-Memories (KB)

C = eingesparter Speicherraum (KB)

$C = (A - 1) \times B$

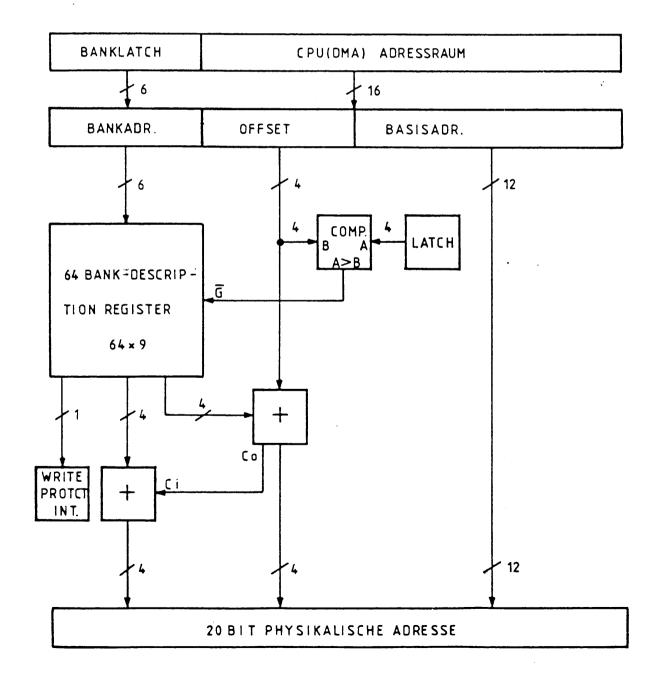

Das folgende Bild zeigt die prinzipielle Schaltung der Adreßumrechnung auf der CPU III.

Der 16Bit breite Adreßbus der CPU wird in zwei Teile aufgeteilt. Die unteren 12Bit werden Basisadresse genannt, die oberen 4Bit werden Offset genannt. Zusätzlich existiert ein "Bank-Latch" in dem die Bankadresse gespeichert ist. Die Bankadresse ist 6Bit breit. Es können also maximal 64 Banks adressiert werden.

Das Bank-Latch ist von der CPU über I/O-Befehle zu laden. Die detaillierte Funktion ist der Schaltungsbeschreibung zu entnehmen.

Die Bankadresse, der Offset und die Basisadresse stellen zusammen die <u>logische Adresse</u> der CPU dar.

Diese wird in der folgenden Harware in eine <u>physikalische Adresse</u> umgewandelt.

Die logische Basisadresse ist gleich der physikalischen Basisadresse.

Der Offset zerschneidet den logischen Adreßraum in 4KB große Kacheln.

Die Bankadresse führt auf ein bipolares RAM, das Bank-Description-Register. Dieses RAM ist durch ein Programm beschreibbar. Die Bankadresse adressiert nun eins der 64 9Bit breiten Worte dieses RAMs.

Die unteren 8Bit dieses Wortes geben die **Verschiebung** der Basis-adresse einer Bank in 4KB Schritten im physikalischen Adreßraum an. Die folgende Additionsstufe addiert den jeweiligen Offset dazu, so daß die Abbildung der logischen in die physikalische Adresse innerhalb einer Bank **linear** verläuft.

Das neunte Bit ist als Speicherzugriffsindikator definiert. Ist es 0, so erzeugt jeder Speicherzugriff auf diese Bank ein Triggersignalfür den CTC.

Im obigen Bild ist noch ein Komparator zu finden, der den Wert des Latches mit der Offsetadresse vergleicht. In dem Latch stehen die oberen 4Bit der unteren Adresse des Common-Bereichs. Ist die Offsetadresse größer oder gleich diesem Wert, so befindet sich die CPU im Common-Memory. Das Bank-Description-Register wird gesperrt, (die Ausgänge werden hier zu logisch 0 angenommen) und die unteren 16Bit der physikalischen Adresse sind gleich der Logischen. Die oberen 4Bit sind dann immer logisch 0. Die CPU kann also die Page 0 linear adressieren.

Festzuhalten ist, daß der logische größer als der physikalische Adreßraum ist.

# 2.3. Schaltungsbeschreibung der Adresumrechnung:

Die ICs 31 und 32 (siehe Schaltplan) stellen an den Ausgängen BO bis B5 die jeweilige Bankadresse zur Verfügung. Die Erzeugung dieser Bankadresse ist dem Abschnitt Inter-Bank-Move zu entnehmen.

Die 6Bit breite Bankadresse liegt an den Adreßleitungen des 64x9 bipolaren RAMs IC24. Die unteren 8 Datenausgänge führen auf die Addierer IC27 und IC28. Diese addieren das im RAM gespeicherte Wort zu den oberen 4 Adreßbits der CPU oder des DMA um daraus die Adressen A12 bis A19 zu bilden.

Pin 15 des bipolaren RAMs ist der CE. Ist dieses Signal High, so sind alle Ausgänge ebenfalls High. Das IC27 bekommt am Anschluß "Carry In" ebenfalls ein High-Signal. IC27 bildet dann die Summe S = B + FH + 1. Die Summenausgänge nehmen die Werte der B-Inputs an, zusätzlich wird "Carry Out" High. Das IC28 hat dann alle Ausgänge auf Low. Der Adreßbereich der CPU wird linear auf den Bus geführt und die Obergruppenadressen A16 - A19 sind Low.

Dieser Fall tritt immer dann ein, wenn der Ausgang A>B des IC36 Low ist. Nach PWCLR ist das immer der Fall, da die Ausgänge des IC36 alle Low sind. Nach dem Laden des Latches IC36 mit der unteren Basisadresse des Common-Bereiches wird das Bank-Description-Register nur gesperrt, falls die CPU oder der DMA im Common-Bereich arbeiten.

Im BOOT-Betrieb ist die Adresumrechnung in den unteren 4KB ohne Bedeutung, da das EPROM die Adressen A12 bis A19 nicht zur Dekodierung verwendet. Im BOOT-Betrieb sollten die Latche IC31 und IC32 definiert geladen werden, so das die CPU nach dem BOOT auf einer definierten Bank arbeitet. Dies kann aber auch nach dem Laden des Betriebssystems geschehen, falls das entsprechende Programm im Common-Memory steht.

Werden SKB EPROMs verwendet, so ist darauf zu achten, daß die oberen 4KB durch die Adresse A12 selektiert werden. Diese Adresse führt über die Adreßumrechnung. In den unteren 4KB des BOOT-EPROMs muß also das Programm zum Laden des Bank-Description-RAMs liegen.

## 2.4. Laden des Bank-Description-Registers:

Die ICs 31 und 32 stellen zusammen 4 einzelne 6Bit Latches dar. Sie werden im Kapitel "Inter-Bank-Move" noch ausführlich beschrieben.

Das Register CWB (CPU-Work-Bank) wird zur Adressierung des Bank-Description-Registers IC24 benutzt.

Es hält somit die Adresse des zu schreibenden Bank-Description-Vektors. Dieser Vektor wird mit einem I/O-Befehl geladen (s. I/O-Portbelegung) Man beachte, daß die Datenspeicherung in diesem RAM invertiert erfolgt.

Es existieren zwei Ports. Der Port mit A0 = 0 setzt das neunte Bit des RAMs auf 1, der Port mit A0 = 1 setzt das Bit auf 0, so daß der CTC mit jedem Speicherzugriff auf diese Bank getriggert wird. Eine sinnvolle Verwendung dieses Bits ist noch offen.

Das Laden des Vektors kann nur aus dem Common-Memory heraus erfolgen. Das 64x9 RAM muß ein aktives CE-Signal (Pin 15) vor dem Write-Zugriff bekommen. Dies kann beim Beschreiben der Banks nur erfolgen, falls der Ausgang A>B des IC35 High wird. Hier wird folgende Eigenschaft der Z80-CPU ausgenutzt:

Bei einem indirekten OUT-Befehl wird der Inhalt des Registers B auf die obere Hälfte des Adreßbus gelegt. Ist diese O und ist der Inhalt des Latches IC36 ungleich O, so wird während des Schreibzugriffs auf das bipolare RAM das Signal A>B des IC35 aktiv. Es wird also das geforderte CE-Signal erzeugt.

Das Laden eines Bank-Description-Registers muß mit einem indirekten OUT-Befehl aus dem Common-Memory heraus erfolgen, wobei der Inhalt des CPU-Registers B O sein muß.

Im BOOT-Betrieb sollte mindestens die Bank O konfiguriert worden sein. D.h. in diesem Fall, daß der Vektor der Bank O auch den Wert O besitzen muß. Außerdem muß die untere Adresse des Common-Bereichs definiert geladen werden. Sie muß wie bereits erwähnt, ungleich O sein.

# 2.5. Aufbau eines Bank-Description-Vektors:

Der zu ladende Vektor stellt den invertierten Wert der oberen 8Bits der Basisadresse einer bestimmten Bank im physikalischen Speicherbereich dar.

| ** | **** | *** | **** | ***          | **** | *** | **** | *** | **** | *** | **** | *** | **** | *** | **** | <del>: * *</del> |

|----|------|-----|------|--------------|------|-----|------|-----|------|-----|------|-----|------|-----|------|------------------|

| ×  |      | *   |      | *            |      | *   |      | ×   |      | *   |      | *   |      | ×   |      | *                |

| ×  | A19  | *   | A18  | ×            | A17  | *   | A16  | ×   | A15  | *   | A14  | ×   | A13  | *   | A12  | *                |

| *  |      | ×   |      | *            |      | *   |      | *   |      | *   |      | *   |      | *   |      | *                |

| ** | **** | *** | **** | ***          | **** | *** | **** | *** | **** | *** | **** | *** | **** | *** | **** | <del>* * *</del> |

| ×  |      | *   |      | *            |      | *   |      | ×   |      | *   |      | *   |      | ×   |      | ×                |

| *  | D7   | ×   | D6   | *            | D5   | *   | D4   | ×   | DЗ   | ×   | D2   | *   | D1   | *   | DO   | ×                |

| ×  |      | ×   |      | *            |      | *   |      | *   |      | *   |      | *   |      | ×   |      | *                |

| ×× | **** | *** | **** | * * <b>*</b> | **** | *** | **** | *** | **** | *** | **** | **× | **** | *** | **** | <del>: * *</del> |

## 3. Inter-Bank-Move:

Sollen Daten zwischen zwei Banks transferiert werden, so bestehen im Prinzip zwei Möglichkeiten:

- 1) Die CPU kann die Daten aus einer Bank in reservierte Speicherbereiche des Common-Memories transferieren, die Bank wechseln und dann die Daten aus dem Common in die neue Bank transferieren.

- 2) Ein DMA-Baustein kann Daten direkt zwischen den Banks transferieren. Eine Lösung dazu wurde bereits auf der Address-Extension-Karte verwirklicht.

Die erste Möglichkeit ist zeitaufwendig. Der Transfer kann nur in Kleinen Teilen erfolgen, will man den dafür reservierten Speicherplatz im Common nicht zu groß werden lassen.

Daher fand die zweite Möglichkeit Anwendung. Die Schaltung der Address-Extension-Karte wurde auf der CPU III in modifizierter und erweiterter Form realisiert. Zusätzlich wurde noch die Möglichkeit eines Inter-Bank-Move mittels LDIR- oder LDDR-Befehlen geschaffen.

## 3.1. Inter-Bank-Move mit DMA oder LDIR:

Auf der Karte ist ein 4x6Bit Latch untergebracht. In diesem Latch wird die Bankadresse gespeichert.

- Latch 0: CWB (CPU-Work-Bank)

Enthält die Adresse der Bank, auf der die CPU gerade arbeitet. Ein externer DMA kann ebenfalls nur auf diese Bank zugreifen.

- Latch 1: TSB (Transfer-Source-Bank)

Enthält die Bank, von der der DMA oder die CPU mit einem LDIR/LDDR bei einem Inter-Bank-Move liest.

- Latch 2: TDB (Transfer-Destination-Bank)

Enthält die Bank, auf die der DMA oder die CPU mit einem

LDIR/LDDR bei einem Inter-Bank-Move schreibt.

Latch 3: nicht benutzt.

## 3.1.1. RD/WR-Steuerung beim DMA-Transfer:

Die Initialisierung des DMA ist im Programmbeispiel im Anhang nachzulesen. Zuerst müssen die Latche TSB und TDB geladen werden. Dann wird der DMA mittels eines OTIR-Befehls geladen.

Das RD/WR Flipflop IC26 steuert den Transfer. Mit jeder positiven Flanke des MRQ-Signals wechselt es seinen Zustand. Ein M1-Signal setzt es zurück. Bei einem Memory zu Memory Transfer mit dem DMA ist der erste Zugriff immer ein Lese- der zweite ein Schreibzugriff usw. Aus dem Timing eines OTIR ist ersichtlich, daß der Ausgang des RD/WR Flipflop beim ersten DMA-Zugriff, also beim Lesen, High ist. Dies gilt nur, falls der DMA mit einem OTIR initialisiert wird. Das PAL (1258) setzt dies jedoch voraus.

## 3.1.2. RD/WR-Steuerung beim LDIR-Transfer:

Ist der DMA auf der Karte nicht bestückt, so kann derselbe Transfer auch mit einem LDIR/LDDR-Befehl vorgenommen werden. Ein Programmbeispiel dazu befindet sich ebenfalls im Anhang. Das LDIR-Flipflop IC10 wird vor dem LDIR mit einem OUT-Befehl gesetzt. Das Flipflop wird nach dem LDIR wieder zurückgesetzt.

Es wird hier vorausgesetzt, daß der Code im Common-Bereich abgearbeitet wird. Erfolgt ein Interrupt während des LDIR, so darf die Service-Routine Keinesfalls außerhalb des Commons irgendeinen Speicherzugriff machen. Während das LDIR-Flipflop gesetzt ist, werden nämlich die Bank-Latche TSB und TDB abwechselnd selektiert. Nur im Common ist immer das CWB-Latch selektiert. Es ist zu empfehlen, die Interrupts vor Aufruf des Inter-Bank-Move Programmes zu sperren. Dies erscheint auch deshalb sinnvoll, da bei einem DMA-Transfer ebenfalls Keine Interrupts verarbeitet werden.

#### 4. Beschaltung des CTC:

Der Z80-CTC auf der CPU III kann mehrere Funktionen erfüllen. Die meisten Multi-Tasking oder Multi-User Betriebssysteme benötigen z.B. eine feste Interrupt-fähige Zeitbasis. Dieser Interrupt kann mit dem CTC-Baustein verwirklicht werden.

Der Triggereingang des Kanals 0 erhält mit jedem MRQ auf eine Bank, deren Vektor mit der höheren Adresse (s. I/O-Port Belegung) in das bipolare RAM geschrieben wurde, einen positiven Puls.

Der Triggereingang des Kanals 1 ist mit der Hardware-Uhr IC38 verbunden. Er erhält eine Frequenz von 32768Hz. Diese kann für Zeitsteuerungen herangezogen werden.

Der Triggereingang des Kanals 2 ist mit dem Ausgang des Kanals 1 verbunden um auch lange Zeiten im Sekundenbereich realisieren zu können.

#### 5. I/O-Portbelegung:

Die Basisadresse wird mit den Jumpern SA7 bis SA3 eingestellt. Dabei repräsentiert ein gesetzter Jumper eine logische O. Die Adresse 20H ist also wie folgt einzustellen:

SA7 SA6 SA5 SA4

X X X X 1 1 1 0 RD/WR DMA DMA-Controller

Auslieferzustand!

| A7 | A6 | A5 | Α4 | АЗ | A2 | Ai | A0 | RD/WR | Name | Funktion                        |

|----|----|----|----|----|----|----|----|-------|------|---------------------------------|

| X  | X  | X  | Х  | 0  | 0  | 0  | 0  | RD/WR | стсо | Kanal O des CTC                 |

| X  | ×  | X  | X  | 0  | 0  | 0  | 1  | RD/WR | CTC1 | Kanal 1 des CTC                 |

| X  | X  | X  | X  | 0  | 0  | 1  | 0  | RD/WR | CTC2 | Kanal 2 des CTC                 |

| X  | X  | X  | X  | 0  |    |    | 1  | RD/WR | стсз | Kanal 3 des CTC                 |

| ×  | ×  | ×  | ×  | 0  | 1  | 0  | 0  |       |      | nicht benutzt                   |

| X  | X  | X  | X  | 0  |    |    | 1  | WR    | TSB  | Transfer-Source-Bank            |

| X  |    |    |    | 0  |    |    |    | WR    | TDB  |                                 |

| X  | X  | ×  | ×  | 0  | 1  | 1  | 1  | WR    | CMB  | CPU-Work-Bank                   |

| X  |    |    |    | 1  |    |    | 0  |       | CFF  | Clock-Flip-Flop (BOOT and LDIR) |

| ×  | ×  | ×  | ×  | 1  | 0  | 0  | 1  | WR    | BAC  | Base-Address-Common             |

| X  | X  | Х  | X  | 1  | 0  | i  | 0  | WR    | BDV  | Bank-DescVek. (ohne Attribut)   |

| X  | X  | X  | X  | 1  | 0  | 1  |    | WR    | BDVA | Bank-DescVek. mit Attribut      |

| ×  | ×  | ×  | X  | 1  | 1  | 0  | 0  | WR    | SWL  | Set-Watch-Latch                 |

| X  |    |    |    | 1  |    | 0  | 1  | RD    | RWO  | Read-Watch-Output               |

|    |    |    |    |    |    |    |    |       |      |                                 |

#### 5.1. Die I/O-Ports im einzelnen:

#### 5.1.1. Bank-Latche CWB, TSB und TDB:

|     | D7                |      | D۵   |     | D5  |     | D4  |     | DЗ   |     | D2   |     | D1   |     | D0  |                  |

|-----|-------------------|------|------|-----|-----|-----|-----|-----|------|-----|------|-----|------|-----|-----|------------------|

| **; | ****              | **** | **** | *** | *** | *** | *** | *** | ***  | *** | **** | *** | ***  | *** | *** | ***              |

| ×   |                   | ×    |      | *   |     | *   |     | ×   |      | ×   |      | *   |      | *   |     | *                |

| ×   | ×                 | *    | ×    | ×   | B5  | *   | В4  | *   | В3   | *   | B2   | *   | B1   | ×   | B0  | *                |

| ×   |                   | *    |      | ×   |     | *   |     | *   |      | ×   |      | *   |      | *   |     | ×                |

| **; | <del>(</del> ***) | ***  | **** | *** | *** | *** | *** | *** | **** | *** | **** | *** | **** | *** | *** | * <del>* *</del> |

BO - B5 ist die Bankadresse.

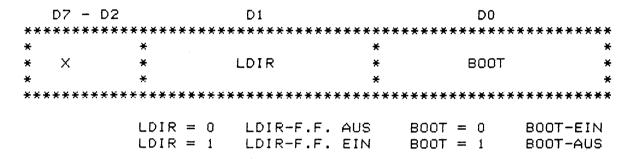

### 5.1.2. BOOT/LDIR-Flipflop:

# 5.1.3. Basisadresse des Common:

|     | D7              |     | D6       |      | D5   |     | D4   |      | DЗ   |     | D2   |     | D1   |     | DO   |    |

|-----|-----------------|-----|----------|------|------|-----|------|------|------|-----|------|-----|------|-----|------|----|

| *** | <del>(***</del> | *** | ****     | **** | ***  | *** | **** | ***  | **** | *** | **** | *** | **** | *** | **** | ×× |

| ×   |                 | *   |          | *    |      | *   |      | *    |      | *   |      | *   |      | ×   |      | *  |

| *   | ×               | *   | $\times$ | *    | ×    | *   | ×    | *    | A15  | *   | A14  | *   | A13  | ×   | A12  | *  |

| *   |                 | *   |          | *    |      | *   |      | *    |      | *   |      | ×   |      | ×   |      | *  |

| *** | ****            | *** | ****     | **** | **** | *** | **** | **** | **** | *** | **** | *** | **** | *** | **** | ** |

Die Basisadresse des Common-Memory setzt sich dann so zusammen:

A15 A14 A13 A12 X X X X

#### 5.1.4. Bank-Description-Vektor: (siehe 2.5.)

# 5.1.5. Set Watch Latch:

Die Bedienung der Harware-Uhr erfolgt seriell. Die Ausgänge des Watch-Latches IC39 sind nach einem PWCLR alle High (invertierte Ausgänge) und damit inaktiv.

Das Auslesen der Uhr geschieht relativ langsam. Aus dem Datenblatt der Uhr kann entnommen werden, daß die maximale Clockfrequenz von der Spannung des AKKUs abhängig ist. Diese beträgt mind. 2,2 Volt, so daß die Clockfrequenz max. 100kHz betragen darf. Die minimale Periodendauer beträgt demnach 10ys. Die Beispielsoftware arbeitet sicherheitshalber mit ca. 14ys.

- D3 erzeugt den invertierten Clock der Uhr, wobei zu beachten ist, daß die Clockperiodendauer 10ys nicht unterschreiten darf.

- D2 erzeugt den invertierten Chip-Select der Uhr.

- D1 steuert den Lese- oder Schreibzugriff. Dabei gilt:

0 = Lesen 1 = Schreiben

DO enthält den invertierten Wert des zu Schreibenden Bits.

#### 5.1.6. Read Watch Output:

Beim Lesen der Uhr ist die Zugriffszeit nach Clock von min. 5ys zu beachten. Das zu Lesende Bit wird auf die Datenleitung DO geschaltet.

#### Bussteuerung:

Die Steuerung der Daten- Adreß- und Steuerbustreiber wird im wesentlichen durch das PROM 1208 IC6 vorgenommen. Es wird nur aufgetaktet, falls ein gültiger Speicher- oder I/O-Zugriffszyklus stattfindet. Die Steuerung ist vollständig bezüglich aller vorkommender Zustände in einem Z8O-System. So wird z.B. der RETI immer an alle I/O-Bausteine gelegt, unabhängig davon, ob der OPCODE-Fetch aus dem internen oder dem externen Memory erfolgt.

#### 6.1. Inhalt des PROMs 1208:

| Adresse: | Ιr | nh a | al · | t : |    |   |   |   |   |   |   |   |   |   |   |   |

|----------|----|------|------|-----|----|---|---|---|---|---|---|---|---|---|---|---|

| 00       | F  | F    | F    | F   | F  | F | F | F | F | F | F | F | F | F | F | F |

| 10       | F  | F    | F    | F   | 1  | 1 | 1 | D | 3 | F | 3 | F | В | В | F | 8 |

| 20       | F  | F    | F    | F   | 9  | D | 9 | D | В | F | В | F | F | 3 | F | 3 |

| 30       | F  | F    | F    | F   | 9  | D | 9 | D | F | F | В | F | F | В | F | 3 |

| 40       | F  | F    | F    | F   | ·F | F | F | F | F | F | F | F | F | F | F | F |

| 50       | F  | F    | F    | F   | 1  | í | 1 | Đ | 3 | F | 3 | F | В | В | F | В |

| ક0       | F  | F    | F    | F   | 9  | D | 9 | D | В | F | В | F | F | 3 | F | 3 |

| 70       | F  | F    | F    | F   | 9  | D | 9 | D | F | F | В | F | F | F | F | 3 |

| 80       | F  | F    | F    | F   | F  | F | F | F | F | F | F | F | F | F | F | F |

| 90       | F  | F    | F    | F   | 1  | 1 | 1 | D | 3 | F | 3 | F | В | В | F | В |

| A0       | F  | F    | F    | F   | 9  | D | 9 | D | В | F | В | F | F | 3 | F | 3 |

| В0       | F  | F    | F    | F   | 9  | D | 9 | D | F | F | В | F | 3 | F | F | 3 |

| CO       | F  | F    | F    | F   | F  | F | F | F | F | F | F | F | F | F | F | F |

| DO       | F  | F    | F    | F   | 1  | 1 | 1 | D | 3 | F | 3 | F | В | В | F | В |

| E0       | F  | F    | F    | F   | 9  | D | 9 | D | В | F | В | F | F | 3 | F | 3 |

| F0       | F  | F    | F    | F   | 9  | D | 9 | D | F | F | В | F | F | В | F | 3 |

## 7. Internes Memory:

Die CPU III besitzt 64K/256KB RAM und einen Steckplatz für ein EPROM von 2KB - 8KB Speichergröße.

#### 7.1. Dynamisches RAM:

Die 8 Sockel für dynamische RAMs können wahlweise mit 64Kx1 oder mit 256Kx1 bestückt werden. Der Schalter S2 zeigt dem PAL1259 die Speichergröße an. Bei Verwendung von 256K Chips müssen die Adressen A16 und A17 gemultiplext auf Pin 1 der RAMs geführt werden. Dies geschieht im PAL (1259).

Die 64Kx1 Chips gibt es in zwei Versionen, mit 128 Refresh Zyklen also 7Bit und 256 Refresh Zyklen entsprechend 8Bit. Die Z80-CPU besitzt aber bekanntlich nur 7 Refresh-Adressen. Das Adreßbit A7 ist beim Refresh immer 0.

Das achte Adreßbit wird folgendermaßen erzeugt. IC7 ist ein Teiler 1:256, der lediglich die Refresh-Zyklen zählt. Sein Ausgang zeigt dem PAL die Wertigkeit des Adreßbits A7 beim Refresh an. Das PAL muß diese Adresse mit der CPU-Adresse A7 multiplexen.

Es bleibt anzumerken, daß die nun vorhandene 8Bit Refresh-Adresse zu RAMs mit nur 7Bit-Refresh aufwärtskompatibel ist. Die zukünftigen 256Kx1 RAMs benötigen jedoch mindestens eine 8Bit Refresh-Adresse.

#### 7.2. EPROM der CPU III:

Der 28polige Sockel IC15 kann mit drei verschiedenen EPROM-Typen bestückt werden.

| 2716 | S3 = (b) |                   |

|------|----------|-------------------|

| 2732 | S3 = (a) |                   |

| 2764 | S3 = (a) | Auslieferzustand! |

Dabei ist zu beachten, daß im BOOT-Betrieb, also mit eingeblendetem EPROM, immer die unteren 16KB des dynamischen RAM ausgeblendet werden. Da das EPROM dieser Karte praktisch nur als abschaltbarer BOOT sinnvolle Verwendung findet, ist diese Einschränkung tragbar.

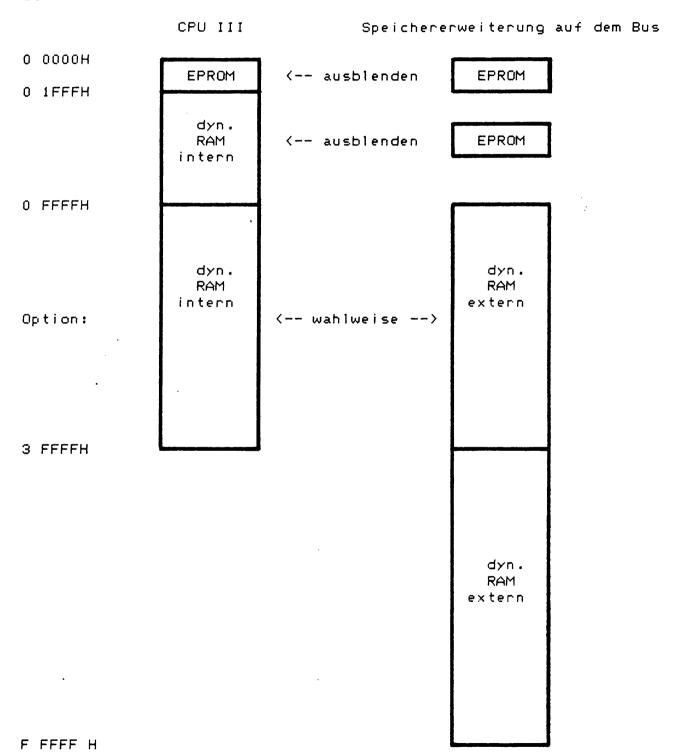

#### 7.3. Speicheraufteilung:

Im Adreßbereich von 1MB liegt das EPROM ab 00000H aufwärts. Das dynamische RAM liegt ebenfalls unten im Speicherbereich. Je nach Bestückung reicht es bis 0FFFFH oder 3FFFH. Eine Speichererweiterung auf dem Bus (64/256K RAM-Karte) darf also erst bei 0FFFFH bzw. 3FFFFH beginnen.

Das DESELECT-Signal wird ebenfalls dekodiert. Durch DESELECT zeigt eine externe Speicherkarte (EPROM oder CMOS-RAM) an, das der jeweilige Speicherbereich des dynamischen RAMs ausgeblendet werden soll.

## 8. Schaltungsbesonderheiten:

#### 8.1. RESET-Generierung:

Das IC41 ist ein Spannungskomparator, dessen Ausgang erst inaktiv wird, falls die Betriebsspannung 4,7V überschritten hat. Dadurch erhält man ein unter allen Umständen funktionierendes Power-On-Signal. Es ist jedoch zu beachten, daß das Netzteil tatsächlich 5V liefert. Einstellbare Netzteile sollten auf 5,1V abgeglichen werden. Ein 100Hz Brumm von mehr als 300mV ist nicht zu vertreten. Die CPU wird in einem solchen Fall ständig zurückgesetzt.

#### 8.2. CMOS-Bestückung:

Die beiden Komparatoren IC35 und IC40 sind Bausteine des Typ **74HC85**. Dies ist erforderlich, da sonst das zulässige Fan-In des internen Bus überschritten wird. Der Typ 74LS85 hat leider ein Fan-In von 3 auf den betreffenden Leitungen.

#### 8.3. Takterzeugung:

Der Quarz Q1 schwingt auf der doppelten Systemtaktfrequenz. Das Signal wird durch das IC26 geteilt und anschließend durch den Transistor T1 auf den erforderlichen Pegel angehoben. Das & Signal ist das einzige nicht TTL-kompatible Signal in der Z80 Familie. Der Spannungshub muß hier mindestens 4V betragen.

# 9. Beispielsoftware:

```

: *** 1/0-PORTS ***

; BASE ADDRESS CPU III

BASIS EQU

20H

BASIS

CTC8 EQU

; CHANEL O OF CTC

CTC1

EQU

BASIS+1

: CHANEL 1 OF CTC

CTC2 EQU

BASIS+2

; CHANEL 2 OF CTC

CTC3 EQU

BASIS+3

; CHANEL 3 OF CTC

; TRANSFER SOURCE BANK

TSB

EQU

BASIS+5

; TRANSFER DESTINATION BANK

TDB

EQU

BASIS+6

EQU

; CPU WORK BANK

CMB

BASIS+7

; CLOCK BOOT- AND LDIR F.F.

CFF

EQU

BASIS+8

; BASE ADDRESS COMMON MEMORY

BASIS+9

BAC

EQU

BDV

EQU

BASIS+0AH

; BANK DESCRIPTION VECTOR

; BANK DESCRIPTION VECTOR WITH ATTRIBUT

EQU

BDVA

BASIS+0BH

; SET WATCH LATCH

SWL

EQU

BASIS+OCH

RW0

EQU

BASIS+00H

; READ WATCH OUTPUT

; DNA' CONTOLLER

DMA

EQU

BASIS+0EH

; * THE FOLLOWING PROGRAMM CONFIGURATES A MEMORY OF 320KB INTO 6 BANKS, EACH *

HAVING A SIZE OF 48KB. THE COMMON MEMORY IS DEFINED TO BE 16KB LARGE.

THIS PROGRAMM CAN EITHER RUN IN THE BOOTSTRAPLOADER OR IN THE COMMON

; * MEMORY. RECKOGNIZE, THAT AFTER A RESET THE BASE ADDRESS OF THE COMMON

MEMORY IS ALWAYS ZERO.

; *** ENTRY: BKING ***

; *** DESTROYS: AF, BC, DE ***

BGR

EQU

OCH

; SIZE OF BANKS: NUMBER OF 4K BLOCKS PER BANK

; (HEX) C = 12

;

```

| BKING: | LD                                         | ,                                       | ; BASE ADDRESS COMMON<br>; FORMAT: (0,0,0,0,415,414,413,412)                                                   |

|--------|--------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|

|        | OUT<br>LD<br>LD                            | (BAC),A<br>B,O<br>C,BDV                 | ;<br>; 16K COMMON<br>; DON'T CHANGE, REFER TO DESCRIPTION<br>; BANK DESCRIPTION REGISTER ADDRESS               |

| BANKO: | LD<br>OUT<br>LD<br>CPL<br>OUT              | A,0<br>(CMB),A<br>A,0                   | ; BANK NUMBER<br>; CUB-PORT ADDRESSES VECTOR RAM<br>; BASE ADDRESS OF BANK<br>; STORAGE IS INVERTED            |

| BANK1: | LD<br>OUT<br>LD                            | (CMB),A<br>A,00010000B                  | BANK NUMBER CUB-PORT ADDRESSES VECTOR RAM BASE ADDRESS OF BANK FORMAT: (A19,A18,A17,A16,A15,A14,A13,A12)       |

|        | LD<br>CPL<br>OUT                           |                                         | SAVE FOR CALCULATION<br>STORAGE IS INVERTED                                                                    |

| BANK2: | LD<br>OUT<br>LD<br>ADD<br>LD<br>CPL<br>OUT | (CUB),A<br>A,E<br>A,BGR<br>E,A<br>(C),A | _                                                                                                              |

| BANK3: | LD<br>OUT<br>LD<br>ADD<br>LD<br>CPL<br>OUT | (CHB),A<br>A,E<br>A,8GR<br>E,A<br>(C),A | BANK NUMBER CLIB-PORT ADDRESSES VECTOR RAM ADD SIZE OF BANK SAVE FOR CALCULATION STORAGE IS INVERTED           |

| BANK4: | LD<br>OUT<br>LD<br>ADD<br>LD<br>CPL<br>OUT | (CHB),A<br>A,E<br>A,BGR<br>E,A          | ; BANK NUMBER ; CIJB-PORT ADDRESSES VECTOR RAM ; ADD SIZE OF BANK ; SAVE FOR CALCULATION ; STORAGE IS INVERTED |

| BANK5: | LD OUT LD ADD LD CPL OUT XOR OUT RET       | (CMB),A<br>A,E<br>A,BGR<br>E,A<br>(C),A | ; BANK NUMBER ; CUB-PORT ADDRESSES VECTOR RAM ; ADD SIZE OF BANK ; SAVE FOR CALCULATION ; STORAGE IS INVERTED  |

```

; *

; *

INTER BANK MOVE USING THE DNA CONTROLLER

; *

DMAINI SHOULD ONLY BE CALLED ONCE AFTER POWER UP

*** ENTRIES: DMAINI - DMA INIT ***

DNANOV - DNA NOVE

į

*** INPUT REGISTERS: ***

HL - SOURCE ADDRESS

DE - DESTINATION ADDRESS

BC - BLOCKLENGTH

H' - SOURCE BANK

L' - DESTINATION BANK

; *** DESTROYS: AF, BC, DE, HL, HL' ***

DMAINI: LD

C,DMA

; PORT ADDRESS

LD

B,LEN1

; BLOCK LENGTH OF TABLE

LD

HL TAB1

; START OF TABLE

OTIR

; INITIALISE DNA

RET

TAB1: DEFB

011111018

; SOURCE ADDRESS & BLOCKLENGTH FOLLOWS,

; TRANSFER FROM PORT A TO B

; SOURCE ADDRESS

DEFW

DEFW

8

; BLOCKLENGTH - 1

00010100B ; PORT A IS MEMORY, ADDRESS INCREMENTS

00010000B ; PORT B IS MEMORY, ADDRESS INCREMENTS

10101101B ; CONTINUE MODE, NO INT, PORT B ADDRESS FOLLOWS

DEFB

DEFB

; DESTINATION ADDRESS

DEFW

DEFB

100110108

; STOP ON END OF BLOCK, CE/WAIT, READY AKTIV HIGH

OCFH

DEFB

; LOAD STARTING ADDRESS FOR BOTH PORTS, CLEAR

; BYTE COUNTER

DEFB

083H

; DISABLE DMA, (CONTROLL REGISTERS ARE NOT AFFECTED)

LEN1

EQU

$-TAB1

;

;

DMAMOV: LD

(SOURCE), HL

LD

(DESTIN), DE

DEC

80

; BLOCK LENGTH FOR DNA HAS TO BE BLOCK LENGTH - 1

; AND SHOULD NOT BE GREATER THAN 0400H = 1K.

LD

(LENGTH), BC

EXX

LD

A,H

; SOURCE BANK

OUT

(TSB),A

LD

A,L

; DESTINATION BANK

OUT

(TDB),A

ĐΧ

LD

C.DMA

; PORTADRESSE

LD

B,LEN2

; BLOCK LENGTH OF TABLE

LD

HL, TAB2

; START OF TABLE

OTIR

; INITIALIZE DMA

RET

```

```

; SOURCE ADDRESS & BLOCK LENGTH FOLLOWS,

TAB2: DEFB

01111101B

; TRANSFER FROM PORT A TO B

SOURCE: DEFW

; SOURCE ADDRESS

LENGTH: DEFW

; BLOCKLENGTH - 1

0

DEFB

101011018

; CONTINUE MODE, NO INT, PORT B ADDRESS FOLLOWS

; DESTINATION ADDRESS

DESTIN: DEFW

0

OCFH

; LOAD STARTING ADDRESS FOR BOTH PORTS, CLEAR

DEFB

; BYTE COUNTER

087H

DEFB

; ENABLE DNA, (CONTROLL REGISTERS ARE NOT AFFECTED)

LEN2

EQU

$-TAB2

i

; *

INTER BANK MOVE USING THE LDIR F.F.

; *

; *** ENTRIES: LDIR - INTER BANK MOVE USING THE LDIR ***

; *** INPUT REGISTERS: ***

HL - SOURCE ADDRESS

DE - DESTINATION ADDRESS

BC - BLOCKLENGTH

H' - SOURCE BANK

L' - DESTINATION BANK

; *** DESTROYS: AF,BC,DE,HL,HL' ***

LDIR:

£ΧΧ

; SOURCE BANK

LD

. A,H

OUT

(TSB),A

LD

A,L

; DESTINATION BANK

OUT

(TDB),A .

EXX

; IF USED INSIDE THE BOOTSTRAPLOADER

;B00T: L0

A,0

; IF USED OUTSIDE OF THE BOOTSTRAPLOADER

NBOOT: LD

A,OFFH

SET

1,A

OUT

(CFF),A

; LDIR F.F. ON

LDIR

RES

1,A

OUT

(CFF),A

; LDIR F.F. OFF

RET

```

```

THESE SUBROUTINES SET OR READ THE CMOS WATCH

; *** ENTRIES: STIME - SET TIME ***

SDATE - SET DATE

RTIME - READ TIME

RDATE - READ DATE

; *** INPUT- OUTPUTREGISTER: ***

B - SECOND

ij

C - MINUTE

D - HOUR

E - DAY

H - MONTH

L - JEAR

*** INPUT/OUTPUT FORMAT: BCD ***

; *** DESTROYS: AF,BC,DE,HL ***

j

XMHZ

EQU

2

; SYSTEM CLOCK = 4MHZ OR LOWER

; SYSTEM CLOCK = &MHZ

;XMHZ

EQU

3

STIME: PUSH

80

LD

€,8

; SECOND

LO

8,000011118

; ADDRESS FOR SECONDS

CALL

WREG

POP

80

; C = MINUTE

PUSH

BC

LD

B,00061011B

; ADDRESS FOR MINUTES

CALL

WRE6

; HOUR

LD

C,D

LD

B,00001101B

; ADDRESS FOR HOURS

CALL

WREG

POP

BC

RET

ţ

į

SDATE: PUSH

BC

; DAY

LD

C,E

LD

B,000010018

; ADDRESS FOR HOURS

CALL

WREG

LD

C,H

; MONTH

LD

B,00001110B

; ADDRESS FOR MONTH

CALL

WREG

LD

C,L

; JEAR

LD

B,000011008

; ADDRESS FOR JEARS

CALL

WREG

POP

BC

RET

```

```

RTIME: LD

B,00000111B

; ADDRESS FOR SECONDS

CALL

RREG

LD

B,C

; B = SECOND

PUSH

BC

LD

; ADDRESS FOR MINUTES

B,00000011B

CALL

RREG

POP

DE

LD

B,D

; C = MINUTE

PUSH

BC

LD

B,00000101B

; ADDRESS FOR HOURS

CALL

RREG

LD

D,C

; D = HOUR

POP

BC

RET

;

RDATE: LD

B,00000001B

; ADDRESS FOR DAYS

CALL

RREG

LD

E,C

; E = DAY

LD

B,00000110B

; ADDRESS FOR MONTH

CALL

RREG

LD

H,C

; H = MONTH

; ADDRESS FOR JEARS

LD

8,000001008

CALL

RREG

LD

L,C

; L = JEAR

RET

;

į

; *** WREG ***

; THIS PROGRAM WRITES TO A REGISTER OF THE CHOS WATCH.

; INPUT REGISTER: B = REGISTER ADDRESS

(FORMAT: 0,0,0,0,1,A0,A1,A2; A0-A2 ARE INVERTED)

C = DATA TO BE WRITTEN

(FORMAT: TWO WORD BCD)

WREG:

PUSH

BC

PUSH

DE

PUSH

AF

LD

A,C

CPL

LD

C,A

; WRITE DATA INVERTED

LD

0,4

; BIT COUNTER

WREGO: LD

A,B

OR

0EH

; CE = LOW, CLOCK = LOW, WRITE MODE SELECTED

CALL

WCLOCK

; BIT WRITE

RRC

В

; NEXT BIT

DEC

JR

NZ,WREGO

; IF ZERO THAN 4BITS DONE

```

```

; BIT COUNTER

LD

0,8

WREG1: RLC

; MSB FIRST

C

A,C

LD

OR

0EH

; CE = LOW, CLOCK = LOW, WRITE MODE SELECTED

CALL

WCLOCK

; BIT WRITE

DEC

JR

NZ ,WREGI

; IF ZERO THAN 8BITS DONE

XOR

; DISABLE WATCH

OUT

(SUL),A

POP

AF

POP

DE

POP

BC

RET

;

;

; *** RREG ***

; THIS PROGRAM READS FROM A REGISTER OF THE CHOS WATCH.

; INPUT REGISTER: B = REGISTER ADDRESS

(FORMAT: 0,0,0,0,1,A0,A1,A2; A0-A2 ARE INVERTED)

; OUTPUT REGISTER: C = DATA READ

(FORMAT: TWO WORD BCD)

;

;

RREG:

PUSH

DE

PUSH

AF

LD

0,4

; BIT COUNTER

RREGO: LD

A,B

; CE = LOW, CLOCK = LOW, WRITE MODE SELECTED

OR

0EH

WCLOCK

CALL

; BIT WRITE

RRC

В

; NEXT BIT

DEC

D

; IF ZERO THAN 4BITS DONE

JR

NZ, RREGO

į

; BIT COUNTER

0.8

LD

LD

C,OFFH

; ALL BITS ON

; BIT READ

RCLOCK

RREG1: CALL

BIT

0,A

JR

NZ,RREG2

RES

3,0

RREG2: RRC

C

; LSB FIRST

DEC

NZ,RREG1

JR

; IF ZERO THAN 8BITS DONE

XOR

; DISABLE WATCH

OUT

(SWL),A

POP

AF

POP

DE

RET

```

```

WCLOCK: PUSH

BC

(SUL),A

; CLOCK OF WATCH DURING WRITE

OUT

LD

B,XMHZ

; T = 1/2 * CLOCK

; CA. 7YS

LIWCLK: DJNZ

LIWCLK

; CLOCK = HIGH

RES

3,A

(SWL),A

OUT

LD

B,XMHZ

L2WCLK

L2WCLK: DJNZ

; CLOCK = LOW

SET

3,A

OUT

(SUL),A

POP

BC

RET

; CLOCK OF WATCH DURING READ

RCLOCK: PUSH

LD

A,00001100B

; CE = LOW, CLOCK = LOW, READ SELECTED

OUT

(SWL),A

PUSH

AF

; SAVE CONTROLL BYTE

; T = 1/2*CLOCK

LD

B,XMHZ

LIRCLK: DJNZ

LIRCLK

; CA. 7YS

RES

; CLOCK = HIGH

3,A

OUT

(SWL),A

IN

A,(RWO)

; READ WATCH

LD

C,A

; SAVE DATA

B,XMHZ

LD

L2RCLK: DJNZ

L2RCLK

POP

AF

; RESTORE CONTROLL BYTE

SET

3,A

; CLOCK = LOW

OUT

(SUL),A

POP

AF

; RESTORE DATA

LD

A,C

; RESTORE DATA

POP

80

RET

```

# 10. Busbelegung:

| Name               | Signal LS-Fa           | ın – Qu t,  | ∕In              |              |          |          |          |              |

|--------------------|------------------------|-------------|------------------|--------------|----------|----------|----------|--------------|

|                    | _                      | 60          | 1.               |              |          |          |          |              |

| A0                 | Adresse 0              | 60          | 1                |              |          |          |          |              |

| A1<br>A2           | Adresse 1<br>Adresse 2 | 60          | 1                |              |          |          |          |              |

| A3                 | Adresse 3              | 60          | i                |              |          |          |          |              |

| A4                 | Adresse 4              | ح<br>ح<br>ا |                  |              |          |          |          |              |

| A5                 | Adresse 5              | 60          | 1                |              |          |          |          |              |

| A6                 | Adresse 6              | 60          | i                |              |          |          |          |              |

| A7                 | Adresse 7              | 60          | i                |              |          |          |          |              |

| A8                 | Adresse 8              | 60          | i                | Belegung     | der      | VG-      | 64 L     | eiste        |

| A9                 | Adresse 9              | 60          | 1                |              | <u> </u> | <u> </u> | X:E      |              |

| A10                | Adresse 10             | 60          | 1                |              | a        |          | c        |              |

| A11                | Adresse 11             | 60          | 1                | •            |          |          |          |              |

| A12                | Adresse 12             | 60          | 1                | +50          | 1        | 0        | 1        | +50          |

| A13                | Adresse 13             | 60          | 1                | D5           | 2        | 0        | 2        | D0           |

| A14                | Adresse 14             | 60          | 1                | D6           | 3        | 0        | 3        | D7           |

| A15                | Adresse 15             | 60          | 1                | DЗ           | 4        | 0        | 4        | D2           |

| A16                | Adresse 16             | 20          |                  | D4           | 5        | O        | 5        | A0           |

| A17                | Adresse 17             | 20          |                  | A2           | 6        | 0        | 6        | A3           |

| A18                | Adresse 18             | 20          |                  | A4           | 7        | 0        | 7        | A1           |

| A19                | Adresse 19             | 20          |                  | A5           | 8        | 0        | 8        | A8           |

|                    |                        |             |                  | A6           | 9        | 0        | 9        | A7           |

| D0                 | Data O                 | 60          | 1                | WAIT         | 10       | 0.       | 10       | A16          |

| D1                 | Data i                 | 60          | 1                | BUSRQ        | 11       | 0        | 11       | IEI          |

| D2                 | Data 2                 | 60          | 1                | BAI          | 12       | 0        | 12       | A17          |

| DЗ                 | Data 3                 | 60          | 1                |              | 13       | 0        |          | A18          |

| D4                 | Data 4                 | 60          | 1                | A19          | 14       | 0        | 14       | D1           |

| D5                 | Data 5                 | 60          | 1                |              | 15       | 0        | 15       |              |

| D6                 | Data ó                 | 60 ا        | 1                | 2Ф           | 16       | 0        | 16       | IEO          |

| D7                 | Data 7                 | 60          | 1                | BAO          | 17       | 0        | 17       | A11          |

|                    |                        |             |                  | A14          | 18       | 0        | 18       | A10          |

| MRQ                | Memory Request         | 60          | 1                |              | 19       | 0        | 19       |              |

| IORQ               | I/O Request            | 60          | 1                | MI           | 20       | 0        | 20       |              |

| RD                 | Read                   | 60          | 1                |              | 21       | 0        | 21       | INT          |

| WR                 | Write                  | 60          | 1                | DMARDY       | 22       | 0        | 22       | WR           |

| HALT               | Halt                   | 60          |                  |              | 23       | 0        | 23       | ==           |

| MI<br>DESIGNATION  | Maschinenzyklus 1      |             |                  |              | 24       | 0        | 24       |              |

| RFSH               | Refresh                | 60          |                  | 55051 507    | 25       | 0        | 25       | HALT         |

| WAIT               | Wait                   |             | 3,2mA            | DESELECT     | 26       | 0        | 26       | PWCLR        |

| ð<br>ar            | Clock                  | 24mA        |                  | IORQ         | 27       | 0        | 27       | A12          |

| 2 <b>6</b>         | 2 x Clock              | 20          |                  | RFRSH        | 28       | 0        | 28       |              |

| PWCLR              | Power On Clear         | 60          |                  | A13          | 29       | 0        | 29       | <u>ф</u>     |

| RESET              | Reset                  |             | 4mA              | A9           | 30       | 0        | 30<br>31 |              |

| DESELECT<br>DMARDY | Deselect<br>DMA Ready  |             | 3,2mA            | BUSAK<br>GND | 31<br>32 | 0        | 32       | RESET<br>GND |

| IEI                | Int. Enable In         |             | 3,2mA<br>2       | GIND         | 32       | 0        | 32       | GIND         |

| IEO                | Int. Enable Out        | 20          |                  | :            |          | :        |          | •            |

| INT                | Int. Enable Out        | 20          | 3,2mA            |              |          |          |          |              |

| NMI                | Non Maskable Int       |             | 3,2mA            |              |          |          |          |              |

| BAI                | Busacknowledge In      |             | S1               |              |          |          |          |              |

| BAO                | Busacknowledge Ou      |             | J.               |              |          |          |          |              |

| BUSAK              | Busacknowledge         | 60          |                  |              |          |          |          |              |

| BUSRQ              | Busrequest             |             | 3,2mA            |              |          |          |          |              |

| • · · •            | ·                      |             | , <del>-</del> · |              |          |          |          |              |

Die Stromaufnahme beträgt ca. 1,2A auf den 5V bei Bestückung mit 64KB und einem EPROM 2764.

# 11. Stückliste:

| IC 1 - 3         | 74LS245                          | R 1 - 3,              |                 |

|------------------|----------------------------------|-----------------------|-----------------|

| IC 4 - 5         | 74LS243                          | 7 - 10                | 1K5             |

| IC 6             | Prom (1208)                      | R 4, 14               | 4K7             |

|                  |                                  |                       | 680R            |

| IC 8             | 74LS125                          | R 11                  | <b>1</b> 2K     |

| IC 9             |                                  | R 12, 13              | 330R            |

| IC 10, 26        |                                  |                       | 22K             |

| IC 11            | Z80(A/B)-DMA(selekt.)            | SIL 1, 2 8            | x 1K2           |

| IC 12            | 74LS08                           | •                     |                 |

| IC 13, 14        |                                  | C 1                   | 33pF            |

|                  | BYTEWIDE-Sockel                  | C 2 - 5               |                 |

| IC 16,17,21,22,  | 4164/41256                       |                       | 10yF 16V        |

|                  | 128/256 R.C. (150ns)             |                       |                 |

| IC 18            | PAL14L8 (1259)                   | C 17 Stück a'         | 100nF RM2,5     |

| IC 18<br>IC 19   | PAL12L10 (1258)                  |                       | ·               |

| IC 20            | Z80(A/B)-CTC                     | D 1                   | 1N914           |

| IC 23            | Z80(A/B)-CTC<br>74504 Schottky ! |                       |                 |

| IC 24            | N82S09/19 (64x9)                 | T 1 2                 | N2906           |

| IC 27, 28        | 74LS283                          |                       |                 |

| IC 30            | 74LS02                           | Q 1 8MHz              | /10MHz/12MHz    |

| IC 31, 32        | 74LS670                          | Q 2 32                | 768Hz           |

| IC 34            | 74LS04                           |                       |                 |

| IC 35, 40        | 74HC85 CMOS !                    | VG-64 Messerle        | iste /          |

| IC 36, 39        | 74LS175                          | Pfostenleiste 18 pol. |                 |

| IC 38            | MEM E050-16                      | Steckbrücken 5        | Stück           |

| IC 41            | TL7705A CPA                      | AKKU 2DK60            |                 |

|                  |                                  |                       |                 |

| Sockel Spolig 3  | 300mil. 1 Stück                  |                       | 300mil. 2 Stück |

|                  | 300mil. 7 Stück                  |                       | 600mil. 3 Stück |

| Sockel 16polig 3 | 300mil. 20 Stück                 | Sockel 40polig        | 600mil. 2 Stück |

| Sockel 20polig 3 | 300mil. 3 Stück                  |                       |                 |

# 12. Bestückungsdruck: