# Inhaltsverzeichnis

| 1.        | Aufbau des alphatronic-PC                                      | 1           |

|-----------|----------------------------------------------------------------|-------------|

| 1.1       | Uffnen und Schließen des alphatronic-PC<br>Leichte Reparaturen | 5<br>6<br>6 |

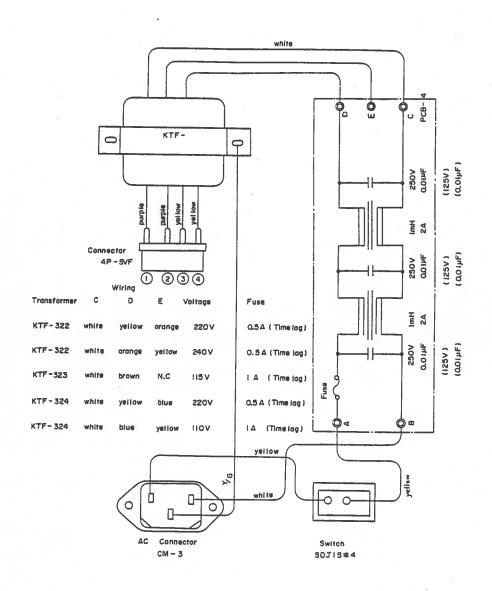

| 1.2.1     | Austausch der Sicherung<br>Austausch der Netzteileinheit       | 6           |

| 1.2.3     | Austausch des Netzsteckers oder -schalters                     | 7           |

| 1.2.4     | Austausch der Keyboardplatine                                  | 7           |

| 1.2.5     | Austausch eines Steckers                                       | 8           |

| 1.2.6     | Austausch eines gesockelten IC                                 | 9           |

| 2.        | Blockschaltbild                                                |             |

| 2.1       | Beschreibung am Blockschaltbild                                | 10          |

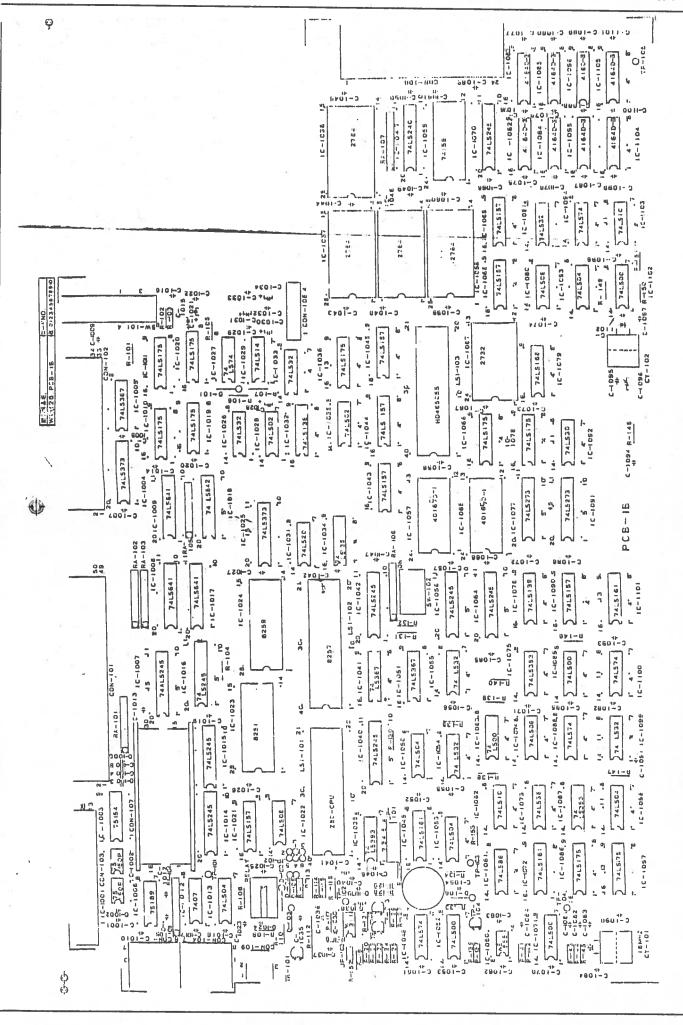

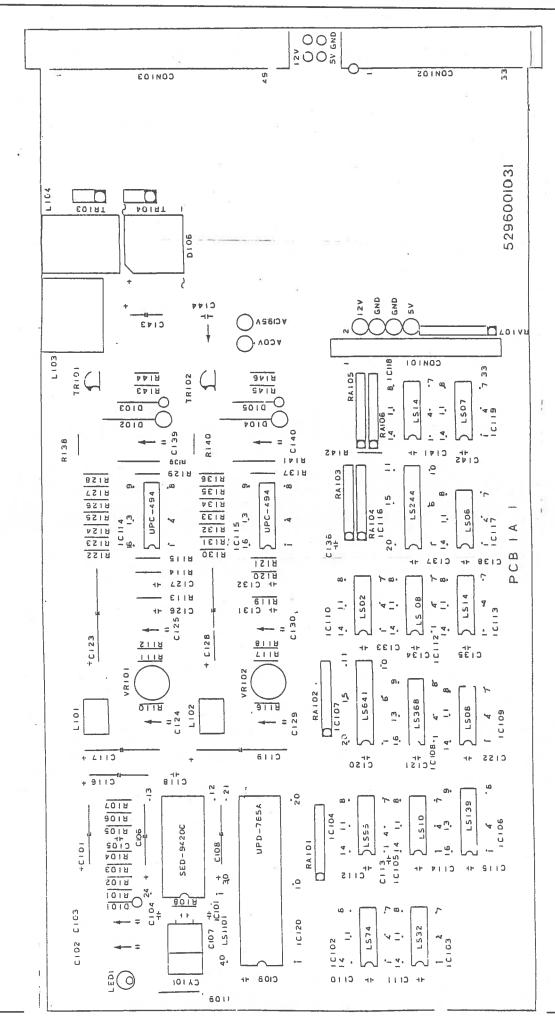

| 2.2       | Bestückungsplan der Hauptplatine                               | 13          |

|           |                                                                |             |

| 3.        | Microprozessor Z 80 A                                          |             |

| 3.1       | Architektur des Z 80 A                                         | 14          |

| 3.2       | Befehlssatz des Z 80 A                                         | 19          |

|           |                                                                |             |

| 4.        | Memory Mapping                                                 |             |

| 4.1       | Memory Mapping                                                 | 32          |

| 4.2       | I/O Adressen                                                   | 33          |

|           |                                                                |             |

| <u>5.</u> | Schnittstellenbeschreibungen                                   |             |

| 5.1       | SPORT (System Port)                                            | 35          |

| 5.2       | Tastatur                                                       | 39          |

| 5.3       | Serielle Schnittstelle                                         | 43<br>58    |

| 5.4       | Cassettenschnittstelle Parallelschnittstelle (Centronics)      | 64          |

| 5.6       | Systembus - Schnittstelle                                      | 71          |

| 5.7       | Videoschnittstellen RGB und BAS                                | 88          |

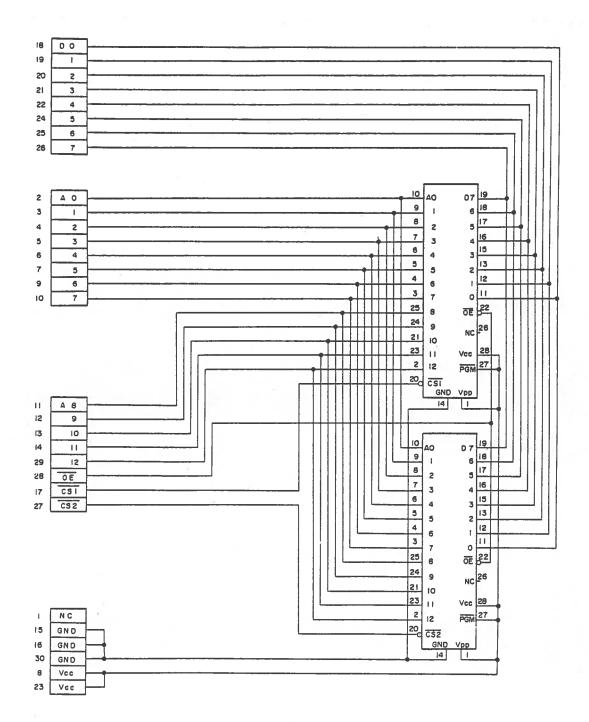

| 5.8       | ROM PACK                                                       | 104         |

|           |                                                                |             |

| 6.                                                           | Software                                                                                                                                                                        | 100                                           |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 6.1<br>6.2<br>6.3                                            | Kurzbeschreibung des IPL Monitors<br>CP/M Betriebssystem<br>BASIC                                                                                                               | 109<br>115<br>118                             |

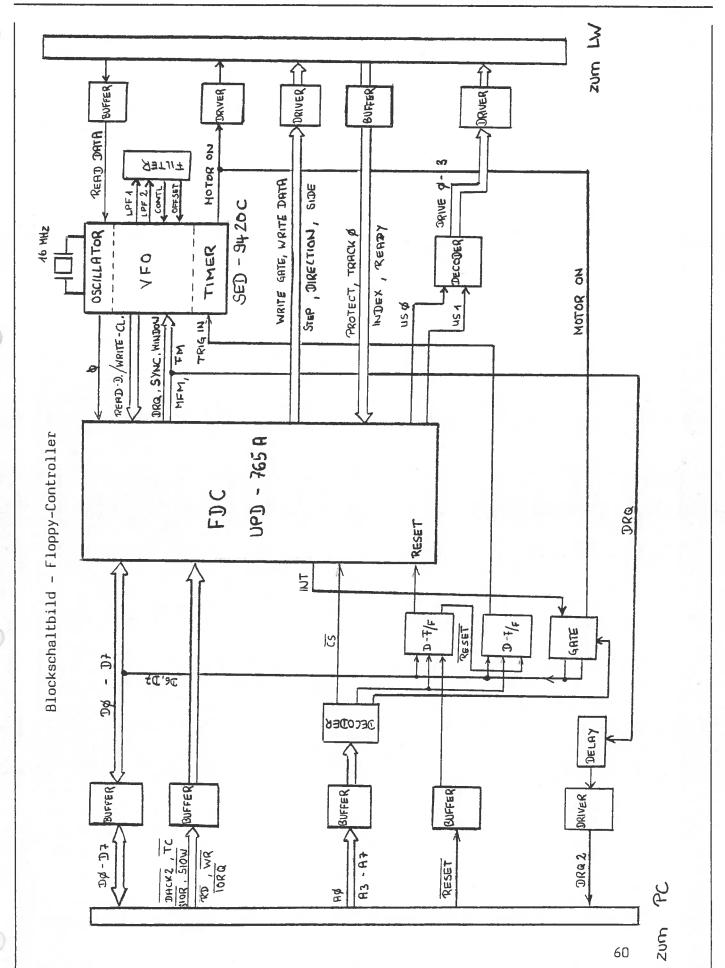

| 7.1<br>7.1<br>7.2<br>7.3<br>7.3.1                            | Betrieb eines Floppydisk  Allgemeine Hinweise Sicherungswechsel Controller Aufzeichnungsformat                                                                                  | 120<br>127<br>128<br>128                      |

| 8.1<br>8.2<br>8.3                                            | Drucker Gabriele 8008 V.24 TRD 7020 V.24 Epson MX 80 FT3                                                                                                                        | 133<br>134<br>135                             |

| 9.                                                           | Stichwortregister                                                                                                                                                               | 136                                           |

| 10.1<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7 | Anhang Liste der IC's Bezugsquellenangabe für Datenblätter Befehlsliste Z 80 A Literaturverzeichnis Schnittstellen-Steckverbinder ESCAPE-Sequenzen Monitor-Listing Weitere Tips | 141<br>142<br>143<br>168<br>169<br>170<br>175 |

|                                                              |                                                                                                                                                                                 |                                               |

# 1. Aufbau des alphatronic-PC

Der Aufbau des alphatronic-PC ist nach neuestem Fertigungsstandard erstellt.

Sein Gehäuse besteht aus zwei Kunststoffhalbschalen, die zur Abschirmung der entstehenden Störstrahlung des Rechners innen elektrisch leitend lackiert sind. Zur Verbindung der beiden Halbschalen zu einem geschlossenen Gehäuse sind im vorderen Teil des Oberteiles drei "Haltenasen" angebracht, die in entsprechende Üsen im Unterteil greifen. Geschlossen wird das Gehäuse mit drei Schrauben, die von unten durch das Unterteil in angespritzte Zapfen des Oberteils eingeschraubt werden.

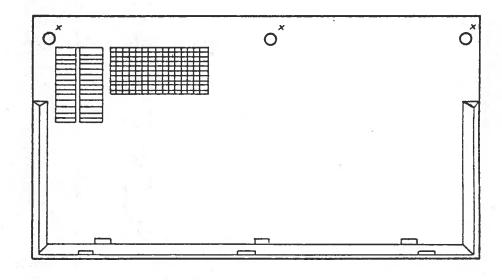

# Unterseite des PC

\* = Schrauben

Das Unterteil trägt in seinem Inneren die "Hauptplatine". Sie ist ebenfalls auf angespritzten Sockeln verschraubt. Auf der Hauptplatine sind, bis auf Netzteil, Netzfilter, Trafo und Tastatur (Keyboard), alle Baugruppen des alphatronic-PC vereint.

Alle Verbindungen zwischen der Hauptplatine und anderen Baugruppen sind gesteckt.

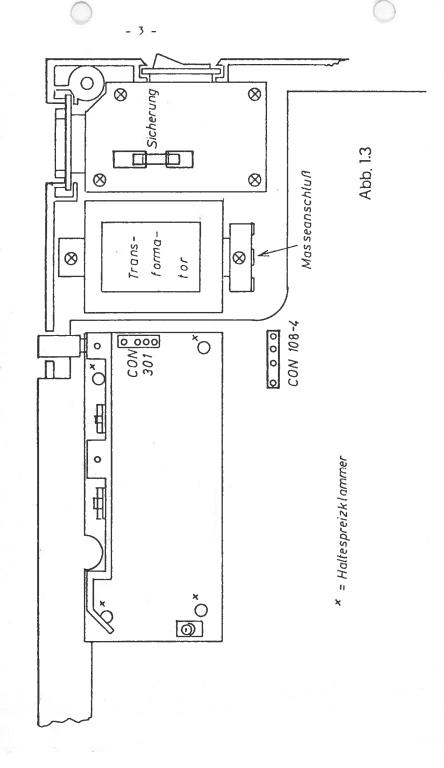

Oberhalb der Hauptplatine (siehe Abb. 1.3) befindet sich rechterhand das Netzfilter und der Netztrafo. Das Netzteil (mit Spannungsregler etc.) wurde aus Platzgründen über die Hauptplatine auf Kunststoffhalter gesetzt.

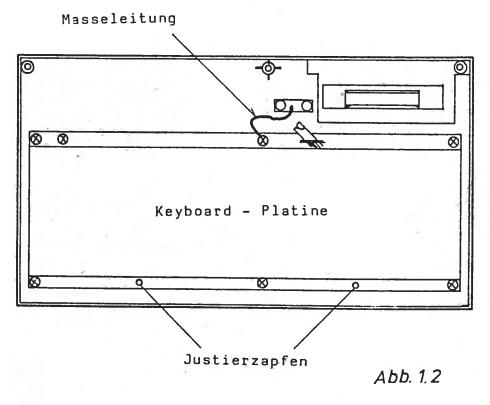

In das Oberteil des Gehäuses ist die Tastaturplatine eingebaut. Auf ihr sind alle Tasten sowie die Leuchtanzeigen montiert. Zur mechanischen Stabilisierung ist diese Platine mit zusätzlichen Verstärkungen versehen. Die obere Kunststoffschale enthält Justierzapfen, die als Montagehilfe in die Tastaturplatine ragen (Abb. 1.2).

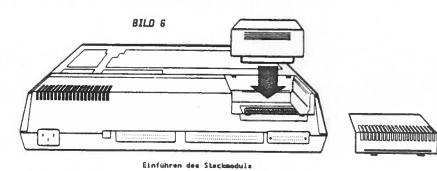

Der ebenfalls im Oberteil angeordnete "ROM-PACK"-Schacht wird durch einen ohne Werkzeug entfernbaren Kunststoffdeckel verschlossen. Die Geometrie des Schachtes ist so ausgelegt, daß eine Verpolung des ROM-PACK-Modules vermieden wird.

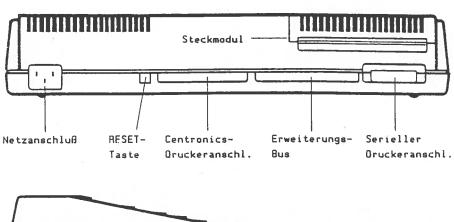

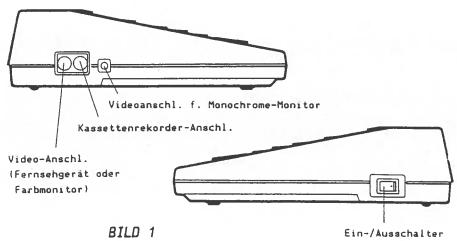

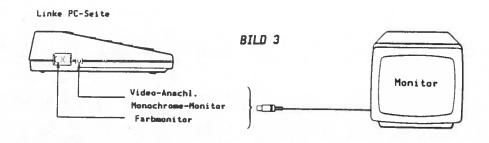

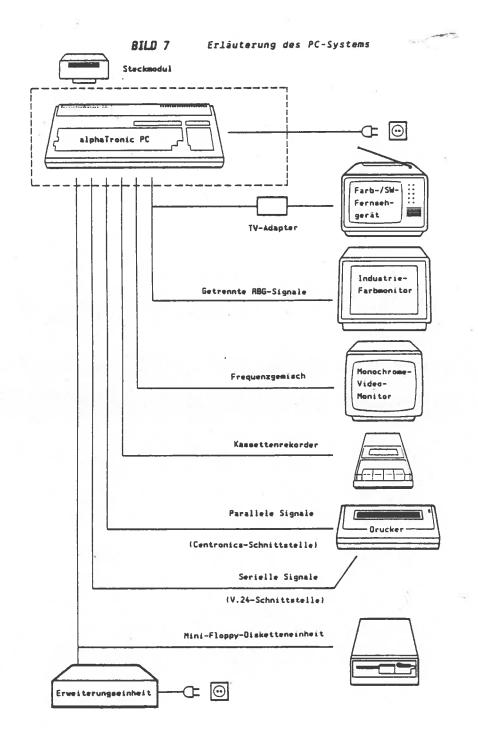

Die Steckverbinder für das parallele Ausgabeport, die Systembus- Schnittstelle, die serielle Schnittstelle, sowie der Resettaster befinden sich an der Gehäuserückseite (Abb. 5.16). Die Anschlüsse für monochrome und Farbmonitore, sowie für einen Cassettenrecorder sind auf der linken Gehäuseseite zugänglich.

Für die vielpoligen Verbinder der parallelen, seriellen und der Systembus-Schnittstelle sind zusätzliche Befestigungen vorgesehen. An diesen werden die alphatronic Steckverbinder mit ihren Schrauben befestigt.

# ACHTUNG

Garantieverlust bei unbefugtem Öffnen des Gerätes !

# 1.1 Offnen und Schließen des alphatronic-PC

- 1. Netzleitung vom Gerät lösen

- 2. Alle Leitungen zu weiteren Geräten lösen

- 3. Das Gerät mit der Tastatur nach unten auf eine ebene Unterlage legen.

- 4. Die in Abbildung 1.1 markierten Schrauben mit einem passenden Kreuzschlitzschraubendreher herausdrehen.

- 5. Das Gerät wieder auf die Unterseite drehen, dabei das Ober- und Unterteil verbunden halten.

- 6, Jetzt das Oberteil am hinteren Ende des Gerätes etwa l cm anheben und nach vorne von den am Unterteil angespritzten Haken abschieben.

- 7. Das Oberteil (Tastatur) kann nun nach rechts neben das Unterteil geschwenkt werden (Die Öffnung des Oberteils zeigt nach oben).

# 1.1.2 Zusammenbau

Der Zusammenbau geschieht in umgekehrter Reihenfolge. Es ist darauf zu achten, daß kein Kabel eingeklemmt wird.

# Anmerkung:

Da die verwendeten Schrauben selbstgewindeschneidend sind und das Plastik abgenutzt wird, ist häufiges Üffnen des. Gerätes zu vermeiden.

# 1.2 Leichte Reparaturen

#### ACHTUNG

Vor der Ausführung von Arbeiten an Baugruppen oder Bauteilen des PC ist unbedingt sicherzustellen, daß keine elektrostatische Ladung des Körpers oder der Werkzeuge an die Bauteile abfließen kann! (z.B. durch Verbinden des Körpers mit Masse (GND) des PC über einen Widerstand von <= 10 MOhm und einer flexiblen Leitung).

# 1.2.1 Austausch der Netzsicherung

- 1. Öffnen des Gerätes wie in 1.1. beschrieben.

- Auf der Netzfilterplatine ist nun die Sicherung zugänglich (Abb. 1.3). Der Austausch darf nur gegen eine Sicherung mit der Bezeichnung T 0,5 A erfolgen.

- 3. Schließen des Gerätes wie in 1.1.2 beschrieben.

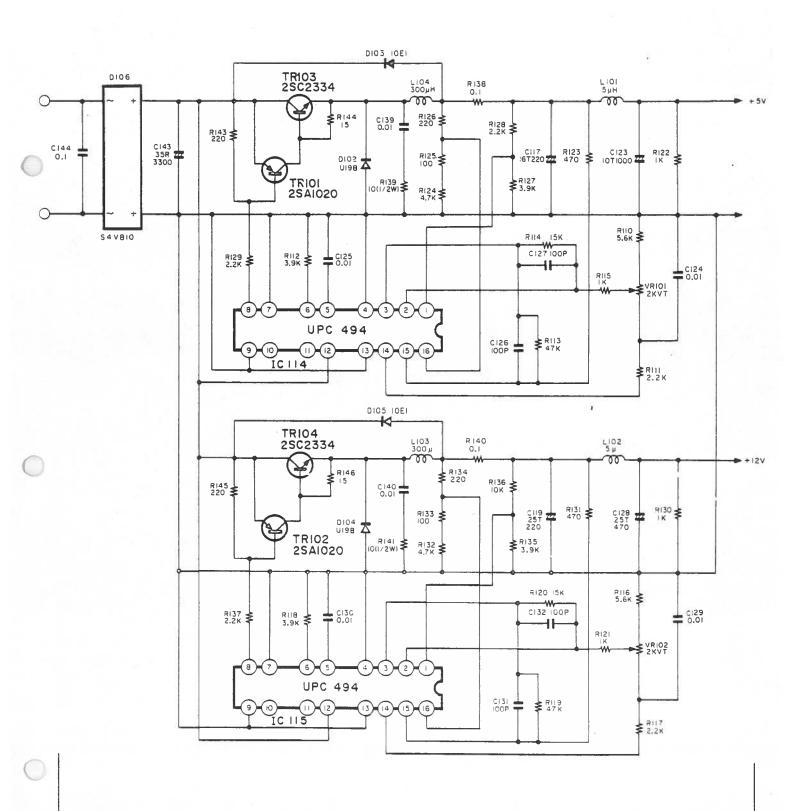

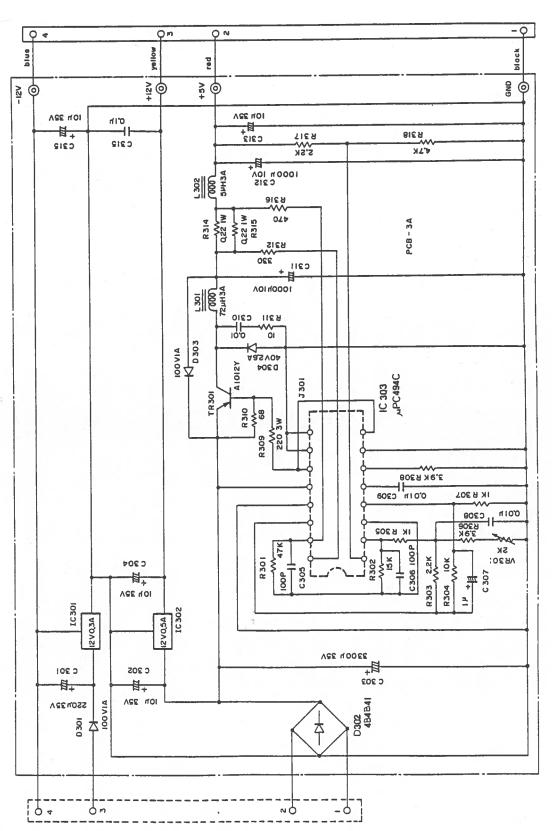

# 1.2,2 Austausch der Netzteilplatine

- 1. Offnen des Gerätes wie in 1.1. beschrieben.

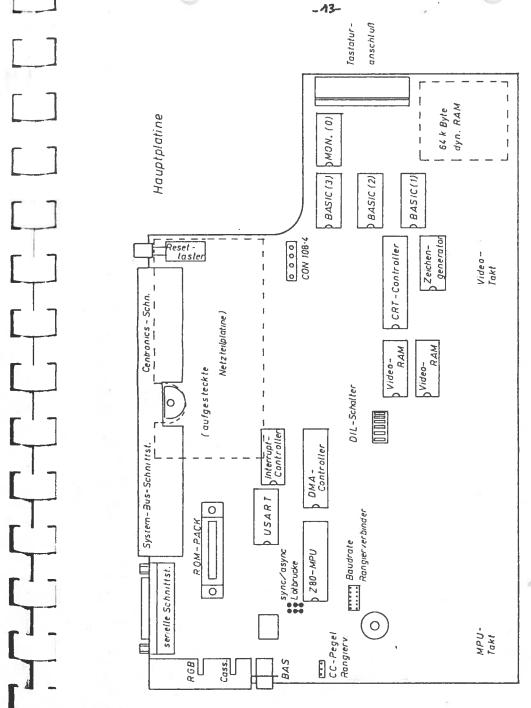

- 2. Lösen des Steckverbinders con 108-4 auf der Hauptplatine (Abb 2.2).

- 3. Lösen des Steckverbinders con 301 auf der Netzteilplatine (Abb 1.3).

- 4. Mit einer Flachzange nacheinander die Sicherungsrasen der 4 Halteklammern (Abb 1.3) zusammendrücken und die Netzplatine leicht über die Sicherungsnasen heben.

- 5. Nun die Platine vorsichtig nach oben abheben.

- 6. Aufsetzen der neuen Platine in umgekehrter Reihenfolge bis zum sicheren Einrasten der Sicherungsnasen.

- 7. Aufstecken der Verbinder con 108-4 und con 301 unter Beachtung ihrer Polaritätshilfen.

- 8. Schließen des Gerätes wie in 1.1.2 beschrieben.

# 1.2.3 Austausch des Netzsteckers oder -schalters

- 1. Uffnen des Gerätes wie in 1.1. beschrieben.

- Beachtung der elektrostatischen Ladung des Körpers (Hinweise in 1.2.2).

- Lösen der mit @ bezeichneten Schrauben mit einem Kreuzschlitzschraubendreher.

- 4. Nach dem Abnehmen der Platine sind der in Gehäuseaussparungen liegende Netzsteckerbuchse und Netzschalter zugänglich.

Typ: 3-polige EUROPA NORM-Gerätesteckerbuchse

- 5. Wiedereinbau in umgekehrter Reihenfolge.

- 6. Schließen des Gerätes wie in 1.1.2 beschrieben.

# 1.2.4 Austausch des Keyboards

- 1. Offnen wie in 1.1. beschrieben

- Lösen des Steckverbinders auf der Hauptplatine. Dabei vorsichtig, während man die Haltenase des Steckers anhebt, diesen von den Steckerstiften schieben.

- Erst jetzt die Masseverbindung zur Hauptplatine lösen.

- 4. Mit @ bezeichnete Schrauben (Abb. 1.2) mit einem passenden Kreuzschlitzschraubendreher herausdrehen.

- 5. Das Keyboard mit den Tasten nach unten belassen.

- Die Keyboardplatine jetzt vorsichtig nach oben entnehmen.

V O R S I C H T : Die auf der Oberseite sichtbaren LED's werden leicht verbogen.

- 7. Einbau

- 7.1 Die Platine ohne Gewaltanwendung in den Sitz legen.

- 7.2 Jetzt die Platine mit den Fingern im Sitz festhalten, das Gehäuseoberteil drehen und den richtigen Sitz der Tasten und LED's kontrollieren. Ggf. Platine neu in den Sitz stecken oder durch verschieben die Tasten mittig ausrichten.

- 7.3 Alle Schrauben wieder (nicht zu fest) anziehen, dabei nicht vergessen, die Masseleitung unterzulegen.

- 7.4 Masseverbindung zur Hauptplatine des TA PC herstellen.

- 7.5 Jetzt den Vielfachsteckverbinder mit seiner Sicherungsnase nach oben auf den dazugehörenden Stecker auf der Hauptplatine stecken.

- 8. Schließen des Gerätes wie in 1.1.2 beschrieben.

# 1.2.5 Austausch eines Steckers

Zum Austausch eines Steckers ist es erforderlich, die Hauptplatine auszubauen. Hiervon raten wir dringend ab, da auch schon leichtes Verbiegen der Platine wegen der angewandten "Feinleitertechnik" unweigerlich zu Leiterbahnrissen führen kann.

Von Lötarbeiten an den Baugruppen ohne spezielles Auslötwerkzeug raten wir ebenfalls wegen der sehr großen Beschädigungsgefahr dringend ab.

# 1.2.6 Austausch gesteckter IC's

#### Antistatikvorschriften beachten!

IC's nicht an den Beinchen berühren und nur auf eine geerdete Unterlage ablegen.

Falls kein kombiniertes Einsetz-/Ausziehwerkzeug zur Verfügung steht, ist das IC in möglichst vielen kleinen Schritten beidseitig hebelnd aus dem Sockel zu entnehmen. Als Hebel eignet sich notfalls eine gekröpfte Pinzette.

Es ist darauf zu achten, den Hebel nicht auf der Hauptplatine abzustützen um Leiterbahnrisse zu vermeiden.

Das Einsetzen eines IC erfolgt unter Berücksichtigung der Punkte 1 bis 4:

- Pin 1 der IC's gehört in den Kontakt unten links des Sockels, wenn das Netzteil oben rechts ist.

- 2. IC-Beinchen einer Reihe in dem Sockel ansetzen.

- Zweite Beinchenreihe parallel in Richtung erste Reihe drücken, bis die Beinchen direkt über den Kontaktfedern stehen.

- Nun des IC gleichmäßig und vorsichtig in den Sockel drücken.

### ACHTUNG:

Bei zu starkem Druck auf das IC besteht Gefahr von Leiterbahnrissen, da sich die Hauptplatine verbiegt.

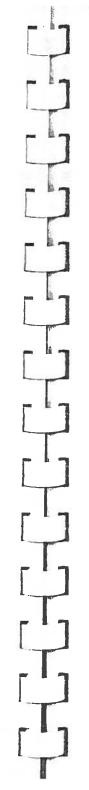

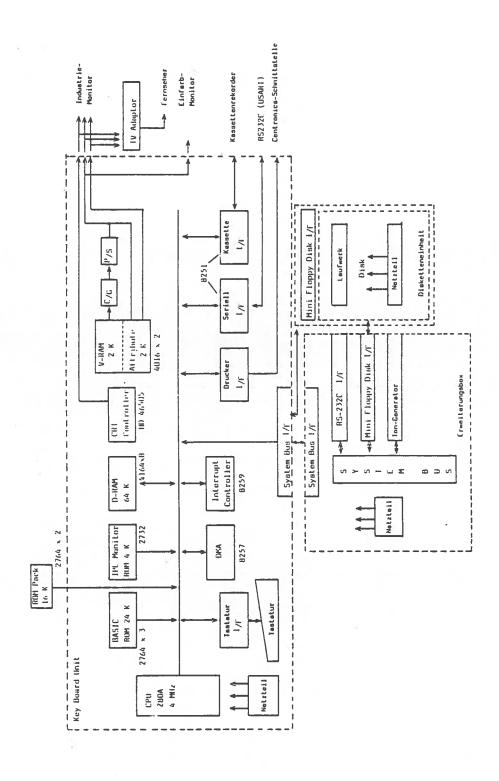

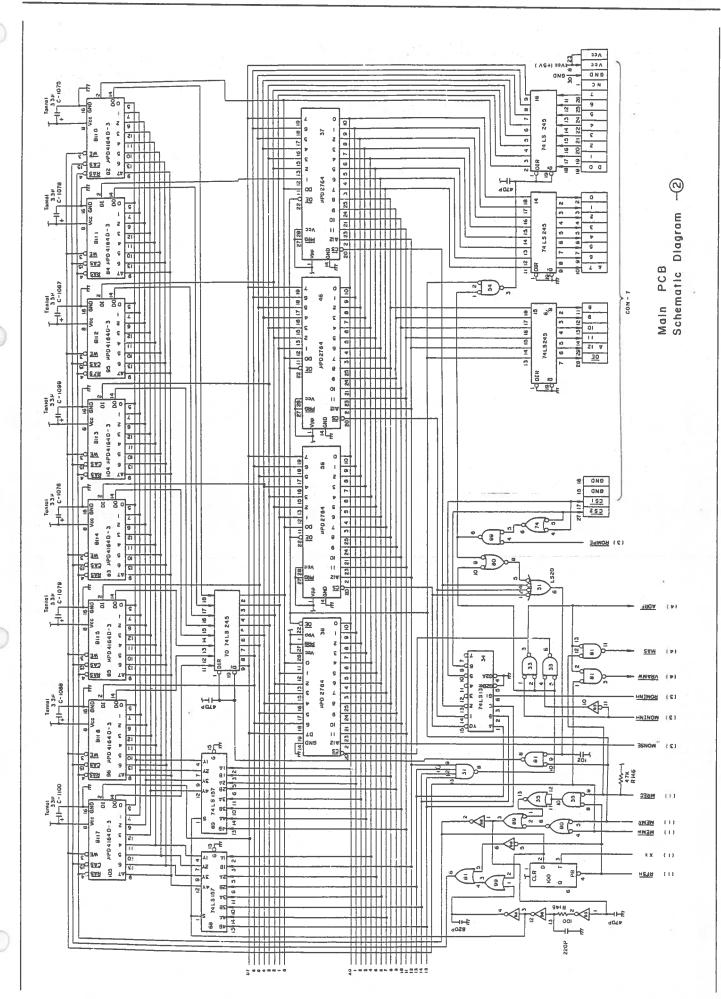

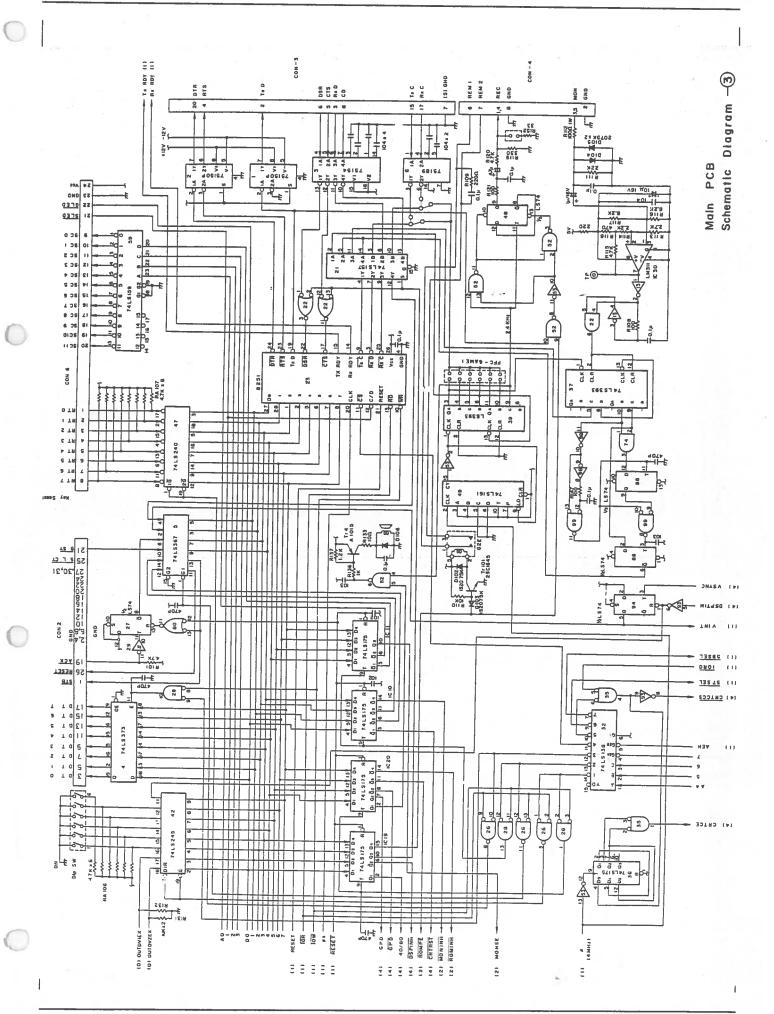

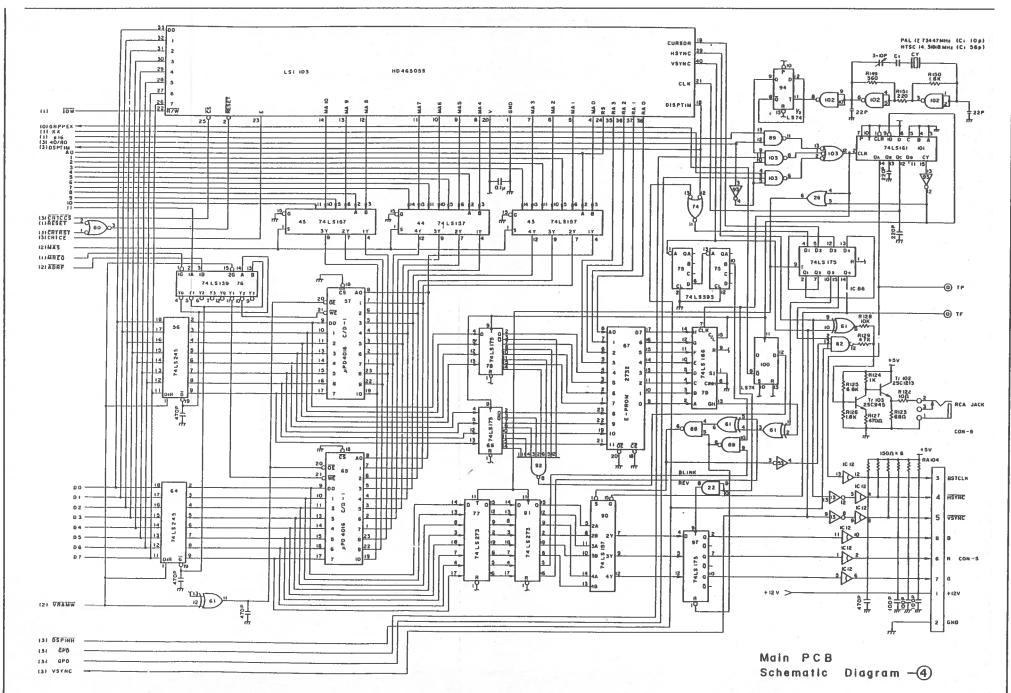

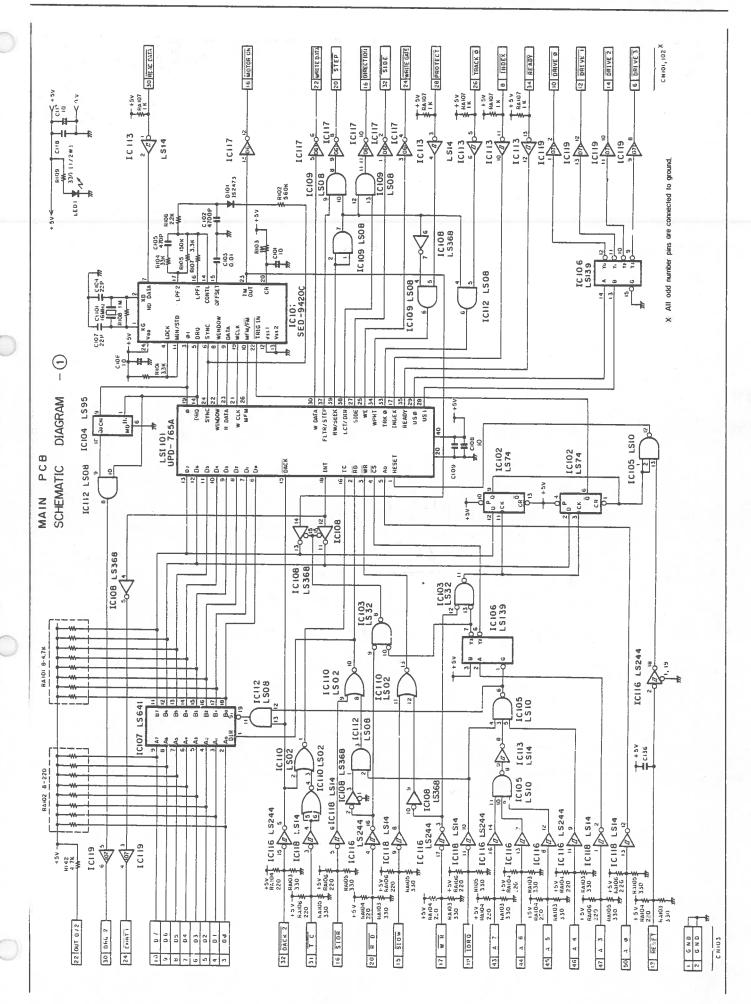

#### 2. Blockschaltbild

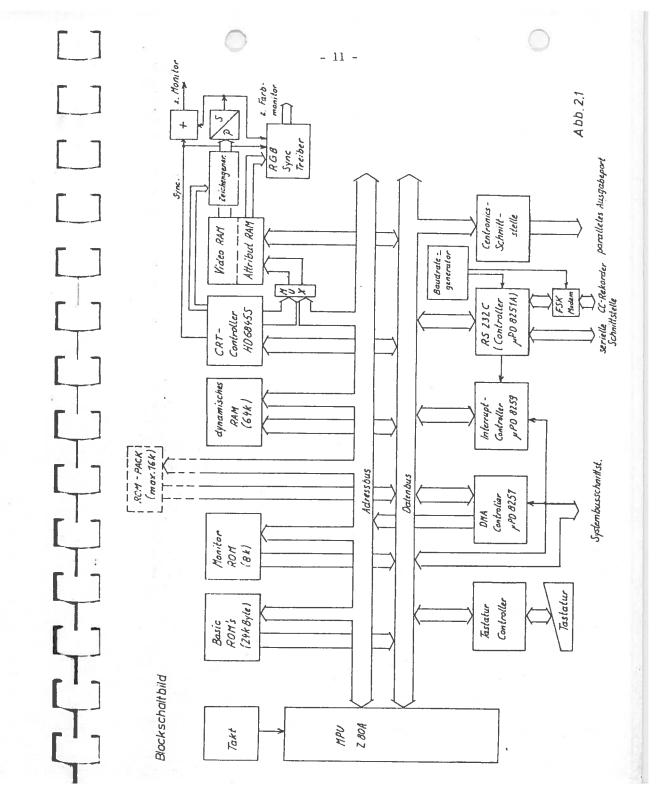

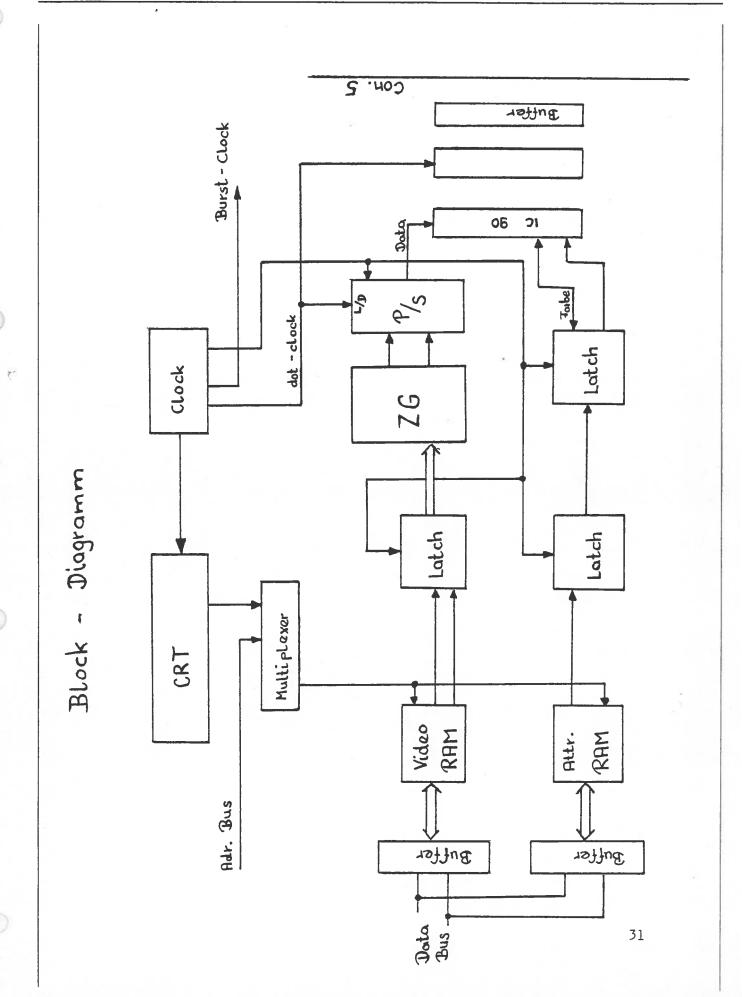

# 2.1 Erläuterungen zum Blockschaltbild

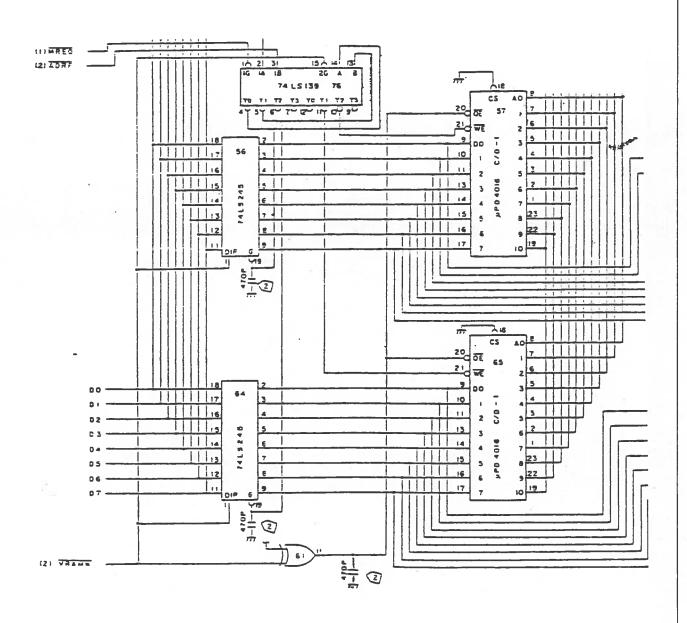

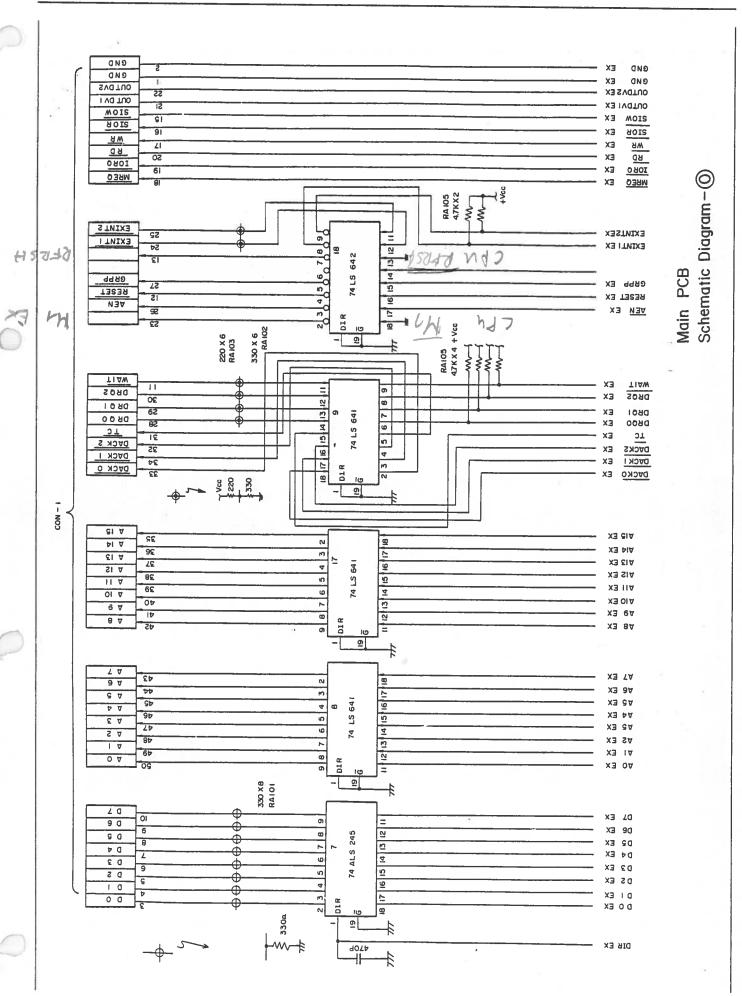

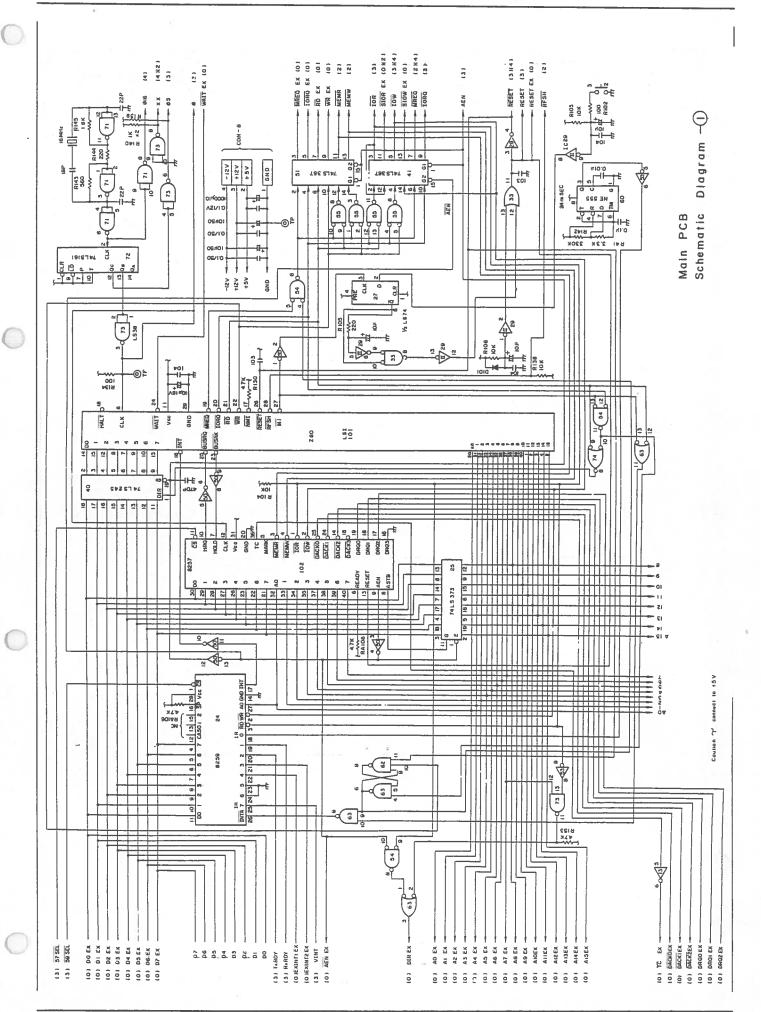

Das Blockschaltbild (Abb. 2.1) gibt einen Einblick in die logische Konfiguration des alphatronic-PC. Funktionsblöcke sind hier als Kästen dargestellt. Steuersignale, Treiberstufen und Versorgungsspannungen sind nicht eingezeichnet. Alle Funktionsblöcke sind um das Bussystem gruppiert. Das Bussystem besteht aus einem 8 Bit breiten Datenbus und einem 16 Bit breiten Adressbus. Jeder PC-interne Datenverkehr wird über den Datenbus abgewickelt. Die jeweils dazugehörende Adresse steht auf dem Adressbus. Aus der 16 Bit Breite des Adressbusses ergibt sich ein direkt adressierbarer Speicherbereich von 2°16 = 65536 Speicherworten. Dies wird oft mit dem Kürzel "64 kByte Adressbereich" angegeben. 1k (k sprich: ka) ist die Abkürzung für 1024 = 2°10 . "Byte" kennzeichnet eine 8 Bit breite Information.

Da der alphatronic-PC jedoch über 64 k Byte RAM (Random Access Memory = Speicher mit wahlfreiem Zugriff, Schreib-/ Lesespeicher) und 32 kByte BASIC bzw. Monitor ROM (Read Only Memory = nur Lesespeicher; Festwertspeicher) verfügt, reicht der direkte Adressbereich nicht mehr aus. Aus diesem Grund wird nach dem Einschalten des PC (sofern kein Floppydisklaufwerk angeschlossen bzw. kein ROM-PACK eingesteckt ist) der Inhalt der ROM-Speicher in den RAM-Speicherbereich kopiert. Der Anwender hat hiernach nicht mehr 64 kByte RAM, sondern nur noch ca. 28 k Byte zur freien Verfügung (ca. 4 kByte RAM werden vom BASC bzw. vom Monitor für Verwaltungsaufgaben benötigt).

Im Regelfall legt der Microprozessor Z80A die Adresse des als Quelle oder als Ziel angesprochenen Speicherwortes auf den Adressbus. Der Microprozessor (MPU = Micro Processor Unit) steuert das gesamte System und arbeitet die Progamme ab. Der Prozessor Z80A ist im Kapitel 3 näher beschrieben.

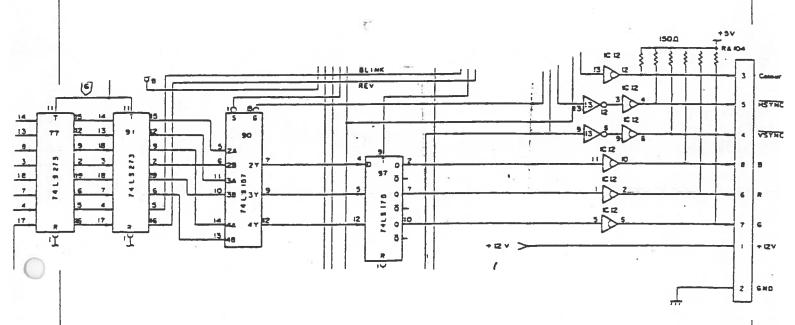

Die Bildschirmsteuerung wird von folgenden Funktionsblöcken Übernommen:

CRT-Controller (Cathode Ray Tube Controller = Bild-schirmsteuerbaustein); er übernimmt die gesamte zeitliche Steuerung des/der angeschlossenen Monitore(s).

Video-RAM; hier werden die vom Monitor darzustellenden Zeichen als 8 Bit Informationen in Speicherbytes abgelegt.

Attribut-RAM; hier werden zusätzliche Farbinformationen zu den im Video-RAM gespeicherten Zeichen abgelegt.

Zeichengenerator (Character-Generator); hierbei handelt es sich auch um einen Festwertspeicher. Er wandelt die 8 Bit Zeicheninformation mit Hilfe einer vom CRT-Controller erzeugten Zeileninformation in eine 8 \* 10 Bit Zeichenmatrix, die der graphischen Darstellung des Zeichens entspricht.

P / S (parallel/seriell-Wandlung); hier wird die jeweils 8 Bit breite Zeicheninformation in einen seriellen Datenstrom gewandelt.

Mit "Sync" sind die für den Monitorbetrieb erforderlichen Synchronisationssignale angedeutet.

Nähere Informationen finden sich in Kapitel 5.

Die weiteren Schnittstellen des PC (serielle Ein-/Ausgabe, paralleles Ausgabeport, Systembus-Schnittstelle, Tastatur) sind ebenfalls in Kapitel 5. beschrieben.

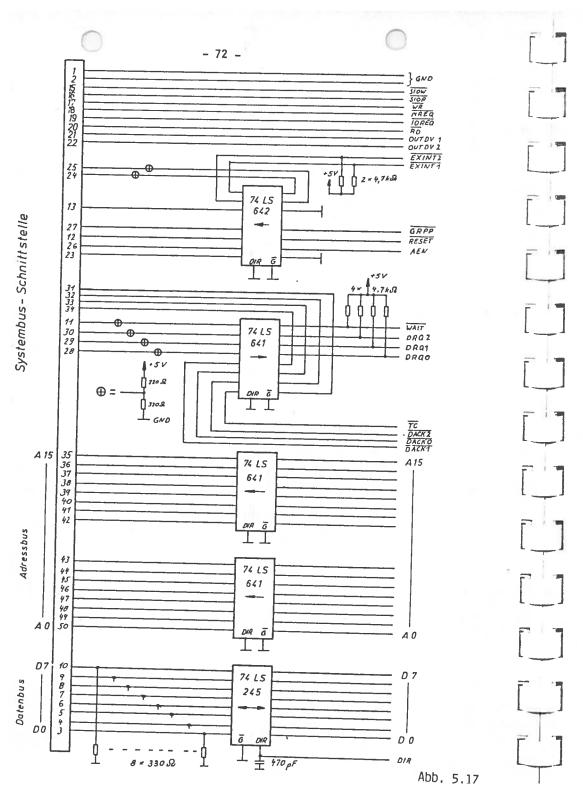

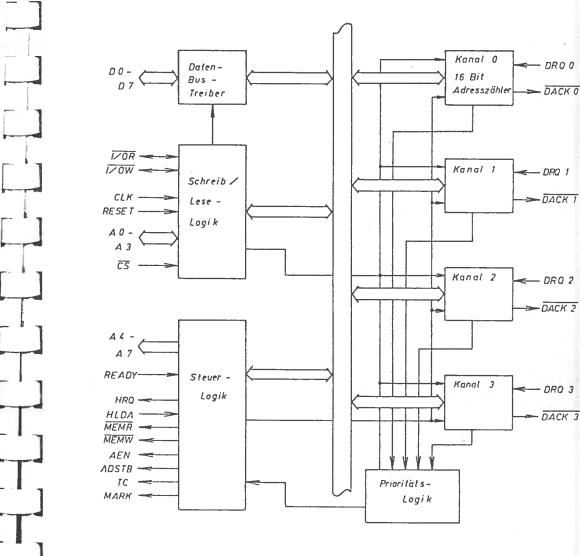

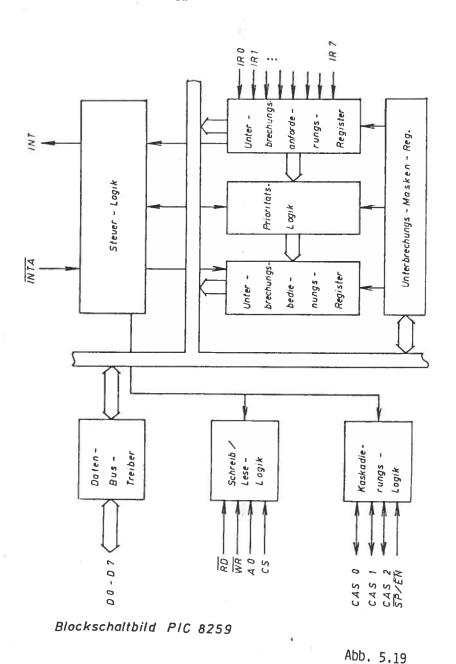

Der Unterbrechungsanforderungen bearbeitende Interruptcontroller und der DMA- (Direct Memory Access) Controller – er steuert den direkten Zugriff eines peripheren Gerätes auf den Speicher des PC; der Z80A Prozessor ist hierbei nicht aktiv – sind in Kapitel 5.6 erläutert.

Die tatsächliche Anordnung der Funktionsblöcke auf der Hauptplatine des PC ist in Abb. 2.2 dargestellt.

# 3. Mikroprozessor Z 80 A

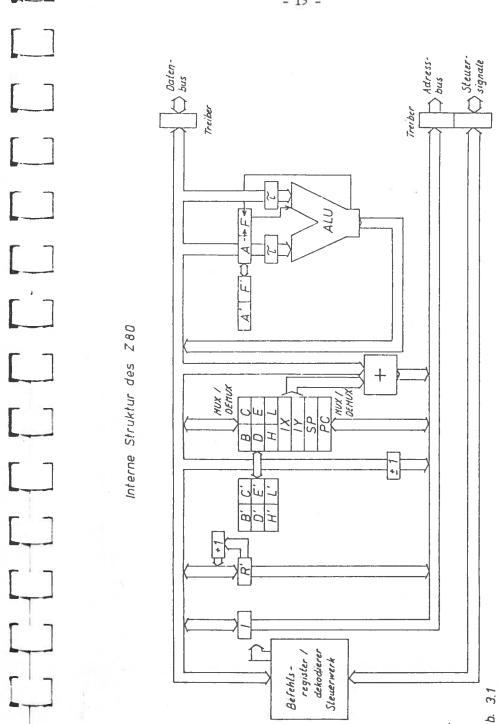

# 3.1 Architektur des Z 80

Kernstück der Zentraleinheit (CPU) des alphatronic-PC ist der Mikroprozessor (MPU) Z 80 A von Zilog (Zweithersteller z.B. Mostek, NEC). Der Z 80 A entspricht in der Struktur und seinem Befehlssatz dem Z 80. Der einzige Unterschied ist in der Verarbeitungsgeschwindigkeit zu finden. Im PC kommt der Z 80 A zum Einsatz. Er arbeitet mit einem 4 MHz Taktgenerator.

Er ist ein 8-bit Mikroprozessor, das heißt der Datenbus, über den der Prozessor Daten mit Speicherbausteinen oder Ein-/Ausgabebausteinen austauscht, ist 8 bit breit. Ferner verfügt der Prozessor über einen Adressbus und einen Steuerbus. Der Adressbus ist 16 bit breit. Er überträgt im Regelfall eine vom Prozessor erzeugte Adresse, die ein Speicherwort oder Ein-/Ausgaberegister anwählt. Der direkt adressierbare Speicherbereich beträgt also 2°16= 65536 Speicherworte (1 Wort = 1 Byte). Der Steuerbus überträgt Signale, die zur Synchronisation des Systems erforderlich sind. Zum Beispiel bestimmt der Zustand des Steuerbusses, ob das über den Adressbus angewählte Datenwort Quelle oder Ziel der Datenbusinformation ist. In Abb. 3.1 ist die interne Struktur des Z80A schematisch dargestellt.

# Erläuterungen zur Blockstruktur:

# 1. ALU (arithmetic logic unit), Rechenwerk

Das Rechenwerk übernimmt die Durchführung von arithmetischen und logischen Operationen. Hier werden Additionen, Subtraktionen (in 2er-Komplementarithmetik) und logische Grundverknüpfungen von Eingangsdaten durchgeführt. Ferner kann die ALU auch den Inhalt von 8-bit Datenworten verschieben bzw. rotieren lassen. Einzelne Bits eines Wortes können gesetzt. gelöscht oder gezielt abgefragt werden.

#### Registersatz

Der Z80 besitzt folgende Register:

A, F, B, C, D, E, H, L, IX, IY, die für den Anwender zur Verfügung stehen.

Für die Register A bis L existiert parallel ein Hintergrundregistersatz A' bis L'. Die Registersätze können nur komplett ausgetauscht werden.

2. A (Accumulator), Rechenregister

Das Rechenregister arbeitet direkt mit dem Rechenwerk zusammen.

3. B, C, D, E, H, L Universalregister, jeweils 8 bit breit

Sie können beliebige Daten beinhalten und ermöglichen eine schnelle Datenverknüpfung mit Hilfe des Rechenwerkes. Diese Register können auch paarweise angesprochen werden und zwar in den Paarungen BC, DE, HL, um 16 bit breite Informationen zu speichern.

4. Flagregister, Signalregister

Die Bits dieses Registers signalisieren den Zustand des Akku-

Es ist wie folgt aufgebaut: nicht benutzt

mulators bzw das Ergebnis der letzten Rechenoperation.

```

Ubertrag (≘ 1) (Carry-flag)

nur intern von der MPU bei BCD-

Subtraktion benutzt

. Paritäts- oder Überlaufbit, je nach Operation

. . nicht 8080-kompatibel, da hier ein Überlauf

. . bei 2er - Komplementoperationen signalisiert

. . wird. Weiterhin wird dieses Bit von der MPU

. . bei Blocktransfer und -Vergleichsoperationen

. benutzt.

. nicht benutzt

Halbübertrag (BCD-Arithmetik) (Halfcarry)

Zero (1 = Null, 0 = ungleich Null)

Vorzeichen (1 ≜ Minus, 0 ≜ Plus)

```

# 5. A', F' Hintergrundregistersatz

Mit diesen können das Rechenregister A oder das Flagregister F ausgetauscht werden. Zugriff auf diese Register ist nur mit Hilfe des Austausches möglich.

# 6. BC', DE', HL' Hintergrundregistersatz

Zugriff auf diesen Registersatz ist wie bei A' F' nur möglich, wenn er zuvor mit den Registern B bis L ausgetauscht wurde. Der Austausch aller 3 Paare ist mit nur einem Befehl (EXX) möglich.

### 1. Direkte (Absolute) Adressierung

Der Befehl gibt die Adresse(n) des Speicherwortes, mit der die Operation durchgeführt werden soll, an.

Beispiel: LD (2345), A

A > (2345)

### 2. Indirekte Adressierung

Der Befehl gibt ein Registerpaar an, dessen Inhalt auf den Operanden zeigt, der bearbeitet werden soll.

Beispiel: LD A, (HL)

(HL) > A

### 3. Implizite Adressierung

Der Befehlscode wirkt nur auf definierte Register, deren Abkürzungen nicht im Befehl auftauchen. z.B. EXX (Austausch von BC, DE, HL mit den Hintergrundregistern BC', DE', HL')

Beispiel: LD A,B

B > A

# Klammern () in der Mnemonik bedeuten immer "Inhalt von"!

# 4. Relative Adressierung

Vergleiche Punkt 11 der Befehlstypen.

Beispiel: JR C2

# 5. Unmittelbare (immediate) Adressierung

Das Datenwort steht direkt im Befehl.

Beispiel: LD A.O3H

03 > A

# 6. Indizierte Adressierung

Erweiterung der indirekten Adressierung. Der Adressregisterinhalt bleibt unverändert, es wird jedoch eine direkt im Befehl stehende Distanz (Displacement) bei der Adressenausgabe berücksichtigt.

Beispiel: SET 1,(IX+3)

#### Mischformen

Indirekt, unmittelbar: LD (HL), 22H

Indiziert, unmittelbar: LD (IX+5) 22H

# 3.2.2 Befehlstypen

Der Prozessor Z 80 A verfügt über folgende Typen von Befehlen:

1. Datentransferbefehle (sowohl 8- als auch 16 bit-Transfer)

Diese Ladebefehle haben folgendes Format:

LD Ziel, Quelle

Nach Ausführung eines solchen Befehls (8 Bit-Transfer) befinden sich in Ziel und Quelle die ursprünglichen Quelldaten. Von dieser Mnemonik weichen 2 Befehle ab (16 Bit):

PUSH Registerpaar

und

# POP Registerpaar

PUSH legt den Registerinhalt auf den Datenstapel im Speicher; POP holt den letzten Eintrag vom Stapel. In beiden Fällen wird der Stapelzeiger automatisch angepaßt. Die Austauschbefehle EX Operand 1, Operand 2 (Exchange) tauschen die Inhalte der im Argument stehenden Operanden aus. Ausnahme: EXX, hier werden die Register BC, DE, HL. mit ihren Hintergrundregistern ausgetauscht.

#### 2. 8-bit Rechenbefehle

Fast alle dieser Befehle benötigen 2 Operanden. Der erste ist immer das A (Rechen-) -Register oder eine "1" (vergleiche implizierte Adressierung). Das in der Befehlserläuterung verwendete Zeichen ":=" bedeutet "ergibt sich aus", x entspricht dem 2ten Operanden und ü (oder c) ist das Übertragsbit (Carrybit) des Flagregisters.

| MNEMONIK | BEFEHL           | ANMERKUNG           |

|----------|------------------|---------------------|

| ADD X    | A := A + X       |                     |

| ADC X    | A := A+X+ü       | (Add with Carry)    |

| SUB X    | A := A - X       |                     |

| SBC X    | A := A-X-ü       | (Substr.with Carry) |

| AND X    | Ai:= Ai ^ Xi     | logisches UND       |

| OR X     | Ai:= Ai v Xi     | logisches ODER      |

| XOR X    | Ai:= AiXi v AiXi | " ENTWEDER          |

|          |                  | -oder               |

|          |                  | (Exclusive OR)      |

| - CP X   | A - X            | Veränderung des     |

|          |                  | Flag Registers      |

|          |                  | (Compare)           |

| INC X    | X := X+1         | (Increment)         |

| DEC X    | X := X-1         | (Decrement)         |

|          |                  |                     |

Der Index i bedeutet: hier werden die Bits gleicher Wertigkeit verknüpft.

#### 3. 16 bit Arithmetik

In den hier aufgeführten Befehlen bedeutet XX ein 16 bit Register(paar) der MPU. HL meint z.B. das Paar HL.

| ADD | XX1,XX2 | XX1:=XX1+XX2 | nicht alle    |

|-----|---------|--------------|---------------|

| ADC | HL,XX   | HL:=HL+XX+ü  | Kombinationen |

| SBC | HL,XX   | HL:=HL-XX-ü  | von Register- |

| INC | XX      | XX := XX + 1 | paaren sind   |

| DEC | XX      | XX:=XX - 1   | zulässig.     |

### 4. Bitmanipulation und Test

Diese Befehle nutzen als Operanden ein Bit i eines Registers oder eines indirekt adressierten Speicherwortes X (Z ist das Null (Zero)bit des Flagregisters).

| BITi,X | Z := Xi | (Bit Test)  |

|--------|---------|-------------|

| SETi,X | Xi = 1  | (Set Bit)   |

| RESi.X | Xi = 0  | (Reset Bit) |

# 5. Speicher-Block-Verschiebe Befehle

Die hier aufgeführten Befehle dienen der Bearbeitung von Datenblöcken. Es handelt sich um 4 Befehle:

LDI, LDIR, LDD, LDDR.

Der Befehl LDI (Load with Increment) bewirkt folgendes:

Der Inhalt des Speicherwortes (1 Byte), auf das HL zeigt, wird in das von DE adressierte Wort transferriert. Anschlie-Bend wird der Inhalt der Registerpaare HL und DE um 1 erhöht. Der Inhalt des Registerpaares BC wird um 1 erniedrigt.

Der Befehl LDIR (Load with Increment and Repeat) unterscheidet sich vom vorhergehenden wie folgt:

Der Befchl LDIR führt ein LDI aus bis der Inhalt des Registers BC = 0 ist.

Der Befehl LDD (Load with Decrement) unterscheidet sich vom Befehl LDI nur dadurch, daß die Registerpaare HL, DE und BC um 1 erniedrigt werden.

Der Befehl LDDR (Load with Decrement and Repeat) arbeitet analog zum Befehl LDIR; hier werden wie beim Befehl LDD die Inhalte der Registerpaare erniedrigt bis die Abbruchbedingung BC = 0 erreicht ist.

# 6. Block-Vergleichs-Befehle

Auch hier gibt es 4 Befehle:

CPI (Compare with Increment),

CPIR (Compare with Increment and Repeat),

CPD (Compare with Decrement) und

CPDR (Compare with Derement and Repeat).

Hierbei wird jeweils der Inhalt des vom Registerpaar HL adressierten Speicherwortes vom Inhalt des Akkumulators subtrahiert und das Flagregister entsprechend beeinflußt. Die weitere Ausführung (z.B. Beeinflußung des Registerpaares BC) erfolgt analog zu den Block-Verschiebe-Befehlen.

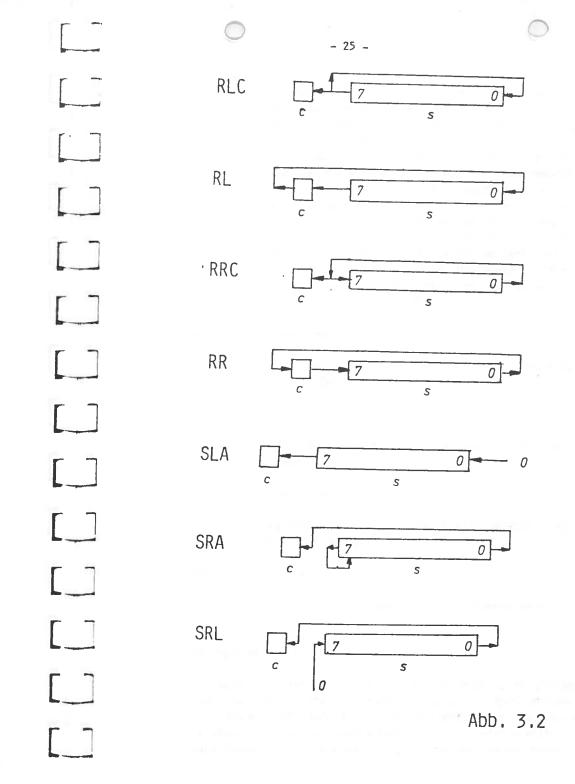

# 7. Rotations- und Verschiebebefehle

Die Funktion dieser Befehle wird durch die nachfolgend aufgeführten Schaubilder deutlich. Der dargestellte 8 bit Block ist entweder eines der MPU Register oder ein durch HL, IX bzw. IY adressiertes Speicherwort S.

ten Befehls im 2er Komplement. Das heißt, relative Sprünge sind im Bereich +127 und -128 Bytes möglich, da sich die Distanz (Displacement) zu dem Befehlszählerstand nach Ausführung des Sprungbefehls addiert.

JP XX = unbedingter Sprung zur Adresse XX, bzw. Sprung zur Adresse die von einem Registerpaar übergeben wird.

JR X = unbedingter Sprung zur Programmzähleradresse + X.

Bedingte Sprünge:

JP b,XX JR br.X

Bei Ausführung dieser Befehle wird nur ein Sprung stattfinden, wenn die Bedingung b bzw. br wahr ist.

b kann sein:

NZ (= No Zero, nicht 0)

Z (= Zero , 0)

NC (= No Carry, kein Ubertrag )

C (= Carry, Ubertrag )

PO (= Parity Odd, Parität ungerade )

PE (= Parity Even, Parität gerade )

P (= Plus )

M (= Minus )

bzw. br kann sein NZ, Z, NC, C

Der letzte, noch nicht erwähnte Sprungbefehl lautet:

DJNZ X (Decrement and Jump if Note Zero)

Hierbei handelt es sich um einen relativen Sprungbefehl. Bei der Ausführung dieses Befehls wird zunächst der Inhalt des B-Registers der MPU um 1 verringert (dekrementiert). Ist danach der Inhalt von B ungleich Null, wird ein relativer Sprung ausgeführt. Ansonsten wird der nächste Befehl abgefragt. 12. Unterprogrammaufruf und Rückkehr zum Hauptprogramm.

Bei der Erstellung von Programmen muß häufig in verschiedenen Bearbeitungsphasen eine gleiche Befehlssequenz durchlaufen werden. Derartige Befehlsblöcke können mit einem Namen versehen und außerhalb des eigentlichen Programmes (=Haupt-programm) als "Unterprogramm" abgespeichert werden. Erreicht das Hauptprogramm einen Punkt (CALL), an dem die häufig benötigte Sequenz durchlaufen werden muß, wird die Startadresse des Unterprogramms in den Befehlszähler geladen.

Weiterhin muß sich das System die Rücksprungadresse merken, um nach Ausführung der Unterprogrammsequenz zu dem Befehl hinter den Programmaufruf zurückfinden zu können. Bei Z 80-Systemen wird bei Ausführung eines Unterprogrammaufrufes der Befehlszählerinhalt auf den Datenstapel gelegt und der Stapelzeiger entsprechend angepaßt.

Es gibt zwei Unterprogrammaufrufe:

CALL XX = unbedingter Unterprogrammaufruf

CALL b, XX = bedingter Unterprogrammaufruf, b entspricht

den bei den bedingten, absoluten Sprüngen aufgelisteten Bedingungen, die zur Ausführung des

Befehls wahr sein müssen.

Die Unterprogramme enden mit einem Rücksprungbefehl, der die Rücksprungadresse wieder vom Datenstapel in den Befehlszähler lädt ( $\underline{V}$  O R S I C H I bei Stapelmanipulationen innerhalb von Unterprogrammen!).

Die Rückkehrbefehle lauten:

RET = (Return) unbedingte Rückkehr zum Hauptprogramm

RET b = bedingte Rückkehr zum Hauptprogramm, b entspricht ebenfalls den oben genannten Bedingungen, die zur Ausführung wahr sein müssen. 13. Rückkehr von Interrupt bearbeitenden Routinen.

Bricht die MPU die Bearbeitung eines Programmes durch einen Interrupt (= Anforderung an die Programmsteuerung, Unterbrechungsanforderung) ab, wird der Befehlszählerstand ebenfalls auf dem Datenstapel abgelegt. Durch die Befehle "RETI" (Return from Interrupt ) bzw. "REIN" (Return from nonmaskable Interrupt) kann nach Ausführung der den Interrupt behandelnden Routine wieder zurück zum unterbrochenen Programm gesprungen werden.

Diese Befehle arbeiten analog zu dem in 12. erläuterten Befehl "RET".

#### 14. Restart-Befehl

Dieser Befehl belegt nur 1 Byte. Er bewirkt den Sprung zu einer von 8 Speicheradressen, nachdem er den Inhalt des Befehlszählers auf den Stapel gelegt hat (wie bei CALL oder PUSH beschrieben). Die möglichen Speicheradressen sind folgende: 0, 8, 16, 24, 32, 40, 48, und 56 (dezimal). Der Befehl wirkt wie ein schneller CALL-Befehl zu einer dieser speziellen Adressen.

# 15. Ein-/Ausgabebefehle

Im Folgenden werden Ein- und Ausgabebefehle, deren Funktion analog ist, gemeinsam erläutert.

IN A,(n) / OUT A,(n)

Das periphere Gerät mit der Portadresse n wird ausgewählt. Die Daten werden mit dem Register A ausgetauscht. IN lädt die Daten von der Peripherie in den Akkumulator, OUT gibt die im Akkumulator stehenden Daten aus. Flags werden bei der Ausführung dieses Befehls nicht beeinflußt.

|        | -                    | 31 -                                                                                                                                                                                                                                                                                                                            |

|--------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | IN r,(C) / OUT r,(C) | Hier wird das periphere Gerät durch<br>Inhalt des C-Registers der MPU<br>adressiert. Der Datenaustausch ge-<br>schieht mit dem Register R.                                                                                                                                                                                      |

|        | INI / OUTI           | (IN / OUT, Increment) Auch hier wird die Peripherie durch den Inhalt des C-Registers der MPU adressiert. Der Datenaustausch ge- schieht mit dem durch das Register- paar HL ausgewähltem Speicherwort. Anschließend wird HL inkrementiert und das Register B dekrementiert. Das Flagregisterbit Z (Null) wird von B beeinflußt. |

|        | INIR / OTIR          | (IN / OUI, Increment and Repeat<br>Diese Befehle arbeiten zunächst wie<br>die zuvor beschriebenen Befehle INI/<br>OUII. Sie werden jedoch so lange<br>wiederholt, bis der Inhalt des B -<br>Registers gleich Null ist.                                                                                                          |

|        | IND / OUTD           | (IN / OUT and Decrement) Diese Befehle unterscheiden sich von INI und OUTI dadurch, daß das Regis- terpaar HL nicht erhöht, sondern um l erniedrigt wird.                                                                                                                                                                       |

|        | INDR / OTDR          | (IN / OUT, Decrement and Repeat) Hier wird analog INIR / OTIR ver- fahren, jedoch HL wie bei IND dekre- mentiert.                                                                                                                                                                                                               |

|        |                      |                                                                                                                                                                                                                                                                                                                                 |

|        |                      |                                                                                                                                                                                                                                                                                                                                 |

| pm 15: |                      |                                                                                                                                                                                                                                                                                                                                 |

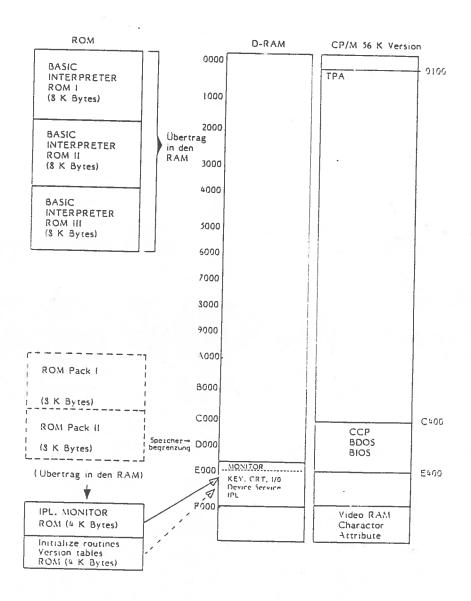

# 4. Memory Mapping

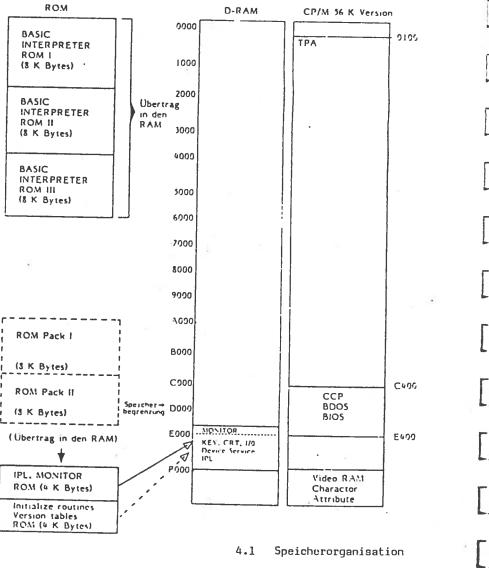

### 4.1 Speicher-Belegung

Nachstehend die grundsätzliche Speicherbelegung, die sich nach einem Hardwarereset oder dem Einschalten des alphatronic-PC ergibt, wenn kein Floppy-Disc-Laufwerk angeschlossen ist:

Adresse

: Inhalt

0000 bis 1FFF

: Basic ROM 1

2000 bis 3FFF 4000 bis 5FFF

: Basic ROM 2 : Basic ROM 3

A000 bis BFFF

: ROM PACK 1 (falls

COOO bis DFFF

: ROM PACK 2 (vorhanden

F000 bis FFFF

: Monitor ROM

(je nach

F000 bis FFFF

: Video und Attribut RAM (Auswahl

(durch

(SPORT

0000 bis FFFF : RAM

Wird der alphatronic-PC mit einer (oder zwei) Floppy-Disk-Station(en) und der Disk-Basic-Diskette betrieben, so wird der Basic-Interpreter nicht vom ROM sondern von der Diskette geladen. Das Ende des Interpreter kann dann aber nicht fest mit 5FFF angegeben werden, da je nach Eingabe bei "How many files" mehr oder weniger Pufferspeicher benötigt wird.

Bei Betrieb mit einem CP/M Betriebssystem sind die Bereiche CCP, BIOS und BDOS wie folgt verteilt:

#### Adresse

C300 bis C3AF : CCP CB00 bis D8FF : BDOS D900 bis E3FF : BIOS

# 4.2 I/O Adressen

Die nachstehende Liste beinhaltet die sedezimalen Adressen der im alphatronic-PC vergebenen I/O Adressen.

Adresse : belegt für

10 : Systemadresse

20

30 : Parallelschnittstelle (Centronics)

40 : Serielle Schnittstelle (V24, RS 232C)

11 41

50 : Video Controller

51

60

68

: DMA Controller

70 : Interrupt Controller

71

FO : Floppy Disc Controller

F8

\* Bemerkung: Diese Adressen sind nur über die Adressen A3H bis A7H und AO dekodiert

Nachträgliche Erweiterungen:

Adresse : : Erweiterung

# 5. Schnittstellenbeschreibungen

# 5.1 System Port (SPORT)

Zur Steuerung des Ein-/Ausgabeverkehrs wird das System Port benutzt. Es wird z.B. durch den Assembler-Befehl OUT 10H angesprochen. Die Bits des 1 Byte breiten Ports haben folgende Bedeutung:

| Bit O (LSB) | Zeilenlänge ( | des | Bildschirms |

|-------------|---------------|-----|-------------|

|-------------|---------------|-----|-------------|

1 = 80 Zeichen / Zeile 0 = 40 Zeichen / Zeile

Bit 1 Bildschirmdarstellung

1 = ausgeschaltet

0 = eingeschaltet

Bit 2 Cassettenrecorder oder V24

1 = V24

O = Cassettenrecorder

Bit 3 Cassettenrecorder-Fernsteuerung

1 = Motor ein

0 = Motor aus

Bit 4 Buzzer (Summer)

1 = ein

0 = aus

Bit 5 muß immer O sein

Bit 6 ROM-PACK Freigabe (enable)

1 = ROM-PACK freigegeben (enabled)

(nur wonn Bit 7 auf 0 gesetzt ist)

0 = ROM-Pack gesperrt (disabled)

Bit 7 (MSB) Freignbe des ROM Zugriffs

1 = Zugriff auf die ROM's ist gesperrt; die MPU arbeitet mit den in das RAM kopierten Daten/Befehlen

O = Zugriff auf die ROM's ist freigegeben

T-

\_\_\_

L.

Der Inhalt dieses aus zwei 4-Bit D-Flip Flops (74 LS 175) bestehenden Registers kann von der MPU nicht gelesen werden. Der Befehl IN 10H fragt ein anderes Register ab (siehe unten). Um den ausgegebenen Status kontrollieren bzw. ändern zu können, wird nach jeder Ausgabe eine Kopie des ausgegebenen Bytes in das RAM-Wort mit der Adresse E46BH geschrieben (SFFO-Byte). Nach dem Kaltstart des alphatronic-PC wird 00 an das Sytem Port ausgegeben und eine Kopie in dem SFFO-Byte abgelegt.

Mit dem Befehl IN 10H wird ein 8 Bit Port abgefragt, das den vorgegebenen Status (z.B. durch DIP-Schalter Abb. 5.1) beschreibt.

### Bedeutung der Bits:

| Bit O (LSB) | Floppy-Disk Laufwerk       |

|-------------|----------------------------|

|             | l = Laufwerk ist verfügbar |

|             | 0 = " ist nicht verfügbar  |

### Bit 1 reserviert

Bit 2, 3, 4 Auswahl des über die Tastatur zugänglichen Zeichensatzes (über den DIP Schalter wählbar)

| 0 | 0 | 0 | internationaler | Zeichensatz |

|---|---|---|-----------------|-------------|

| 0 | 0 | 1 | deutscher       | H           |

| 0 | 1 | 0 | USA             | *1          |

| 0 | 1 | 1 | französischer   | H           |

| 1 | 0 | 0 | englischer      | 11          |

| 1 | 0 | 1 | italienischer   | 11          |

| 1 | 1 | 0 | spanischer      | *1          |

| 1 | 1 | 1 | reserviert      |             |

| Bit | 5 | Druckerauswahl |

|-----|---|----------------|

|     |   |                |

- 1 = Drucker mit serieller Schnittstelle, Datenausgabe über V24 Schnittstelle

- O = Drucker mit Centronicskompatibler Schnittstelle, Datenausgabe über das Parallelport

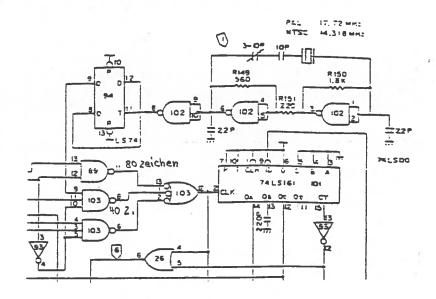

- Bit 6 Auswahl der TV-Norm

- 1 = NTSC, hierbei muß der Taktgenerator des CRT-Controller Bausteins mit einem 14,318 MHZ Schwingquarz bestückt sein

- 0 = PAL, hierzu ist ein 17,72 MHZ Schwingquarz notwendig

Bit 7 (MSB) Bildschirmperiodenüberwachung

theor.

12 us!

1 = Austastlücke

0 = es wird gerade auf dem Bildschirm geschrieben

# \* Hinweis:

Die Ländervarianten-Angaben beziehen sich auf einen Monitorstand mit der Bezeichnung B4 – 7 und größer. Soll ein Gerät auf eine andere Ländervariante umgestellt werden, so ist auch ein Austausch des Zeichengeneratorproms notwendig. Bei Mitnahme in andere Länder ist auf die unterschiedlichen Netzspannungen zu achten (ggf. muß ein entsprechender Transformator evtl. mit Frequenzumsetzer dazwischengeschaltet werden).

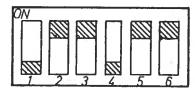

# DIF-Schalter (SW 102)

Im Gerät befindet sich auf der Platine ein DIP-Schalter mit sechs Einstellmöglichkeiten:

Schalter 1 - 3

dient zur Einstellung von Ländervarianten der Tastatur

Schalter 4

Auswahl der Druckerschnittstelle (parallel, seriell)

Schalter 5

Schalter 6

JV-Farbsystem (PAL, NTSC)

ohne Funktion

### Schaltervoreinstellung:

| 1         | 2        | 3        |                                                                                                                          |

|-----------|----------|----------|--------------------------------------------------------------------------------------------------------------------------|

| ON<br>OFF | ON<br>ON | ON<br>ON | Internat. Tastatur<br>Deutsche Tastatur                                                                                  |

|           |          | 4        |                                                                                                                          |

|           |          | OFF      | V.24 (seriell): Voreinstellung                                                                                           |

|           |          | ON       | für den europäischen Bereich<br><u>Centronics</u> (perallel): Vorein-<br>stellung für den außereuropä-<br>ischen Bereich |

|           |          | 5        |                                                                                                                          |

|           |          | OFF      | NTSC                                                                                                                     |

|           |          | ON       | PAL                                                                                                                      |

Dip-Schalter Abb. 5.1

# 5.2 Tastaturschnittstelle

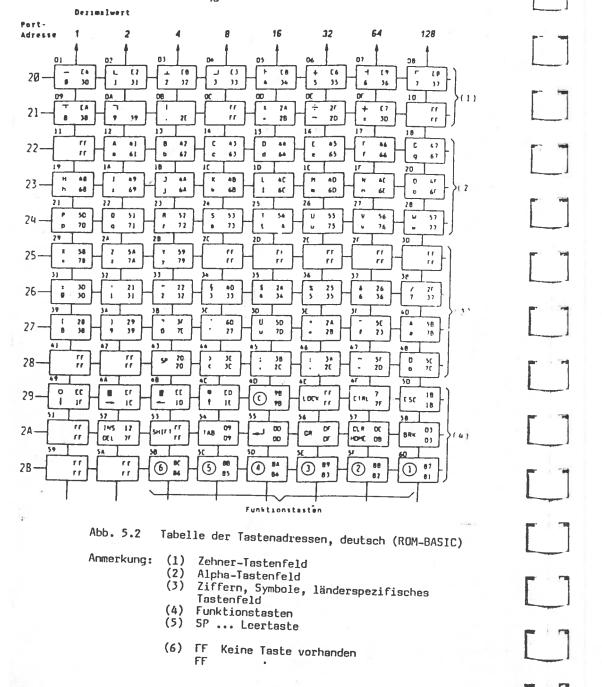

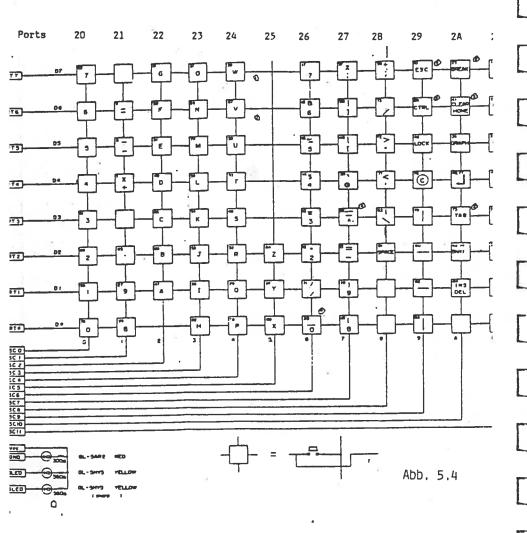

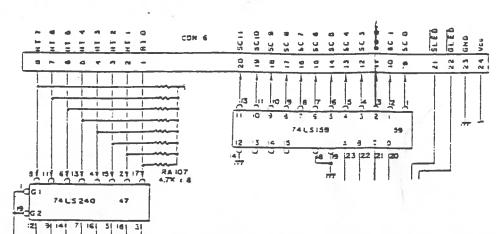

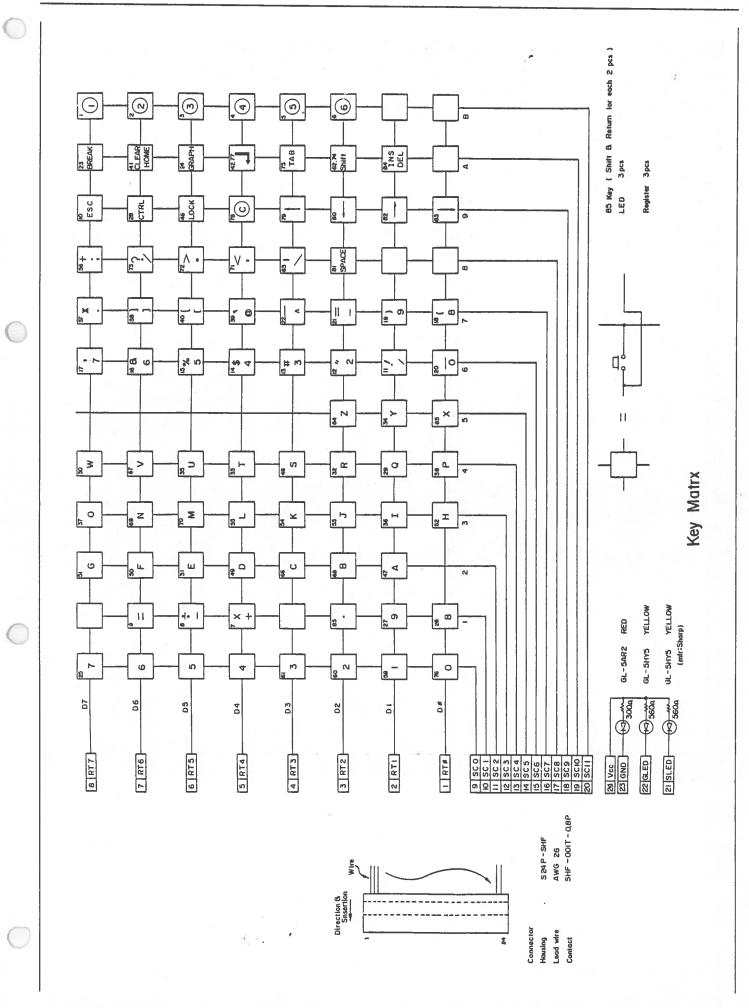

Die in das Gehäuse des alphatronic-PC integrierte Tastatur ist als Schaltermatrix aufgebaut.

Die Tastaturplatine ist über ein Kabel mit der Hauptplatine verbunden. Folgende Leitungen stellen die Verbindung her:

Versorgungsspannung (5V, GND)

- 1 Steuerleitung für die GRAPH-LED

- 1 Steuerleitung für die SHIFT-LED

- 12 Steuerleitungen zur Tastaturmatrix (SCO SC11)

- 8 Antwortleitungen von der Matrix (RTO RT7)

Aus der Anzahl der Leitungen geht hervor, das es sich hier um eine 12 x 8 Matrix mit maximal 96 Tasten handelt, die sich an den "Schnittpunkten" der Matrix befinden (das heißt: eine der Leitungen SCO – 11 wird durch Betätigung einer Taste mit einer der Leitungen RTO – RT7 verbunden werden).

Nun wird ein 10.3 msec Abfragepuls (scan time) nacneinander an jede der Leitungen SCO – SC11 gelegt und währenddessen die Antwortleitungen gelesen. Ist eine Taste gedrückt, gelangt der Puls also wieder zurück zur MPU. Die entsprechende Taste wird als betätigt erkannt. Die Antwortleitungen werden über die Portadressen 20H-2BH abgefragt. Die Steuerleitungen SCO-SC11 verbergen sich in den niederwertigen 4 Bit der Portadresse (O-B = O-11 dezimal).

#### Anmerkung:

In alphatronic-PC's mit niedrigerer Seriennummer beträgt die Abfragezeit 20.7 msec. Der Unterschied zu neueren ist in einem Monitorprogramm zu finden. Die Zeitkonstante für diese Softwareverzögerung steht in den Speicherbytes mit den sedezimalen Adressen E5F1 und E5F2:

> E5F1: DO (niederwertiges Byte) E5F2: OA (höherwertiges Byte)

Hier ist die Konstante ADO (sedezimal) = 2768 (dezimal) für die 20.7 msec maßgeblich; eine 7.5 microsec dauernde Schleife wird 2768 mal durchlaufen.

|   | Ø              | 1   | 2        | 3 | 4 | 5 | 6 | 7   | 8            | 9               | A | В | C | D   | E        | F |

|---|----------------|-----|----------|---|---|---|---|-----|--------------|-----------------|---|---|---|-----|----------|---|

| Ø |                | I   | SP       | 9 | 6 | P | ` | Р   |              |                 |   |   |   |     | г        |   |

| 1 |                |     | !        | 1 | A | Q | a | q   | 1            |                 |   |   |   |     | ٦        |   |

| 2 |                | INS | -        | 2 | 8 | R | Ь | r   | 2            |                 |   |   |   | 500 | L        |   |

| 3 | BRK            |     | ,        | 3 | С | S | С | s   | 3            |                 |   |   |   |     | ١        |   |

| 4 |                |     | S        | 4 | D | T | d | t   | 4            |                 |   |   |   |     | _        |   |

| 5 |                |     | 2        | 5 | Ε | U | e | U   | (3)          |                 |   |   |   |     | 1        |   |

| 6 |                |     | 8        | 6 | F | ٧ | f | ٧   | 6            |                 |   |   |   |     | +        |   |

| 7 | BEL            |     | -        | 7 | 6 | W | g | w   | SHILI        |                 |   |   |   |     | +        |   |

| 8 | <b>®</b><br>BS |     | (        | 8 | н | χ | h | ×   | 34JF1        |                 |   |   |   |     | F        |   |

| 9 | TAB            |     | )        | 9 | 1 | Y | 1 | У   | SHJГТ        | 9₹              |   |   |   |     | 4        |   |

| A | ⊕<br>LF        |     | (x)      | : | J | Z | j | z   | (a)          | 0.1<br>145<br>0 |   |   |   |     | <b>-</b> |   |

| В | HOME           | ESC | +        | ; | К | X | k | ä   | SHIFT        | 0               |   |   |   |     | _        |   |

| С | CLR            | -   | ,        | < | Ĺ | ۵ | 1 | 0   | SHIFT<br>(6) |                 |   |   |   |     | 0        |   |

| D | CR             | -   | -        | • | н | 0 | m | Ü   |              |                 |   |   |   |     | •        |   |

| Ε |                | 1   |          | , | N | ^ | n | В   |              |                 |   |   |   |     | 8        |   |

| F |                | 1   | /<br>(÷) | ? | 0 |   | 0 | DEL |              |                 |   |   |   | GR  |          |   |

Abb. 5.3 Deutscher Zeichen-Code (ROM-BASIC)

Anmerkung: (\*) = keine Taste auf der Tastatur

# 5.3 Serielle Schnittstelle

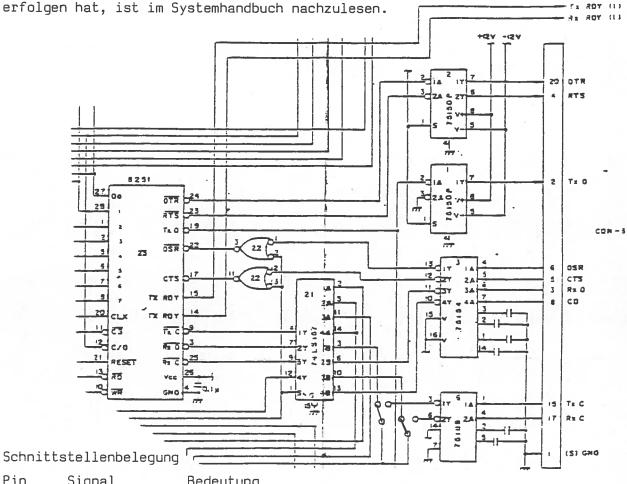

Der alphatronic-PC ist mit einer seriellen Schnittstelle nach DIN 66020 bzw. EIA RS 232C bzw. CCIIT V.24 ausgerüstet. Die serielle Schnittstelle ist durch den integrierten Schaltkreis 8251A (Siemens, Intel, Nec, ...) mit nachgeschalteten pegelanpassenden Schaltkreisen SN 75150, SN 75154 und SN 75189 (Texas Instruments) realisiert. Das Übertragungsverfahren ist durch Voreinstellung von dem PC-internen Rangiersteckverbinder und die Initialisierung des Ein-/Ausgabebausteins 8251A von der Start-Routine in folgenden Modus gesetzt:

A Synch 16

PBit

No Parity

2 Stopphits

asynchrone serielle Datenübertragung nach V24 (RS 232C) mit 4800 Bd (Baud, nach Baudot); jedes Wort besteht aus 1 Startbit, 2 Stoppbits; zwischen Start und Stopbits befinden sich jeweils 7 Datenbits sowie 1 Paritätsbit (gerade Parität, even Parity)

Der USART (universal synchronous/asynchronous receiver and transmitter) 8251A bietet im Zusammenhang mit dem Baud-Rate-Generator und dessen Rangiersteckverbinder jedoch eine Vielzahl weiterer Übertragungsprotokolle.

1. Ubertragene Pegel

Bei dem hier angewandten Verfahren wird eine logische Ø als Spannung von ca +10 V gesendet; eine logische 1 entspricht einer Spannung von ca -10 V. Ein Empfänger erwartet laut den Datenblättern der Treiber-IC's für eine Ø, eine Spannung die größer ist als +3 V und für eine 1 eine Spannung die zwischen -3V und -12V liegt.

2. Asynchrone Datenübertragung

In diesem Betriebsmodus sendet bzw. empfängt der USART Baustein serielle Daten, deren Format durch Steuerregister festgelegt ist. Jedes zu sendende Datenwort wird, nachdem es vom parallelen Datenbus des Prozessors in das Senderegister geladen wurde, seriell ausgesendet. Die Länge eines seriellen Datenwortes ist durch die Programmierung eines Steuerregisters

vorgegeben. Sie kann 5, 6, 7 oder 8 bit betragen. (Werden z.B. 5 Bit Datenworte gesendet, sind die 3 höherwertigen Bits der 8 Bit Datenbusinformation verloren). Jedem gesendeten Wort wird ein Startbit vorangestellt. Hierbei wird nach einer Pause oder einem Stoppbit (logisch Ø) eine 1 gesendet. Es folgen die Datenbits. Nach den Datenbits kann ein Paritätsbit gesendet werden. Man unterscheidet gerade (even) und ungerade Parität (odd parity). Gerade Parität heißt, daß in jedem Datenwort die Quersumme aller gesendeten Bits gerade ist; bei ungerader Parität ist die Summe ungerade. Dieses Paritätsbit ermöglicht dem Empfänger das Erkennen von Übertragungsstörungen. Den Abschluß eines übertragenen Datenwortes bildet die Stoppinformation. Sie kann 1, 1,5 oder 2 Bit lang sein.

Als Empfänger kann der USART serielle Datenworte entsprechend der eingestellten Baudrate, Datenwortlänge und Parität erkennen und dem Prozessor parallel anbieten. Vom PC gesendete Daten können am Pin 2 des Schnittstellenverbinders abgegriffen werden (TxD); vom PC zu empfangende Daten können an den Pin 3 (RxD) gelegt werden. Das Bezugspotential (Masse) liegt an Pin 7.

Bei synchroner Datenübertragung entfallen Start- und Stopbits.

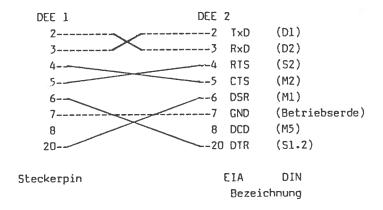

Sowohl Sender als auch Empfänger sind mit einem eigenen Taktgeber ausgerüstet. Beide Seiten müssen auf die gleiche Übertragungsgeschwindigkeit eingestellt sein; eine Synchronisation der beiden Takte ist nicht erforderlich. Der Abtastzeitpunkt für die beiden Takte wird digital bestimmt. Zu diesem Zweck ist es erforderlich, daß die Taktgeberfrequenz ein Vielfaches (progammierbar 16 oder 64) der Baudrate ist. Typische Zusammenschaltung von 2 Datenendeinrichtungen (DEE):

# 3. Synchrone Datenübertragung

Der Unterschied zu asynchronen Datenübertragung besteht darin, daß der als Sender arbeitende USART-Baustein nach der Initialisierung und, falls kein zu sendendes Zeichen im Baustein vorhanden ist, Synchronisationszeichen (SYNC-Zeichen) automatisch sendet. Zum Empfangsbetrieb muß der USART-Baustein nach Übergabe der Modus- und Sync-Worte in den Suchmodus geschaltet werden. Nach Wahl der internen Zeichensynchronisation testet der Empfänger das Signal am Dateneingang (RxD) jeweils mit den steigenden Flanken des Empfangstaktes (RxC) ab und vergleicht nach Empfang eines Bits die zuletzt empfangenen Bits mit dem festgelegten Sync-Zeichen. (Ein Doppel-Sync-Modus kann programmiert werden. In diesem Modus werden 2 aufeinanderfolgende Worte untersucht. Diese Wortfolge muß den Bitkombinationen der Worte SYNC1 und SYNC2 entsprechen). Ist ein solches Zeichen (oder Doppelzeichen) empfangen worden, wird dies durch den H-Pegel des SYNDET/BD-Bits im Statusregister des USART markiert und der Suchmodus beendet. Dieses Bit wird auch bei Empfang eines Sync-Wortes (bzw. Doppelwortes) außerhalb des Suchmodus gesetzt.

Der programmierbare Modus der externen Zeichensynchronisation des USART-Bausteins kann beim PC durch Umlöten der Lötbrücken (Abb. 5.5) 1 - 2 und 4 - 5 verwendet werden.

Rangierverbinder zur Einstellung der Ausgangsspannung an PIN 1 und 4 der Cassettenrecorderschnittstelle

Abb. 5.5

Lötbrücken zur Verbindung des USART mit dem 2 vom Steckverbinder Empfangs- bzw. zum USART vom internen Sendetakt Baudrale generator

Baudrate Rangierverbinder 1200 600 300

Auslieferungszustand

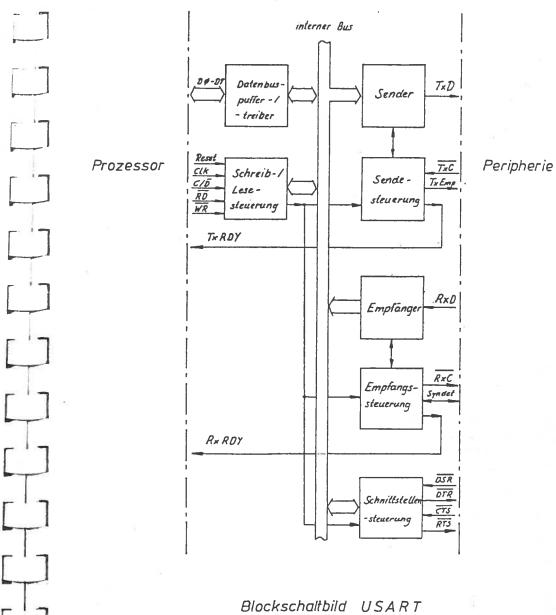

Blockschaltbild USART

mild Kompatibel mil

Abb. 5.6 Skokverbindeg

Im Blockschaltbild ist die interne Struktur des USARI-Bausteines schematisch dargestellt. In der Mitte befindet sich der interne Bus. Auf der linken Seite erkennt man die MPU-orientierten Funktionsblöcke und die von ihnen zum Prozessor verdrahteten Leitungen. Auf der rechten Seite sind die zur Kommunikation mit der Peripherie arbeitenden Strukturblöcke mit ihren erforderlichen Anschlüssen dargestellt. Eine Ausnahme bilden die Leitungen TxRDY und RxRDY. Diese beiden Signale sind zum Interruptcontroller geführt. Hierdurch wird eine interruptgesteuerte Ein-/Ausgabe, z.B. im Hintergrundbetrieb, ermöglicht.

Anzumerken ist, daß alle MPU bzw. PC-internen Bussignale ohne Einfluß auf den USART sind, solange der CS-Eingang inaktiv ist, d.h. solange er nicht durch ein Programm über den Z 80-Prozessor adressiert wurde.

Die Funktion des 8251A wird durch Software festgelegt. Dies erfolgt durch die Übergabe von Steuerworten (Modus-, Kommando- und ggf. Syncl- und Sync2- Wort), die in Registern des USART gespeichert werden. Diese Register legen den Betrieb des Bausteins fest, bis sie durch neue Instruktionen verändert werden. Der Prozessor kann jederzeit den Status des Bausteins durch Einlesen eines der Statusworte abfragen.

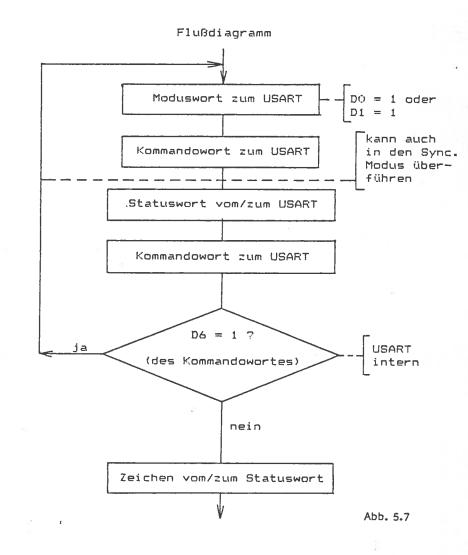

# Programmierung des USART

Um nach dem Empfang eines Reset-Pulses (z.B. nach dem Einschalten) die gewünschten Funktionen wahrnehmen zu können, muß der USART Baustein zunächst durch die Übergabe von 2 (asynchroner Datentransfer), 3 oder 4 (synchroner Datentransfer mit 1 oder 2 Sync-Zeichen) Steuerworten initialisiert werden. Die beiden immer zu übertragenden Worte sind das Moduswort und das Kommandowort. Bei der Programmierung des Bausteins wird nur eine Adresse verwendet; die Programmierung muß daher in einer definierten Reihenfolge vonstatten gehen, um zu gewährleisten, daß die Steuerinformationen in dem richtigen Steuerregister abgelegt werden. Die Adresse des Steuerregisters lautet im PC: 41 (Sedezimal).

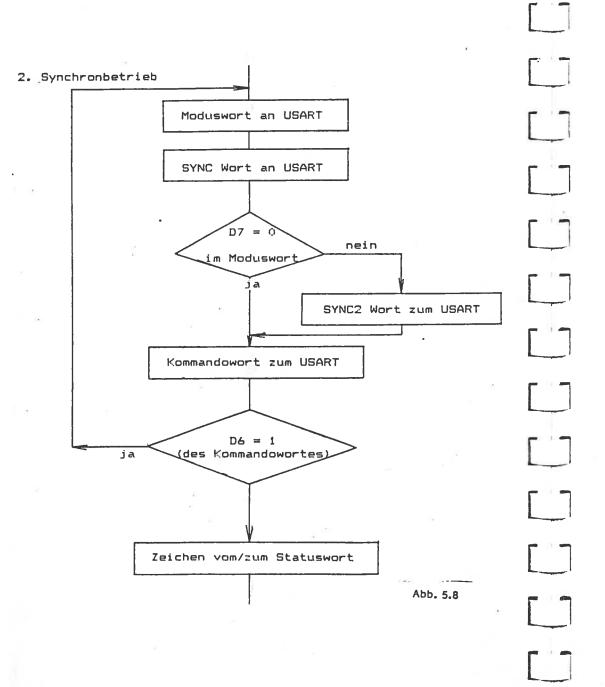

Der Ablauf einer Initialisierung des USART ist in den nachfolgenden Flußdiagrammen dargestellt. Die Reihenfolge der Steuerinformationen ist bindend.

# 1. Asynchronbetrieb:

Aus den folgenden Tabellen ist der Aufbau der erforderlichen Steuerworte zu entnehmen. Mit dem Moduswort wird die Betriebsart und auch das Datenformat festgelegt.

|    |     |     |      |      |       |     |     | •   |     |       |         |      |      |        |     |

|----|-----|-----|------|------|-------|-----|-----|-----|-----|-------|---------|------|------|--------|-----|

| D7 | D6  | D5  | D4   | D3   | D2    | D1  | Đ   | 0   |     |       |         |      |      |        |     |

| 52 | Sl  | EP  | PE   | L2   | L1    | B2  | Е   | 31  |     |       |         |      |      |        |     |

| •  | •   |     |      | •    |       | •   |     |     | Be  | trieb | sart    |      | Free | qu.Tei | ler |

|    |     |     | •    |      | •     | 0   | 0   |     | Syı | nc.Be | trieb   |      |      | 1      |     |

| •  |     |     | •    |      | •     | 0   | 1   |     | As  | ync.  | 4.5     |      | 9    | 1      |     |

|    |     |     | •    | •    | •     | 1   | 0   |     | As  | ync.  | 11      |      |      | 16     |     |

|    |     |     | •    | •    | •     | 1   | 1   |     | As  | ync.  | 79      |      |      | 64     |     |

|    | •   | •   |      | •    | •     |     |     |     |     |       |         |      |      |        |     |

| •  | •   | •   |      |      | •     | Ze: | ich | en. | län | ge    |         |      |      |        |     |

|    |     |     | •    | 0    | 0     | 5   | Вi  | .t  |     |       |         |      |      |        |     |

|    | •   |     |      | 0    | 1     | 6   | Вi  | t   |     |       |         |      |      |        |     |

|    |     | •   | •    | 1    | 0     | 7   | Bi  | t   |     |       |         |      |      |        |     |

| •  | •   |     | •    | 1    | 1     | 8   | Вi  | t   |     |       |         |      |      |        |     |

| •  |     |     | •    |      |       |     |     |     |     |       |         |      |      |        |     |

| •  |     |     | •    | Pa   | rität | sbi | t   |     |     |       |         |      |      |        |     |

| •  |     |     | 0    | ohi  | ne    |     |     |     |     |       |         |      |      |        |     |

| •  |     |     | 1    | mii  | t e   |     |     |     |     |       |         |      |      |        |     |

| •  |     |     |      |      |       |     |     |     |     |       |         |      |      |        |     |

|    |     |     | Par  | itä  | tsart |     |     |     |     |       |         |      |      |        |     |

|    |     | 0   | unc  | jera | de    |     |     |     |     |       |         |      |      |        |     |

|    |     | 1   | _    | ade  |       |     |     |     |     |       |         |      |      |        |     |

|    |     |     |      |      |       |     |     |     | •   |       |         |      |      |        |     |

|    |     |     |      |      |       |     |     |     |     |       |         |      |      |        |     |

|    |     |     |      |      |       |     |     | = . | •   | •     |         |      |      |        |     |

|    |     | Asy | nc.E | etr: | ieb   |     |     |     |     | . 5   | Sync.Be | etri | .eb  |        |     |

|    |     |     |      |      | pbits | ;   |     |     |     | . 7   | eicher  | nsyc | hron | isatio | n   |

| 0  | 0   |     |      |      | ssig  |     |     |     |     | 0 i   | intern  |      |      |        |     |

| D  | 1   | 1   | Bit  |      |       |     |     |     |     | 1 6   | extern  | (ni  | cht  | PC)    |     |

| 1  | 0   | 1.5 | Bit  |      |       |     |     |     |     |       |         |      |      |        |     |

| 1  | 1   | 2   | Bit  |      |       |     |     |     |     | SYNO  | -Zeich  | nen  |      |        |     |

| _  | 0.0 |     |      |      |       |     |     |     | 0   | Dopp  | oel Sy  | nc.  | Zeic | hen    |     |

|    |     |     |      |      |       |     |     |     | 1   | Einf  |         | 19   | **   |        |     |

|    |     |     |      |      |       |     |     |     |     |       |         |      |      |        |     |

| EH | IR   | RTS | ER   | SBRK   | R×EN   | DTR   | TxEN    |                         |

|----|------|-----|------|--------|--------|-------|---------|-------------------------|

| •  | •    | •   | 7    |        | •      | •     | •       |                         |

| •  | •    | •   | •    | •      |        |       | •       | Sender freigeben        |

| •  |      | •   | •    | •      |        | •     | 0       | nein                    |

|    | •    | •   | •    |        |        | •     | 1       | ja                      |

|    |      |     | •    | •      |        | •     |         |                         |

|    |      | •   | •    |        | •      | •     | Ausg    | ang DTR setzen          |

| •  | •    | •   | •    |        | •      | 0     | H-Pe    | gel                     |

| •  | •    | •   | •    | •      | •      | 1     | L-Pe    | gel                     |

| •  | •    | •   |      | •      | •      |       |         |                         |

|    | •    | •   | •    | •      | •      | Empf  | änger   | freigeben               |

| •  | •    | •   | •    | •      | 0      | nein  | 151     |                         |

| •  | •    | •   | •    | •      | 1      | ja    |         |                         |

| •  | •    | •   | •    | •      |        |       |         |                         |

| •  | •    | •   | •    | •      | Bre    | ak-Zu | stand   | (L-Pegel) senden        |

| •  | •    | •   | •    | 0      | nei    | n     |         |                         |

| •  | •    | •   | •    | 1      | ja     |       |         |                         |

| •  | •    | •   | •    |        |        |       |         |                         |

| •  | •    | •   | •    | Fehle  | rbits  | (FE,  | OE, PE  | ) Stat.Reg zurücksetzen |

| •  | •    | •   | 0    | nein   |        |       |         |                         |

| •  | •    | •   | 1    | ja     |        |       |         |                         |

| •  | •    | •   |      |        |        |       |         |                         |

| ٠  | •    | •   |      | gang R | TS set | zen   |         |                         |

| ٠  | •    | 0   | H-P  | egel   |        |       |         |                         |

| •  | •    | 1   | L-P  | egel   |        |       |         | 30.7                    |

| •  | •    |     |      |        |        |       |         |                         |

| •  | •    | näc | hste | s Steu | erwort | ist   | Modus_l | wort -                  |

| •  | 0    | nei | n    |        |        |       |         |                         |

| •  | 1    | ja  |      |        |        |       |         |                         |

| •  |      |     |      |        |        |       |         |                         |

| •  |      |     | us s | tarten | ? (nu  | r im  | Synchr  | onbetrieb)              |

| 0  | neir | 1   |      |        |        |       |         |                         |

| 1  | ja   |     |      |        |        |       |         |                         |

|    |      |     |      |        |        |       |         |                         |

Das Statuswort erlaubt dem Prozessor das Erkennen einer Reihe von Zuständen der peripherieorientierten Steuerpins und das Auftreten von Übertragungsfehlern auf dem seriellen Übertragungsweg. Der Inhalt des Statuswortes wird während des Auslesens vom Prozessor nicht geändert.

```

D2

D1

DO

PE TXEMTY RXEMPTY TXRDY

Sende Register frei

nein

ja

Zeichen im Empfangsregister

nein

ja

beide Senderegister leer

nein

ja

Paritätsfehler beim Empfang

nein

0

ja

Uberlauffehler beim Empfang

nein

ja

Rahmen nicht erkannt

nein

ja

Sync- Zeichen oder Break erkannt

nein

ja

Pegel am Eingang DSR

H-Pegel

L-Pegel

```

Über den Baud-Rate Generator können dem USART Baustein je nach Stellung des Rangiersteckers (siehe Abb. 2.2 u. 5.5) verschiedene Frequenzen angeboten werden. Diese Frequenzen entsprechen jeweils einer bestimmten Baudrate (denn per Programm wurde schon der Teilungsfaktor 16 für den USART eingestellt).

| Rangi | erstecker | Frequenz | Baudrate  |

|-------|-----------|----------|-----------|

|       | 1         | 153600 H | z 9600 Bd |

| ×     | 2         | 76800 H  | z 4800 Bd |

|       | 3         | 38400 H  | z 2400 Bd |

|       | 4         | 19200 H  | z 1200 Bd |

|       | 5         | 9600 H   | z 600 Bd  |

|       | 6         | 4800 H   | z 300 Bd  |

|       |           |          |           |

x = Werkseitige Einstellung

Würde der programmierbare Teilungsfaktor 64 gewählt, erstreckte sich der durch den Rangierstecker einstellbare Bereich von 75 bis 2400 Bd; wird der Faktor 1 programmiert, ist ein externer Taktgenerator erforderlich. Hierbei wird im Synchronbetrieb oder im ISO-Synchronbetrieb übertragen. Ist der ISO-Synchronbetrieb gewählt worden, muß ein Baudrategenerator an beide Datenendgeräte angeschloßen werden. Die Verbindung des externen Taktgenerators mit dem PC erfolgt an den Anschlußpins 15 (TxC) und 17 (RxC) des V24 Steckers. Außerdem müssen auf der Hauptplatine des PC zwei Lötbrücken geändert werden. Die Position der Lötbrücken auf der Hauptplatine ist aus Abb. 2.2 ersichtlich, die jeweiligen Verbindungen gehen aus Abb. 5.5 hervor.

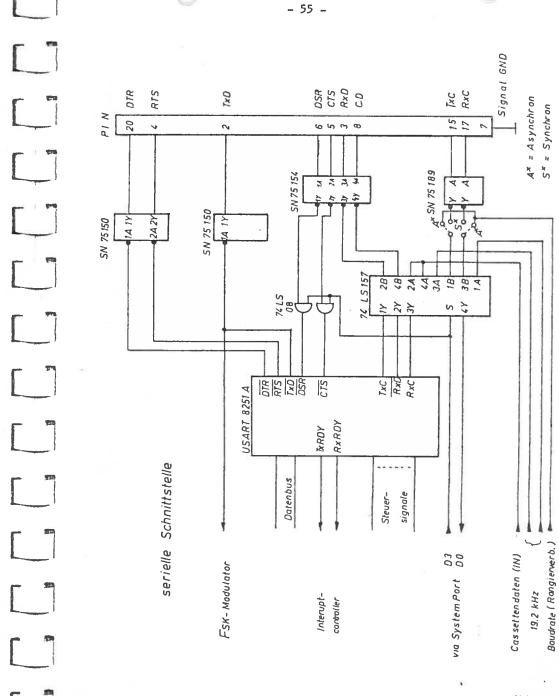

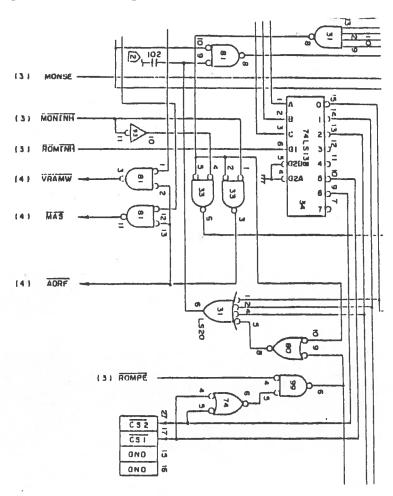

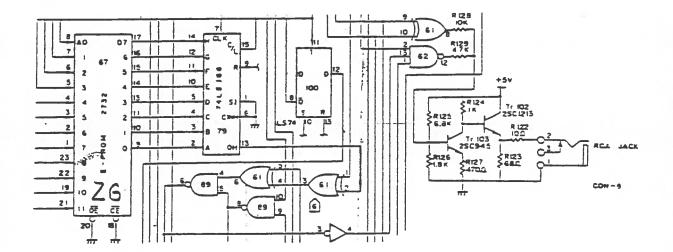

Die Schaltung der seriellen Schnittstelle ist in Abb. 5.9 dargestellt. Neben dem USART-Baustein erkennt man die pegelanpassenden IC's der SN 75-Serie. Der Multiplexer des Typs 74 LS 157 wird vom SPORT angesteuert. Er schaltet zwischen Cassettenrecorderbetrieb und serieller Schnittstelle um (siehe auch Kapitel 5.1. und 5.4).

Die Adressen des USART-Bausteins sind im PC: 41 H für Modus-, Kommando- und Statuswort und 40 H für die zu sendenden bzw. zu empfangenden Daten. Der Baustein wird vom Monitorprogramm des PC (Version 2.0/25. Juli 83) wie folgt initialisiert (kein Cassettenrecorderbetrieb, hierzu siehe Kap. 5.4).

| Befehlsadresse (H) | OP-Code  | Mnemonik      | Anmerkung |

|--------------------|----------|---------------|-----------|

| EF34               | 3E FA    | LD A,OFAH     | 1         |

| EF36               | D3 41    | OUT 41H,A     |           |

| EF38               | 3E 37    | LD A,037H     | 2         |

| EF3A               | D3 41    | OUT 41H,A     |           |

| EF3C               | 3A E4 68 | LD A,(SFFO)   | 3         |

| EF3F               | CB 07    | SET 2,A       |           |

| EF41               | DE 10    | OUT (SPORT),A |           |

| EF43               | 32 E4 68 | LD (SFFO),A   |           |

# Anmerkungen:

- Das Moduswort FA wird in des A-Register der MPU geladen und dann an den USART ausgegeben. Das Moduswort bewirkt folgende Einstellungen:

- 2 Stoppbits je Wort

- gerade Parität

- das Paritätsbit wird Übertragen (die MPU hat hierauf keinen Zugriff)

- 7 Datenbits werden pro Datenwort übertragen

- Asynchronbetrieb mit einem Teilerverhältnis Taktfrequenz zu Baudrate von 16

- Das Kommandowort 37(H) wird in das A-Register der MPU geladen und dann an den USART ausgegeben. Es bewirkt folgende Einstellungen:

das nächste Steuerwort wird wieder ein Kommandowort sein

der Ausgang RTS wird auf L-Pegel gelegt die Fehlerbits des Statuswortes (PE, OE, FE) werden gelöscht

der Empfänger des USART wird freigegeben

der Ausgang DTR wird auf L-Pegel geschaltet der Sender wird freigegeben

3. Das A-Register wird mit dem SFFO-Byte geladen. Dieses Byte enthält die zuletzt an das die Peripherie steuernde System-Port (SPORT) ausgegebene Information. Dieses Port schaltet z.B. den seriellen Datenstrom vom USART entweder zu den pegelanpassenden IC's der V24 Schnittstelle oder zu dem FSK Modulator der Cassettenschnittstelle (siehe weiter unten). Der nächste Befehl setzt das Bit 2 des A-Registers und gibt das Byte an das System Port aus und speichert diesen neuen Status auch im SFFO-Byte. Dieses gesetzte Bit 2 bewirkt, das serieller Datenstrom nun über die V24 Schnittstelle abgewickelt wird.

Belegung des 25-poligen Steckers:

| Pi       | <u>n Si</u> | gnal |           | Bedeutung                                         |

|----------|-------------|------|-----------|---------------------------------------------------|

|          | RS 23       | 2C   | V-24      |                                                   |

| 1        |             | NC   |           |                                                   |

| out 2    | TxD         |      | Dl        | Transmit Data, Sendedaten                         |

| PN 3     | R×D         |      | D2        | Receive Data, Empfangsdaten                       |

| DUT 4    | RTS         |      | <b>S2</b> | Request to Send, Sendeteil ein                    |

| /N 5     |             |      | M2        | Clear to Send, Sendebereitschaft                  |

| 1W 6     | DSR         |      | Ml        | Data Set Ready, Emfangsbereitschaft               |

| ground 7 | GND         |      | E2        | Signal Ground, Betriebserde                       |

| 9 -      | 14          | NC   |           |                                                   |

| 15       | TxC         |      | 12        | Transmit Clock, Sendetakt                         |

| 16       |             | NC   |           |                                                   |

| 17       | RxC         |      | T4        | Receiver Clock, Empfangstakt                      |

| 18       |             | NC   |           |                                                   |

| 19       |             | NC   |           |                                                   |

| 041 20   | DTR         |      | 51.2      | Data Terminal Ready, Endgerät be-<br>triebsbereit |

NC = nicht belegt

8 Courier Delect

# 5.4 Cassettenschnittstelle

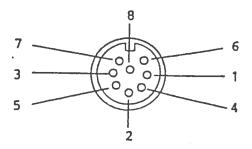

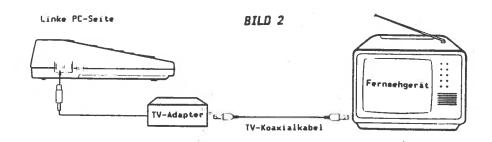

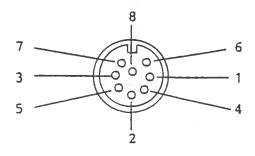

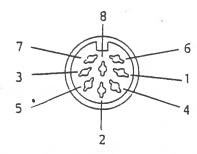

Der alphatronic-PC besitzt für das Laden und Speichern von Programmen eine Cassettenschnittstelle. Zum Anschluß eines handelsüblichen Recorders befindet sich an der linken Seite des PC, neben der RGB-Buchse, eine 8-polige DIN-Buchse zum Anschluß eine Recorders.

Für einwandfreie Funktion des Basic "CLOAD"-Befehls ist der Anschluß "Ear" (2 Kopfhöhrer) eines Cassettengerätes erforderlich. Das Cassettenrecorderkabel des PC sieht diesen Anschluß schon vor.

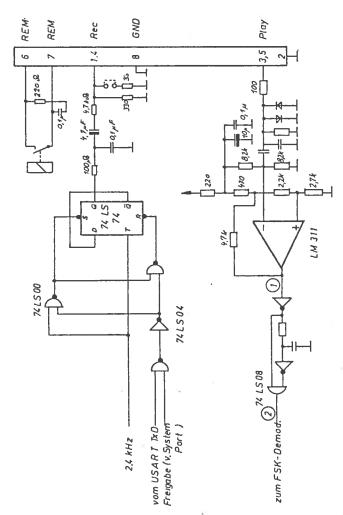

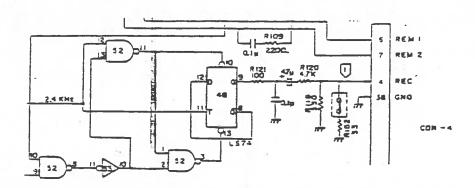

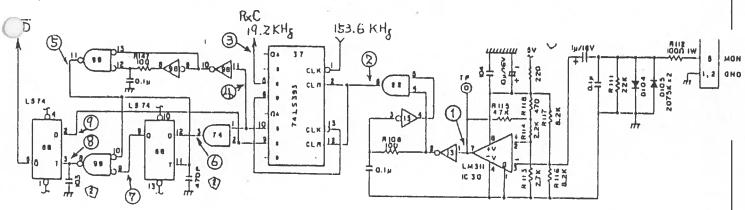

Zur Aufzeichnung auf Compactcassetten wird der vom USART Baustein 8251A (siehe Kapitel "Serielle Schnittstellen") parallel/seriell gewandelte Datenstrom zu einem FSK-Modulator geleitet (FSK = Frequency Shift Keying). Bei diesem Verfahren wird jedem der beiden logischen Pegel eine Frequenz zuge-ordnet.

Der USART ist durch die Programmierung auf ein Teilungsverhältnis f/Bd-Rate von 16 eingestellt. Der Rangiersteckverbinder ist hier ohne Einfluß, als Sende- bzw. Empfangsfrequenz wird dem USART eine Frequenz von 19200 Hz angeboten. Somit ist eine Übertragungsrate von 1200 Bd eingestellt.

Durch die Programmierung des USART auf den Teilungsfaktor 64 kann die Aufzeichnungsgeschwindigkeit auf 300 Bd reduziert werden.

Die vom PC aufgezeichneten Frequenzen sind 2400 Hz (H-Pegel  $\stackrel{\circ}{=}$  logisch 1) und 1200 Hz (L-Pegel  $\stackrel{\circ}{=}$  logisch 0). Diese Frequenzen sind nicht frei wählbar (im Gegensatz zur Baudrate der seriellen Schnittstelle).

# Cassettenrecorder - Schnittstelle

Abb. 5.10

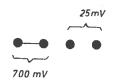

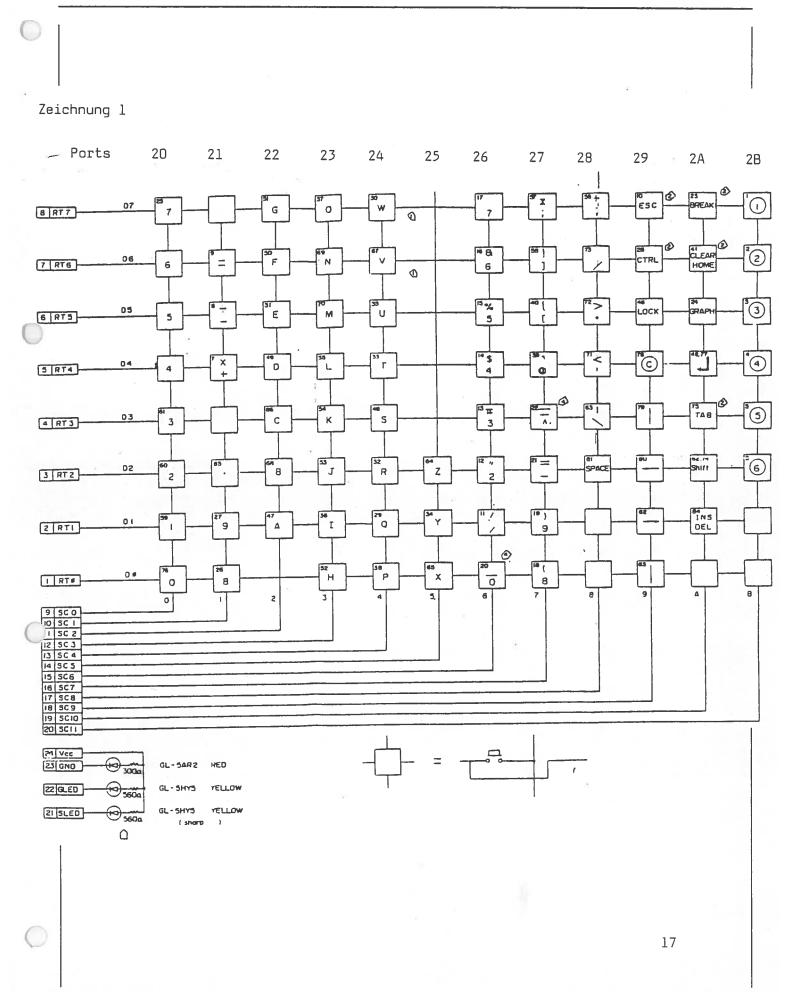

Die FSK-Modulation (siehe Abb. 5.10) übernimmt ein D-Flip flop (SN 74 LS 74, Texas Instruments) in Zusammenarbeit mit zwei NAND-Gattern und ausgangsseitigem Widerstands-Kondensator-(RC) Netzwerk zur Pulsverrundung und Pegelanpassung. Der Ausgangspegel beträgt je nach Einstellung der Steckbrücke (Abb. 2.3) ca. 700 mV oder 25 mV (siehe Handbuch des PC).

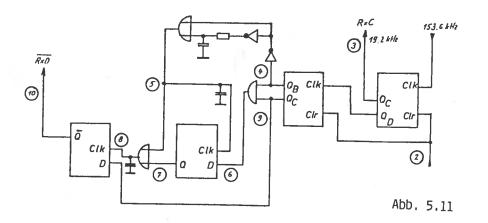

Der Schaltungsaufwand für das Lesen der auf einer Cassette gespeicherten Information ist größer (Abb. 5.10, 5.11). Das auf einer Cassette gespeicherte frequenzcodierte Signal wird einer Begrenzerstufe (bestehend aus Dioden und Widerständen) zugeführt. Das so auf maximal 1,4 Vss begrenzte Signal wird von einem Komparator-IC (LM 311) den Logikpegeln angepaßt. Mit dem nachgeschalteten Differenzierer werden aus den fallenden Flanken des FSK-Signals positive Nadeln erzeugt. Diese werden zur weiteren Verarbeitung dem Demodulator (Abb. 5.12) zugeführt.

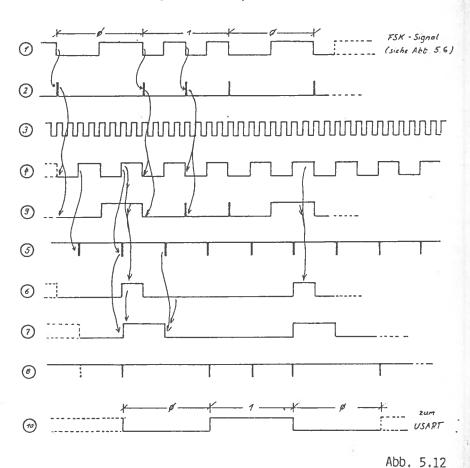

Aus dem nachfolgenden Zeitablaufdiagramm ist die Wirkung der Schaltung, die das empfangene Signal dekodiert, zu ersehen. Die Messpunkte sind in Abbildung 5.10 und 5.11 zu finden.

FSK-Demodulator, CC-Schnittstelle

Die Initialisierung des Cassettenschreib/-lesebetriebes erfolgt <u>nicht</u> von der Initialisierungsroutine des PC. Die Umschaltung des seriellen I/O Betriebes auf Cassettenbetrieb muß entweder vom Basic-Betriebssystem oder vom Benutzer selbst erfolgen.

Das Basic nutzt folgende Routine:

| Befehls Adresse | OP-Code | Mnemonik    |

|-----------------|---------|-------------|

| EB4A            | 3E FE   | LD A,OFEH   |

| EB4C            | D3 41   | OUT 41H,A   |

| EB4E            | 3E 37   | LD A,37H    |

| EB50            | D3 41   | OUT 41H,A   |

| EB52            | 3A E468 | LD A,(SFFO) |

| EB55            | CB 97   | RES 2,A     |

| EB57            | C3 EF41 | JMP PTSET   |

|                 |         |             |

Im Unterschied zur Initialisierung des seriellen Bausteins zum V.24 Modus ist hier lediglich die Zeichenlänge verändert. Sie beträgt hier 8 Bit. Alle anderen Eigenschaften des Datentransfers sind identisch. Weiterhin setzt diese Routine das 2-er Bit des SPORT-Bytes zurück. Dann wird, wie in Kapitel 5.3 beschrieben, zur Ausgabe dieses Byte gesprungen. Pin-Belegung der Kassettenrecorder-Schnittstelle

Ein-/Ausgabe-Signale

Pin-Belegung, Abb. 5.13

(von der Lötseite aus gesehen)

| Nr. | Signal | Bedeutung             | Richtung |

|-----|--------|-----------------------|----------|

| 1   | REC    | verbunden mit 4       |          |

| 2   | GND    | Signal Ground (Masse) | Ausgang  |

| 3   | MON    | verbunden mit 5       |          |

| 4   | REC    | Schreibsignal         | Ausgang  |

|     |        | TTL-Pegel             |          |

| 5   | MON    | Lesesignal            | Eingang  |

|     |        | TTL-Pegel             |          |

| 6   | REMI   | Fernsteuerung         | Ausgang  |

| 7   | REM2   | Fernsteuerung         | Ausgang  |

| 8   | GND    | Signal Ground         |          |

|     |        |                       |          |

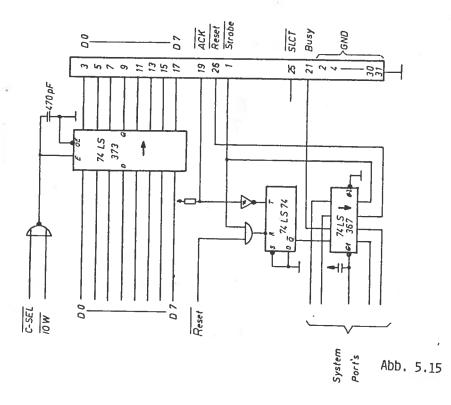

# 5.5 Parallelschnittstelle

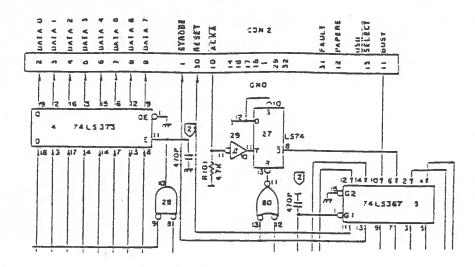

Der alphatronic-PC verfügt über eine 8 Bit-breite Parallelschnittstelle zur Ausgabe von Daten.

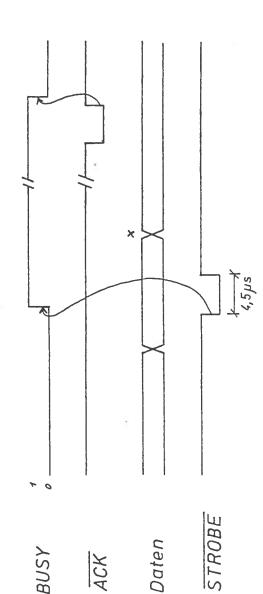

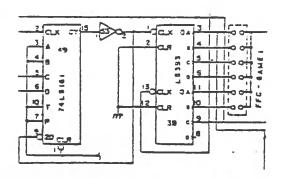

Der Datentransfer erfolgt in einem "Handshake"-Verfahren. Die Pegel und Schaltzeiten sind Centronics-kompatibel. Hierbei wird der Datensenke (-Empfänger, z.B. ein Drucker) von der Datenquelle (in diesem Fall der PC) durch einen Puls auf der "Strobe"-Leitung mitgeteilt, daß ein neues 8 Bit-Wort am parallelen Ausgang bereit steht. Sobald die Senke das Wort übernommen hat, teilt sie dies über die "Acknowledge"-Leitung der Quelle mit. Kann die Senke keine Zeichen übernehmen, wird das der Quelle über die "Busy"-Leitung mitgeteilt. Ferner kann das periphere Gerät über die Resetleitung zurückgesetzt werden.

\*Der PC ändert die Daten erst nach ACK=0

# Centronics-Schnittstelle

Die Ausgabe der 8 Bit-Datenworte erfolgt über das IC 74 LS 374. Ein im A-Register der MPU stehendes Datenbyte wird durch den Befehl OUT 30H an das Register ausgegeben. Das Senden bzw. Empfangen der Steuersignale STROBE, ACK, BUSY, und RESET erfolgt über einen Baustein des Typs 74 LS 367. Das Einlesen der Steuersignale ACK und BUSY erfolgt über den Befehl IN 30H. Der Inhalt des Steuerwortes sieht wie folgt aus:

Bit 2 Centronics ACK

1 = aktiv, Datenwort wurde übernommen

0 = inaktiv

Bit 3 Centronics BUSY

1 = Peripheriegerät ist beschäftigt und kann zur

Zeit keine Daten übernehmen

0 = Datenübernahme möglich

Die Ausgabe des Strobe- und Resetpulses erfolgt über OUT 20H. Als Ausgaberegister dienen 2 Bausteine des Typs 74 LS 175 (je 4 D-Flip Flops).

Bit 1 Centronics RESET

1 = Rücksetzen

0 = nicht Rücksetzen

Bit 2 Centronics STROBE

1 = Strobe aktiv

O = Strobe inaktiv

Es ist zu empfehlen, diese Bits nur mit den Bitmanipulationsbefehlen der Z 80 MPU (BIT, RES, SET) abzufragen bzw. zu ändern.

Der Strobepuls kann zum Beispiel durch folgende Sequenz erzeugt werden:

3A E469 LD A,(SFF1)

CB D7 SET 2,A

D3 20 OUT 20H,A

00 NOP

; die Anzahl der NOP ; (no operation) Befehle ; richtet sich nach der ; gewünschten Pulsdauer, ; für einen 4,5 us Puls ist ; kein NOP-Befehl erforder-; lich. Pro NOP-Befehl wird

; die Pulsdauer um 1 us ver-

; längert (Z 80 A,4 MHz)

00 NOP

CB 97 RES 2,A

D3 20 OUT 20H, A

Von den 6 verbleibenden Bits des Statusport 2, Adresse 20H werden 5 für andere Aufgaben genutzt:

Bit 0 CRISI, CRI-Controller RESET 1 = CRT-Controller zurücksetzen

0 = nicht zurücksetzen

Bit 3 MONINH, Umschaltung zwischen Monitor-ROM und Video-RAM

1 = Video-RAM angewählt

0 = Monitor-ROM angewählt

Bit 4 GLED

1 = Graphik-LED der Tastatur einschalten

0 = ausschalten

Bit 5 SLED

1 = Shift-Locked-LED ein

0 = aus

Monitor ROM/Video RAM Adressbereich

l = Freigabe der 4 kByte Speicher mit den höheren Adressen

O = Freigabe der niederen Adressen

Eine Kopie des am Ausgabeport 20H gegebenen Datenwortes befindet sich in dem SFF1-Byte, Adresse E469H. Während der Initialisierung wird 00 in SFFl geladen.

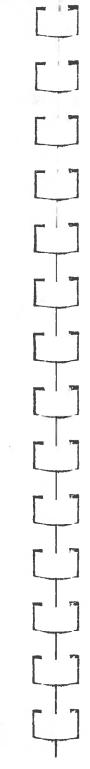

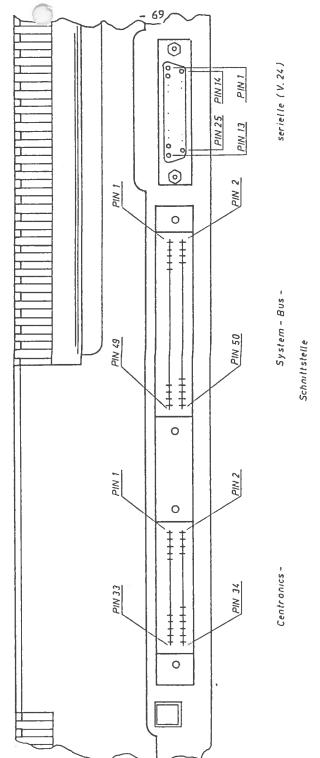

Die Zählweise der Steckerpins des Verbinders ist aus Abbildung 5.16 ersichtlich.

Die Signalbelegung ist aus der nachstehenden Tabelle zu entnehmen.

# Ein-/Ausgabe-Signale

| Nr.      | Signal           | Bedeutung                                                                                                                                           | Richtung                      |

|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 1        | STB              | Freigabesignal für das<br>Senden der Daten zum<br>Drucker; negative Logik,                                                                          | Ausgang<br>Ausgang<br>Ausgang |

|          | DATA .           | TTL-Pegel                                                                                                                                           | Ausgang                       |

| 3<br>5   | DATA-1           |                                                                                                                                                     | Ausgang                       |

| 7        | DATA-2           | Die Signale Data-1 bis                                                                                                                              | Ausgang                       |

| 9        | DATA-3           | DATA-8 enthalten Informa-                                                                                                                           | Ausgang                       |

| -11      | DATA-4           | tionen über das jeweils                                                                                                                             | Ausgang                       |

| 13       | DATA-5           | 1. bis 8. Bit der parallel                                                                                                                          | Ausgang                       |

| 15       | DATA-6<br>DATA-7 | zu übertragenden Daten.:                                                                                                                            | Ausgang                       |

| 17       | DATA-8           | positive Logik, TTL-Pegel                                                                                                                           | Ausgang                       |

| 19       | ACK              | Dan Computer askille                                                                                                                                | _ 12                          |

| 21       |                  | Der Computer erhält das<br>Quittungssignal vom Drucker:<br>dieser hat Daten empfangen<br>und ist erneut empfangsbereit<br>Negative Logik, TTL-Pegel | Eingang                       |

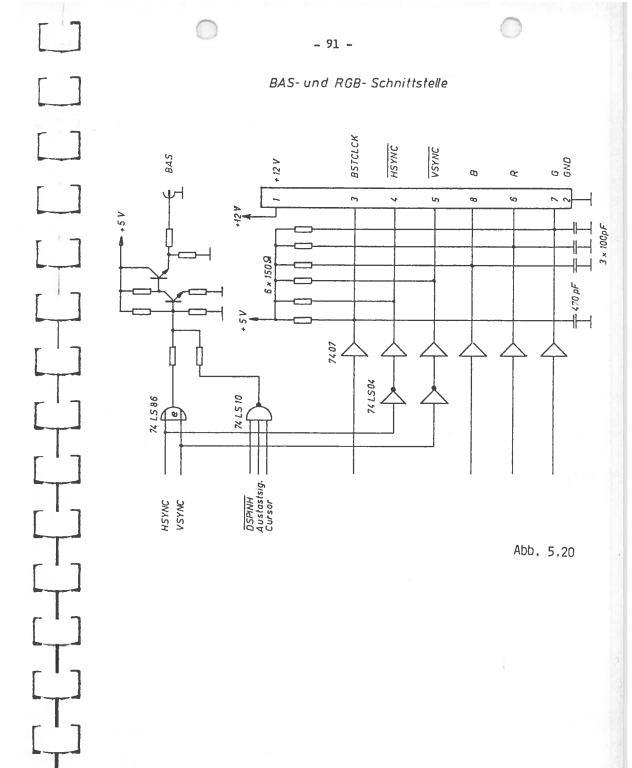

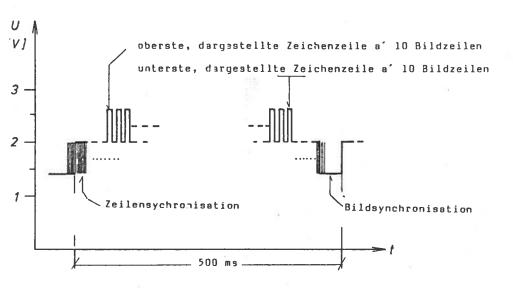

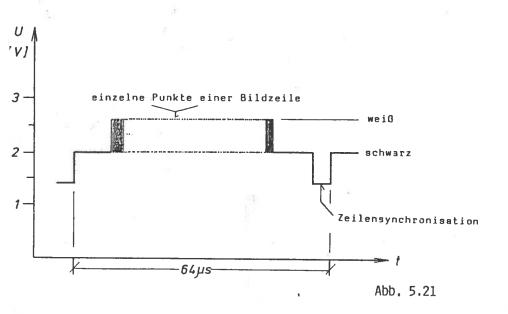

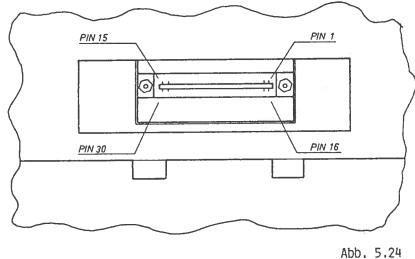

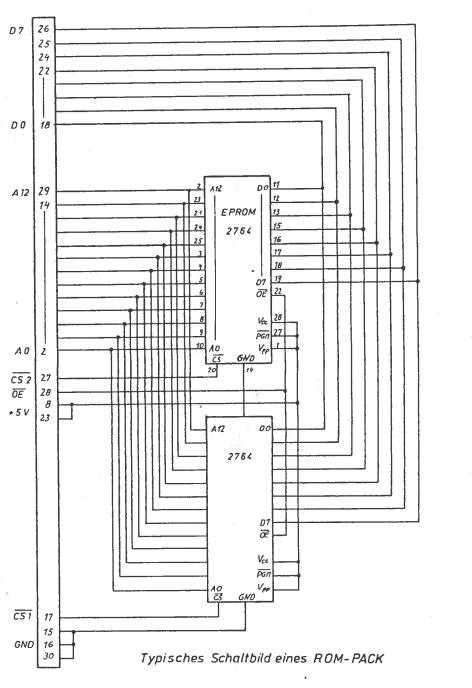

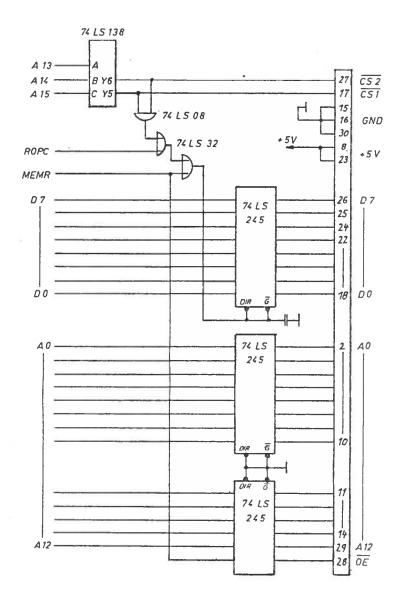

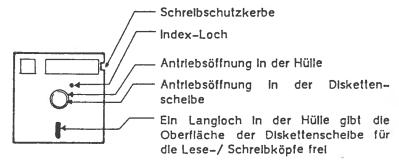

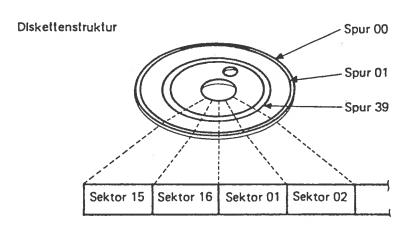

|          | BSY              | Signal an PC vom Drucker<br>Er ist empfangsbereit, sein<br>Puffer ist leer.<br>Negative Logik, TT1-Level                                            | Eingang                       |