8

• ,-

$\mathbf{\hat{\mathbf{x}}}$

|     |                                                              | •            |

|-----|--------------------------------------------------------------|--------------|

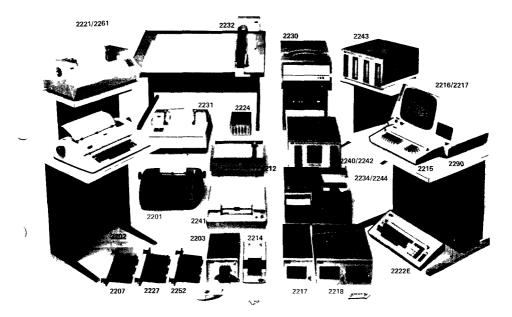

| 1.  | DESCRIPTION                                                  | 1-1          |

|     | 1.1 GENERAL                                                  | 1-1          |

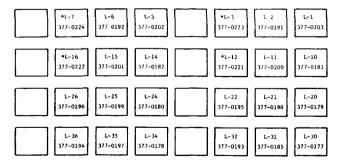

|     | 1.2 MODEL INFORMATION                                        | 1-18         |

|     | 1.3 SPECIFICATIONS                                           | 1-19         |

|     | 1.3.1 2200 System; General Specifications                    | 1-19         |

|     | 1.3.2 2200 CPU; Models A, B, C, S, T                         | 1-19         |

|     | 1.3.3 Memory Sizes                                           | 1-22<br>1-22 |

|     | 1.3.4 Peripheral Capabilities                                | 1-22         |

|     | 1.3.5 Dynamic Range                                          | 1-22         |

|     | 1.3.6 Subroutine Stacking                                    | 1-22         |

|     | 1.3.7 Physical Parameters 5.<br>1.4 PERIPHERAL CABLE LENGTHS |              |

|     | 1.4 PERIPHERAL CABLE LENGTHS                                 |              |

|     | SECTION 2 Trave                                              |              |

|     |                                                              |              |

| 2.  |                                                              |              |

| 2.  | 2.1 INSTALLATION GUIDE FOR WANG SYSTEMS                      | , 2-1<br>2-1 |

|     | 2.1.1 Selecting A Location                                   | 2-1          |

|     | 2.1.2 Controlling The Environment                            | 2-1          |

|     | 2.1.3 Electrical Environment                                 | 2-3          |

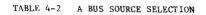

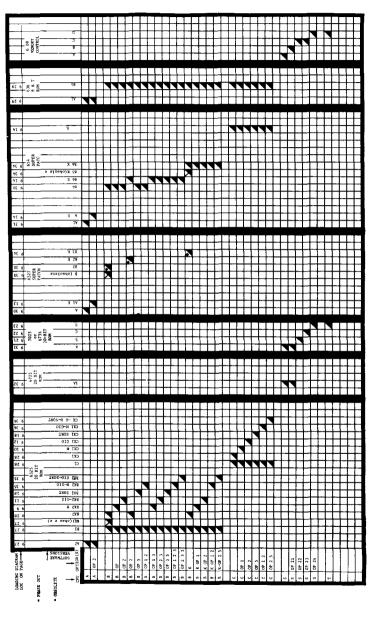

|     | 2.2 DEVICE ADDRESS ASSIGNMENTS                               | 2-4          |

|     | 2.2.1 2200 Peripheral Default Addresses                      | 2-6          |

|     | 2.2.2 Address Setting On 2200 I/O Controller Card            | s 2-7        |

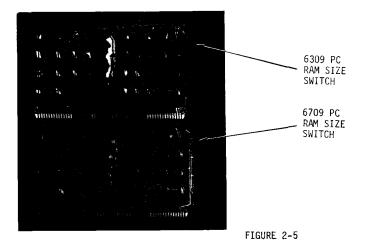

|     | 2.3 RAM SIZE SELECTIONS                                      | 2-11         |

|     | 2,4 INCOMING INSPECTION                                      | 2-12         |

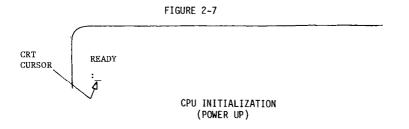

|     | 2.5 INSTALLATION PROCEDURE                                   | 2-13         |

|     | SECTION 3                                                    |              |

|     | 000017100                                                    |              |

| 3.  |                                                              | 3-1<br>3-1   |

|     | 3.1 GENERAL<br>3.2 PROGRAMMING OF OUTPUT DEVICES             | 3-1          |

|     | 3.2.1 The Select Statement                                   | 3-1          |

|     | 3.2.2 Device Type Codes                                      | 3-1          |

|     | 3.2.3 Print                                                  | 3-5          |

|     | 3.2.4 List                                                   | 3-5          |

|     | 3.2.5 Console Output                                         | 3-6          |

|     | 3.2.6 Line Length                                            | · 3-6        |

|     | 3.2.7 Special Techniques                                     | 3-8          |

|     | 3.2.8 Summary Of Console And Non-console Device (            |              |

|     | From CPU                                                     |              |

|     | SECTION 4                                                    | •            |

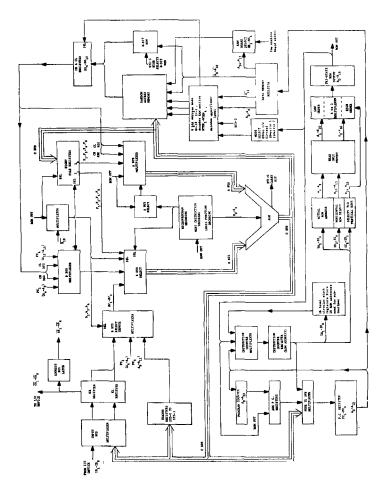

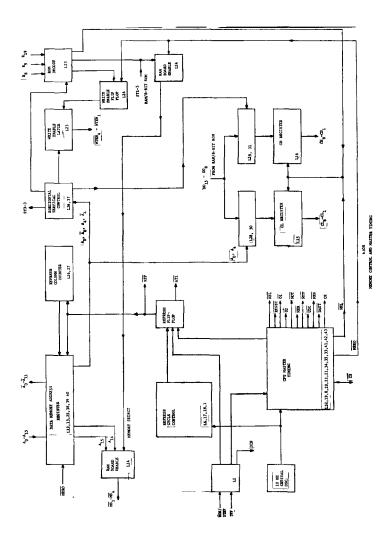

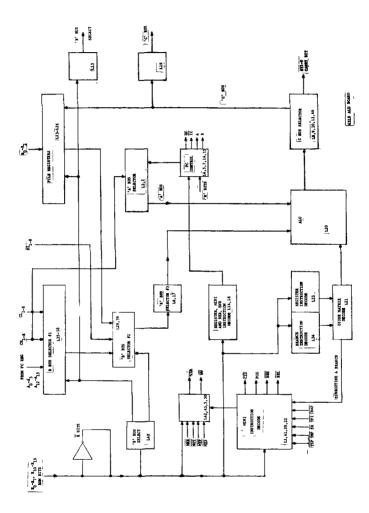

| 4.  | THEORY OF OPERATION                                          | 4-1          |

| -7. | 4.1 CPU GENERAL DESCRIPTION                                  | 4-1          |

|     | 4.1.1 Introduction                                           | 4-1          |

|     | 4.1.2 Hardware Versus Software                               | 4-1          |

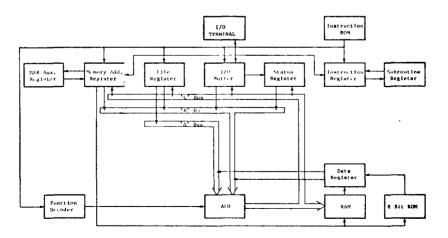

|     | 4.1.3 General Hardware Description                           | 4-4          |

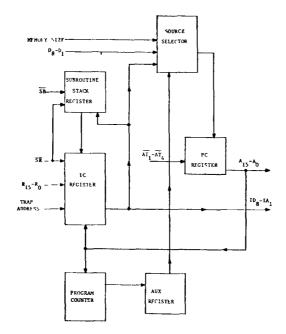

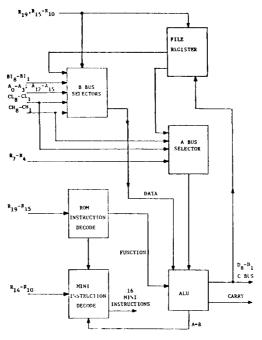

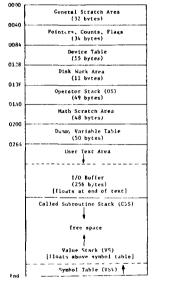

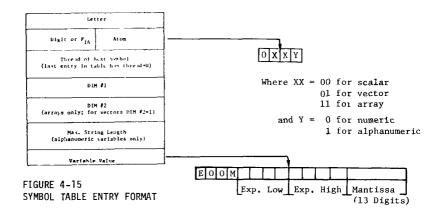

|     | 4.1.3.1 Register Structure                                   | 4-4          |

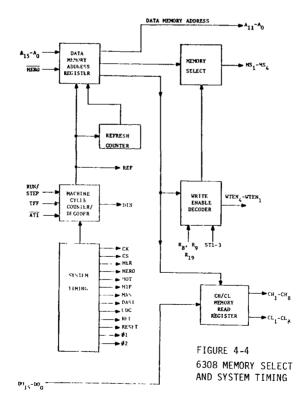

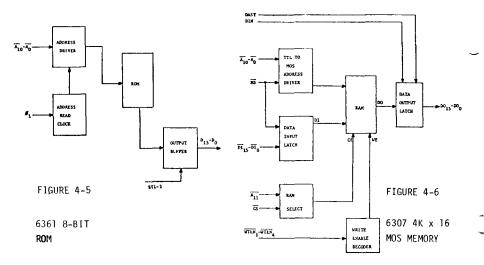

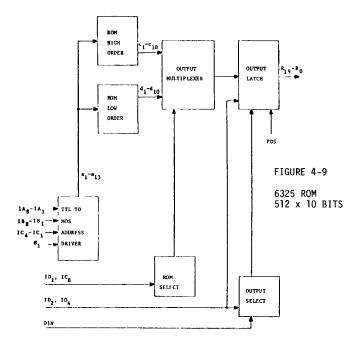

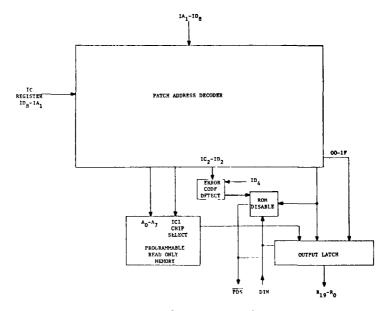

|     | 4.1.3.2 Memory Structure                                     | 4-8          |

|     | 4.1.3.3 Supporting Hardware                                  | 4-11         |

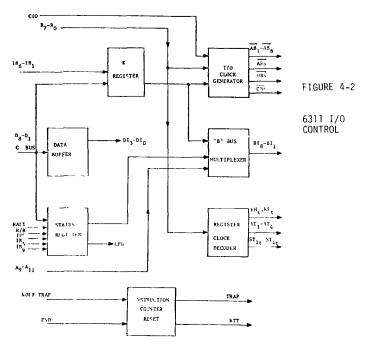

|     | 4.1.3.4 Input/Output Structure                               | 4-15         |

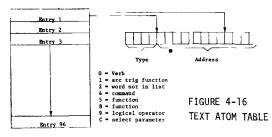

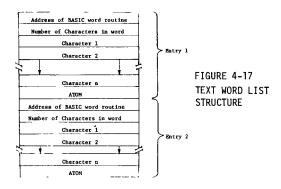

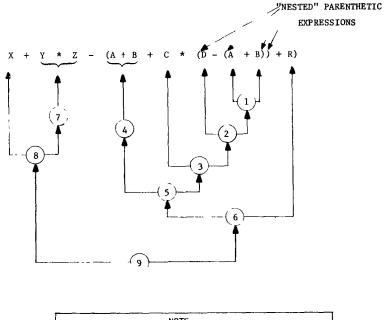

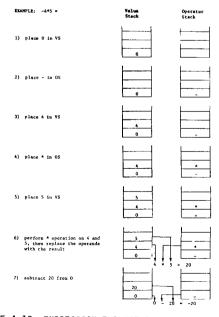

| <ul> <li>4.2 GENERAL INSTRUCTION SET DESCRIPTION</li> <li>4.3 CPU FIRMWARE DESCRIPTION</li> <li>4.3.1 CPU Processing</li> <li>4.3.1.1 Text Entry Phase</li> <li>4.3.1.2 Variable and Line Numbe</li> <li>4.3.1.3 Text Atomizing</li> <li>4.3.1.4 Execution Phase</li> <li>4.3.1.5 Recursion</li> <li>4.3.1.6 Expression Evaluation</li> </ul> | er Resolution Phase | 4-16<br>4-22<br>4-23<br>4-23<br>4-23<br>4-25<br>4-27<br>4-27<br>4-27 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------|--|

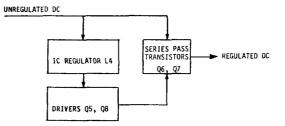

| <ul> <li>4.3.1.7 Looping (FOR/NEXT)</li> <li>4.3.1.8 Subroutines (GOSUB/RETL</li> <li>4.3.1.9 Device Selection</li> <li>4.3.1.10 Output Device Switching</li> <li>4.4 DETAILED THEORY OF CPU OPERATION (CENTR</li> <li>POWER SUPPLY</li> <li>4.4.1 CPU Hardware</li> <li>4.4.2 CPU Power Supply</li> <li>4.4.3 2200 Mnemonics</li> </ul>      | 3                   | 4-31<br>4-32<br>4-32<br>4-34<br>4-35<br>4-35<br>4-88<br>4-90         |  |

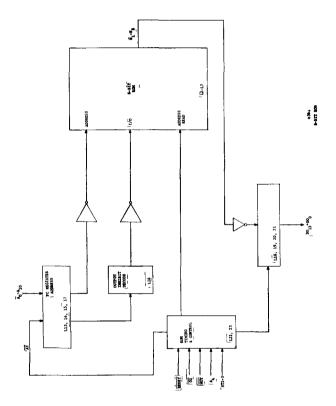

|            |                       | ER SUPPLY HARDWARE OPERATION              | 5-1  |

|------------|-----------------------|-------------------------------------------|------|

|            | AL AND POW<br>DISPLAY | ER SUPPLIT HARDWARE UPERALIUN             | 5-1  |

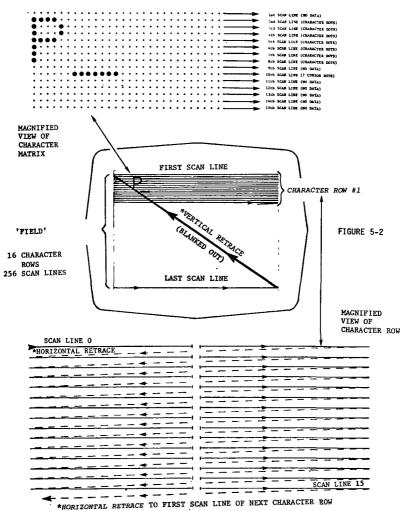

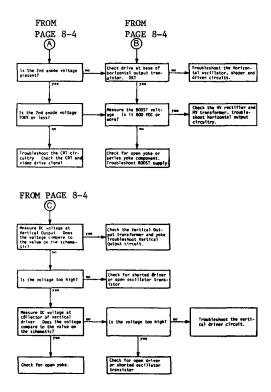

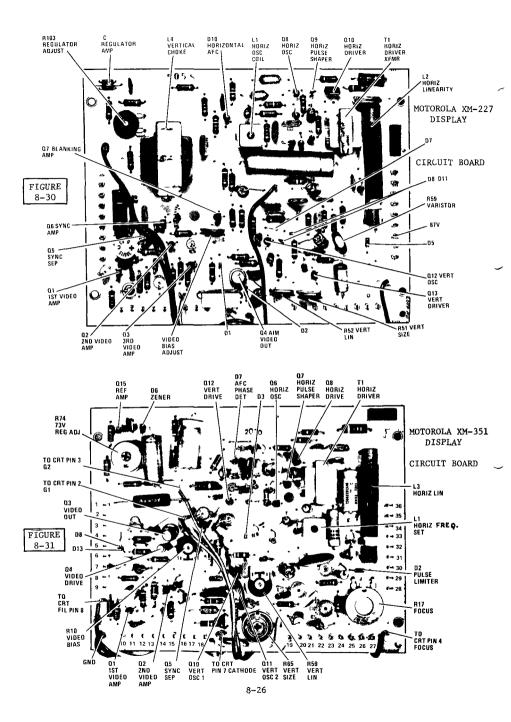

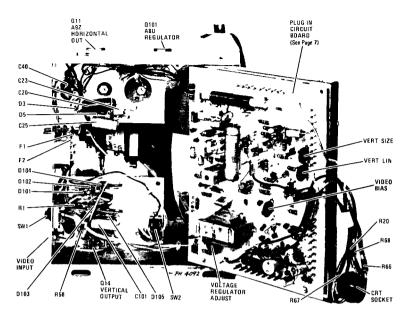

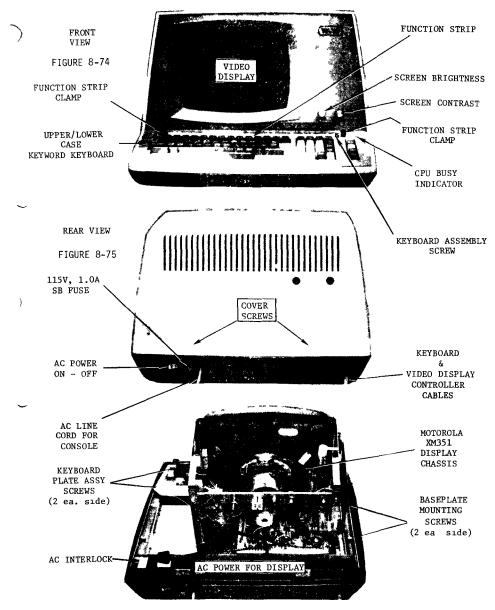

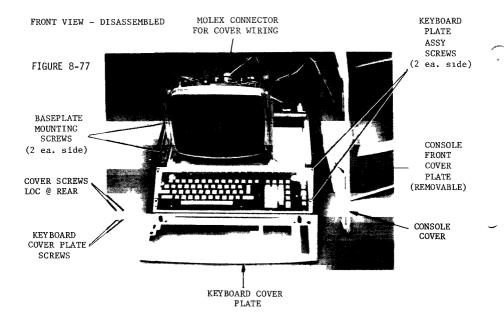

| •••        |                       | play Principles                           | 5-1  |

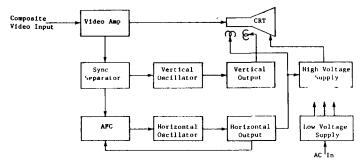

|            |                       | Operation `                               | 5-3  |

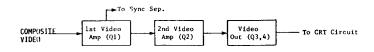

| J.1.2      |                       | Video Amplifier                           | 5-4  |

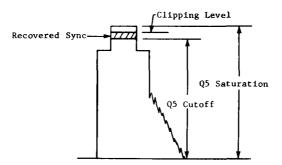

|            |                       | Sync Separator                            | 5-6  |

|            |                       | Vertical Oscillator                       | 5-7  |

|            |                       | Vertical Driver and Output                | 5-8  |

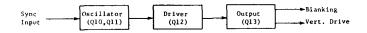

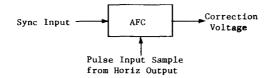

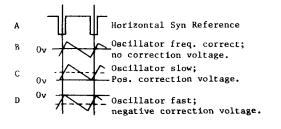

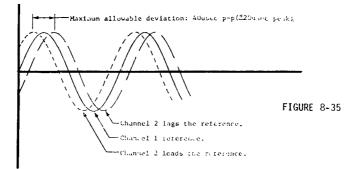

|            |                       | Horizontal AFC Circuit                    | 5-10 |

|            |                       | Horizontal Oscillator                     | 5-12 |

|            |                       | Horizontal Pulse Shaper                   | 5-12 |

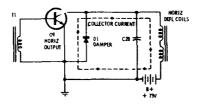

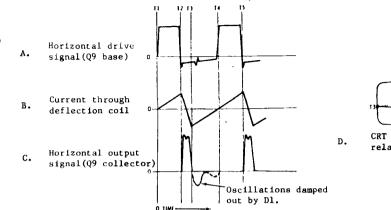

|            |                       | Horizontal Driver                         | 5-13 |

|            |                       | Horizontal Output                         | 5-13 |

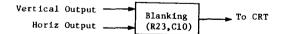

|            |                       | Retrace Blanking                          | 5-17 |

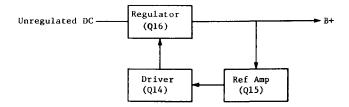

|            |                       | Power Supply (73V Version)                | 5-18 |

|            |                       | Power Supply (12V Version)                | 5-19 |

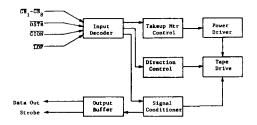

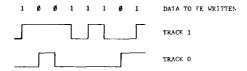

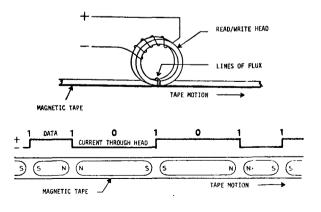

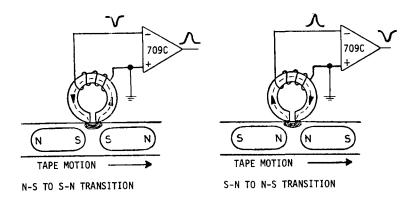

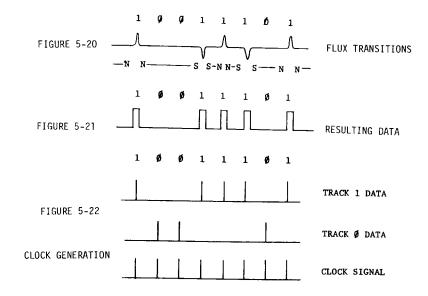

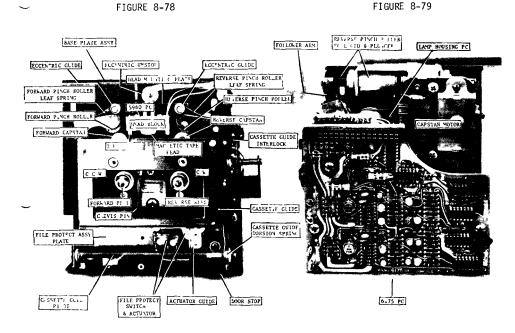

| 5.2 THE TA |                       |                                           | 5-19 |

| - 5.2.1    | Theory Of             | Operation                                 | 5-20 |

|            | •                     | •                                         | 5-20 |

|            |                       | Signal Conditioner                        | 5-20 |

|            |                       |                                           | 5-20 |

|            | 5.2.1.4               | Direction Control                         | 5-20 |

|            | 5.2.1.5               | Output Buffer                             | 5-20 |

| 5.2.2      |                       | Theory Of Operation                       | 5-20 |

|            | 5.2.2.1               | Input Decoder (L558)                      | 5-21 |

|            |                       | Tape Forward Operation (LOAD, SAVE, SKIP) |      |

|            | 5.2.2.3               | Tape Reverse Operation (BACKSPACE)        | 5-21 |

|            | 5.2.2.4               | Rewind                                    | 5-22 |

|            |                       | Power Driver (L559)                       | 5-22 |

|            |                       | Speed Control (L559)                      | 5-22 |

|            | 5.2.2.7               | • • • • • • • • • • • • • • • • • • •     | 5-23 |

|            |                       | Buffer (L558)                             |      |

|            |                       |                                           |      |

x

Z

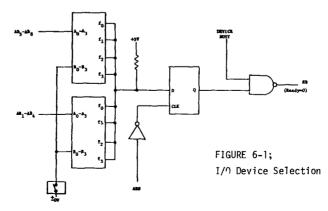

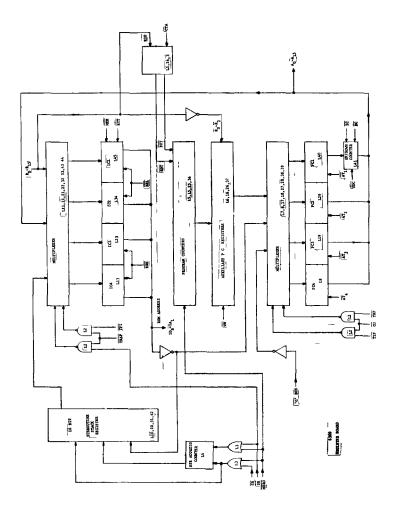

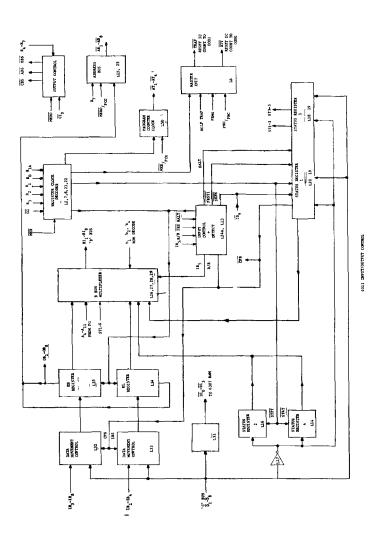

|            | 6. |     |        |            | ROLLER CIRCUIT BOARDS HARDWARE OPERATION | 6-1<br>6-1   |

|------------|----|-----|--------|------------|------------------------------------------|--------------|

| ***        |    | 0.1 |        | Introduct  |                                          | 6-1          |

|            |    |     |        |            | Comparator                               | 6-1          |

|            |    |     |        | Select La  |                                          | 6-2          |

|            |    |     | 614    | Roady/Rus  | By Decoder                               | 6-2          |

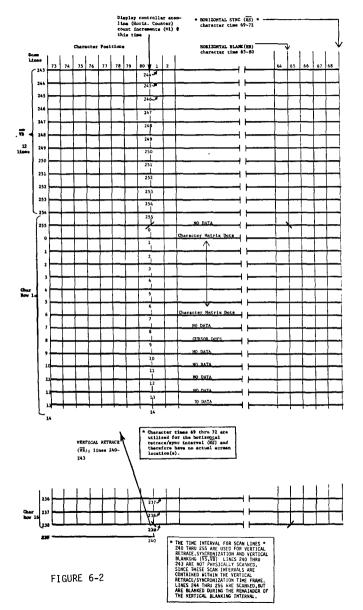

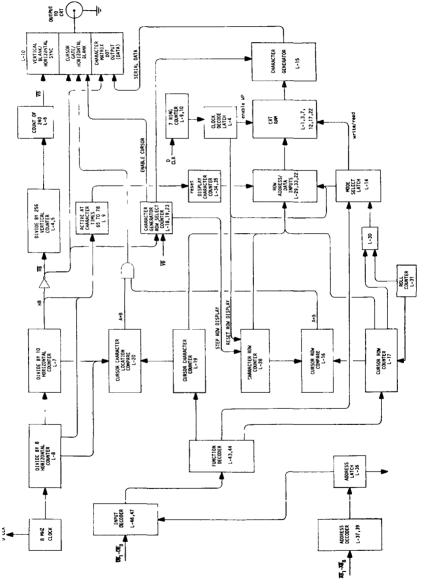

|            |    | 6 2 |        | DISPLAY C  |                                          | 6-2          |

|            |    | 0.2 |        |            | Theory of Operation                      | 6-2          |

|            |    |     | 0.2.12 | 6.2.1.1    |                                          | 6-2          |

| *          |    |     |        | 6.2.1.2    | Device Selection and Data Input          | 6-2          |

|            |    |     |        | 6.2.1.3    | Clock Decoder                            | 6-2          |

|            |    |     |        | 6.2.1.4    | Horizontal Counter                       | 6-3          |

|            |    |     |        | 6.2.1.5    | Vertical Counter                         | 6-3          |

|            |    |     |        |            | Cursor Character and Row Counters        | 6-3          |

|            |    |     |        |            | Cursor Character and Row Compare         | 6-3          |

|            |    |     |        | 6.2.1.8    | Memory Address Selection                 | 6-3          |

|            |    |     |        |            | Character Generator Row Select Counter   | 6-5          |

|            |    |     |        |            | Character Generator and Conversion       | 6-5          |

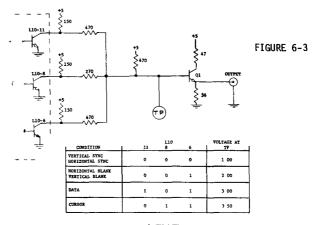

|            |    |     |        |            | Output Gates                             | 6-5          |

|            |    |     |        |            | Roll Counter and Compare                 | 6-6          |

| $\sim$     |    |     |        | 6.2.1.13   | Control Function Decoder                 | 6-7          |

|            |    |     |        | 6.2.1.14   | Control Functions                        | 6-7          |

|            |    |     |        | 6.2.1.15   | Read Cycle                               | 6-7          |

|            |    |     |        |            | Write Cycle                              | 68           |

|            |    |     | 6.2.2  |            | Theory Of Operation                      | 68           |

| $\frown$   |    |     |        | 6.2.2.1    | Device Selection                         | 68           |

|            |    |     |        |            | "D" Clock and Clock Decode Logic         | 68           |

| -25        |    |     |        |            | Vertical Counter .                       | 6-9          |

|            |    |     |        |            | Horizontal Counter                       | 6-9          |

|            |    |     |        |            | Control Functions                        | 6-10         |

|            | ĸ  |     |        | 6.2.2.6    |                                          | 6-11         |

|            |    |     |        |            | Character Generation                     | 6-12         |

|            |    |     |        | -          | Cursor Generation                        | 6-13         |

|            |    |     |        |            | Writing a Character Into Memory          | 6-13         |

|            |    |     |        |            | Lower To Upper Case Conversion           | 6-14         |

|            |    |     |        |            | ces In Video Display Controllers         | 6-14         |

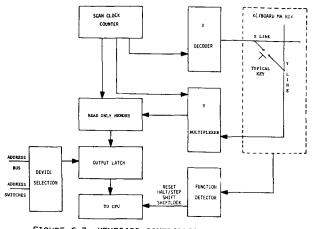

| $\smile$   |    | 6.3 |        | ARD CONTRO |                                          | 6-18         |

|            |    |     | 6.3.1  |            | Theory Of Operation                      | 6-18<br>6-18 |

|            |    |     |        |            | Device Selection                         | 6-18         |

|            |    |     |        |            | Scan Clock                               | 6-19         |

|            |    |     |        |            | Y Multiplexer<br>ROM and Output Latch    | 6-19         |

|            |    |     |        |            | Function Decoder                         | 6-19         |

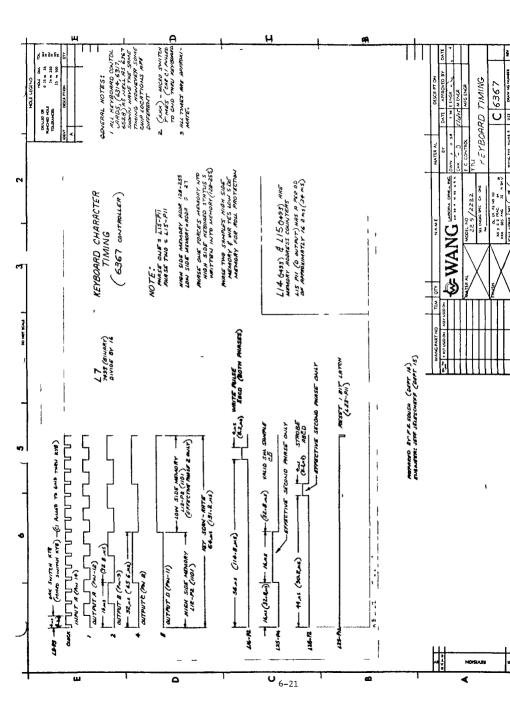

|            |    |     | 637    |            | Theory Of Operation                      | 6-19         |

|            |    |     | 0.3.2  |            | Device Selection                         | 6-19         |

|            |    |     |        |            | Keyboard Input Cycle                     | 6-19         |

|            |    |     |        | 6.3.2.3    | Function Key Detector                    | 6-22         |

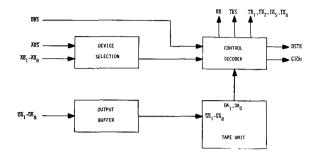

|            |    | 6.4 | TAPE   | DRIVE CONT |                                          | 6-22         |

|            |    | ~   |        |            | Theory Of Operation                      | 6-23         |

|            |    |     |        |            | Device Selection                         | 6-23         |

|            |    |     |        |            | Control Decoder                          | 6-23         |

| $\frown$ - |    |     |        |            | Output Buffer                            | 6-23         |

|            |    |     |        |            | -                                        |              |

|            |    |     |        |            |                                          |              |

**xi**

|                          | 6.4.2 Detailed Theory Of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-23                                                                                                                                                                                                |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | 6.4.2.1 Control Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-24                                                                                                                                                                                                |

|                          | 6.4.2.2 Output Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-24                                                                                                                                                                                                |

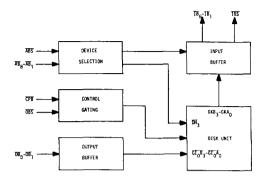

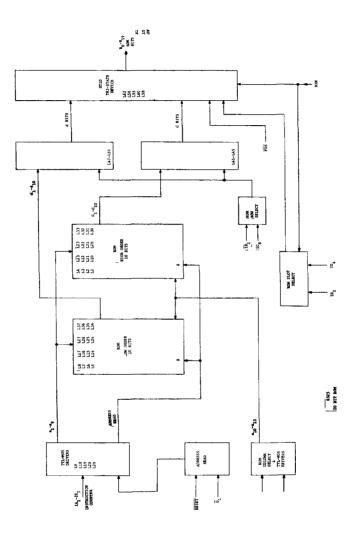

| 6.5                      | DISK CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-24                                                                                                                                                                                                |

|                          | 6.5.1 General Theory Of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-24                                                                                                                                                                                                |

|                          | 6.5.1.1 Device Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-24                                                                                                                                                                                                |

|                          | 6.5.1.2 Input Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-25                                                                                                                                                                                                |

|                          | 6.5.1.3 Output Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-25                                                                                                                                                                                                |

|                          | 6.5.2 Detailed Theory Of Operation 🐂 🙀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 625                                                                                                                                                                                                 |

|                          | 6.5.2.1 Device Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-25                                                                                                                                                                                                |

|                          | 6.5.2.2 Prime Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-26                                                                                                                                                                                                |

|                          | 6.5.2.3 Input Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-26                                                                                                                                                                                                |

|                          | 6.5.2.4 Output Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-26                                                                                                                                                                                                |

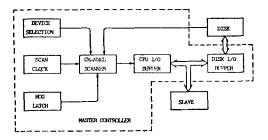

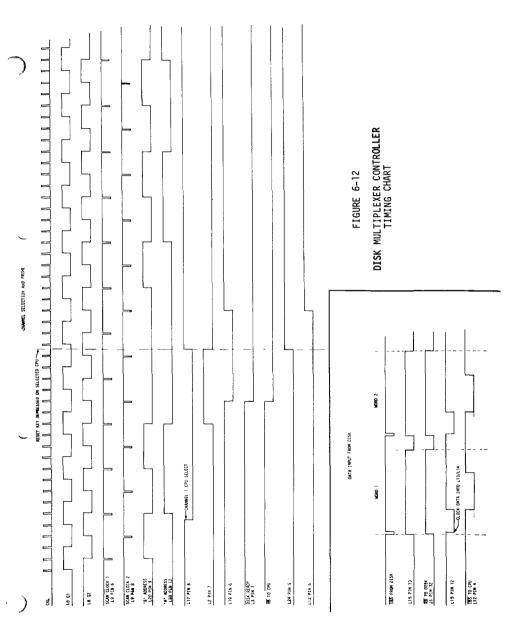

| 6.6                      | DISK MULTIPLEXER CONTROLLER (2230 MXA/B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-26                                                                                                                                                                                                |

|                          | 6.6.1 Theory Of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-26                                                                                                                                                                                                |

|                          | 6.6.1.1 Device Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-27                                                                                                                                                                                                |

|                          | 6.6.1.2 Scan Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-27                                                                                                                                                                                                |

|                          | 6.6.1.3 Channel Scanner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-27                                                                                                                                                                                                |

|                          | 6.6.1.4 CPU I/O Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-27                                                                                                                                                                                                |

|                          | 6.6.1.5 Hog Latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-28                                                                                                                                                                                                |

|                          | 6.6.2 Detailed Theory Of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-28<br>6-28                                                                                                                                                                                        |

|                          | 9 6.6.2.1 Scan Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-28<br>6-28                                                                                                                                                                                        |

|                          | 6.6.2.2 Channel Scanner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-29                                                                                                                                                                                                |

|                          | 6.6.2.3 CPU I/O Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-30                                                                                                                                                                                                |

|                          | 6.6.2.4 Prime Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-30                                                                                                                                                                                                |

|                          | 6.6.2.5 Hog Latch<br>5.6.2.6 Drive #3 Latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-30                                                                                                                                                                                                |

|                          | 5 0.0.2.6 Drive #3 Latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0-30                                                                                                                                                                                                |