# MSV11-P User Guide

Prepared by Education Services of Digital Equipment Corporation 1st Edition, August 1981

#### Copyright <sup>©</sup> 1981 by Digital Equipment Corporation

#### All Rights Reserved

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts 01754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

#### Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

DEC

DECUS

DIGITAL

Digital Logo

PDP

UNIBUS

VAX

DECnet

DECsystem-10

DECSYSTEM-20

DECwriter

DIBOL

EduSystem

IAS

MASSBUS

OMNIBUS OS/8 PDT RSTS RSX VMS

### CONTENTS

#### iv CONTENTS

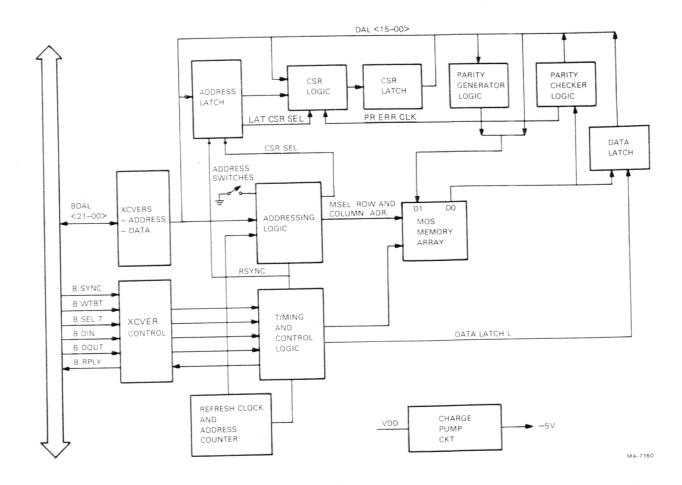

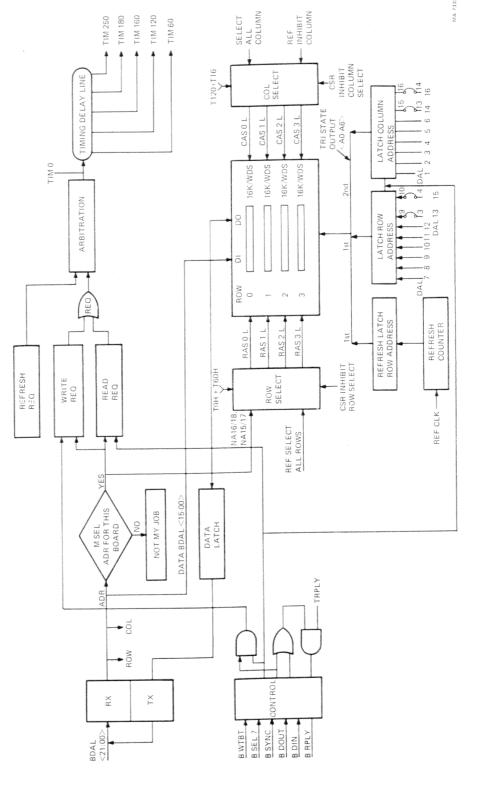

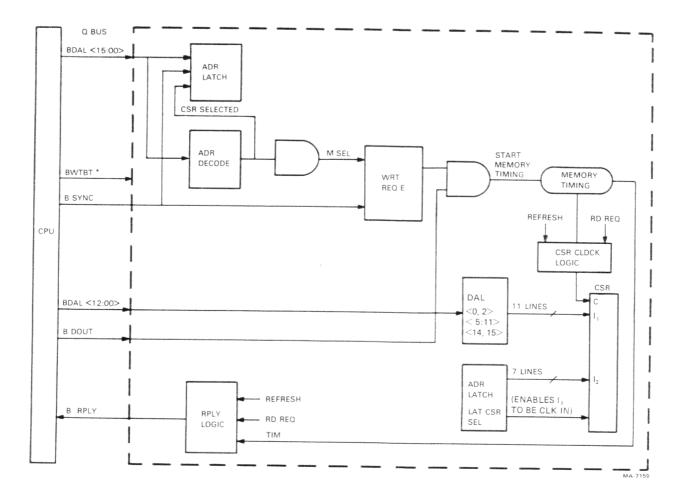

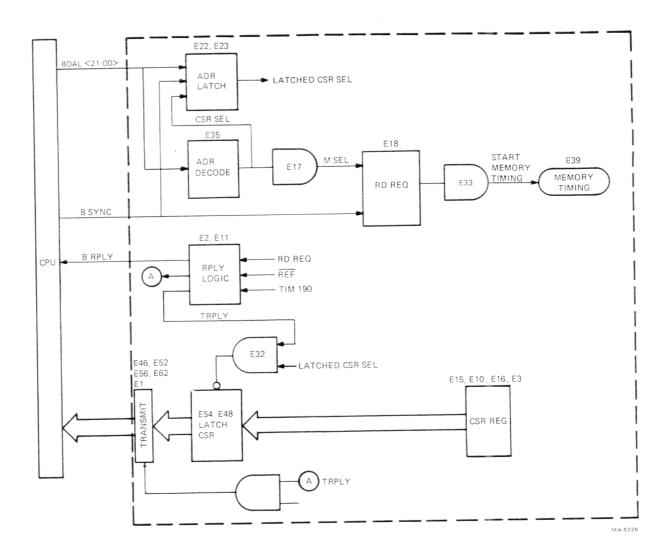

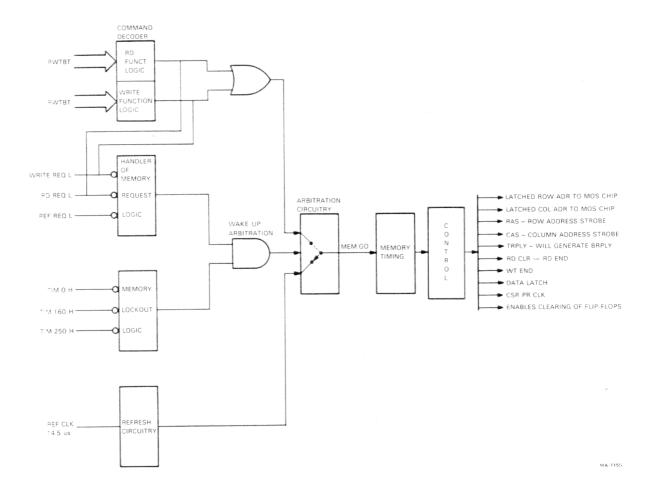

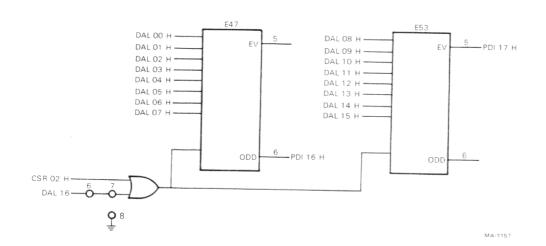

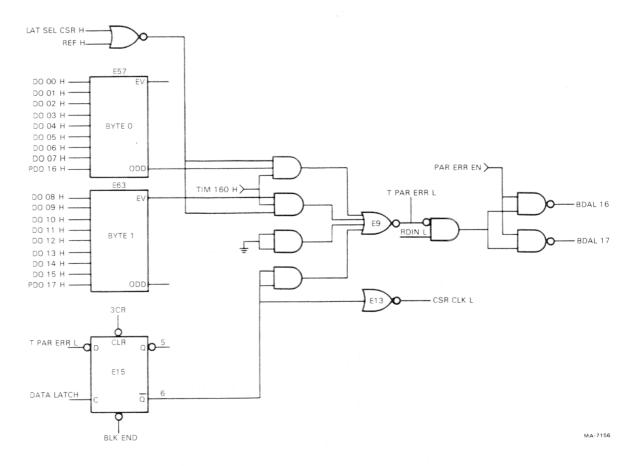

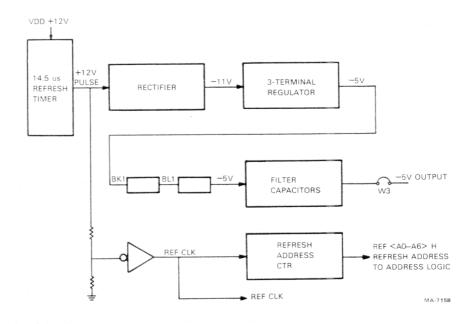

| 3.3<br>3.3.1<br>3.3.2.1<br>3.3.2.2<br>3.3.2.3<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.7.1<br>3.3.7.2<br>3.3.8 | MOS Memory Address Logic CSR Address Logic CSR Write CSR Read Memory Array Timing and Control Logic Parity Logic Parity Generation                  | 30<br>30<br>32<br>32<br>32<br>34<br>34<br>35<br>37<br>37<br>38 |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 3.3.9                                                                                                                     | Charge Pump Circuit                                                                                                                                 |                                                                |

| 3.4                                                                                                                       | Control and Status Register (CSR) Bit Assignment                                                                                                    | 40                                                             |

| CHAP                                                                                                                      | TER 4 MAINTENANCE                                                                                                                                   |                                                                |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3                                                                              | General Preventive Maintenance Visual Inspection Power Voltage Check Diagnostic Testing DIGITAL's Services                                          | 43<br>43<br>43<br>44                                           |

| APPE                                                                                                                      | NDIX A SIGNAL SEQUENCES                                                                                                                             |                                                                |

| FIGUR                                                                                                                     | RES                                                                                                                                                 |                                                                |

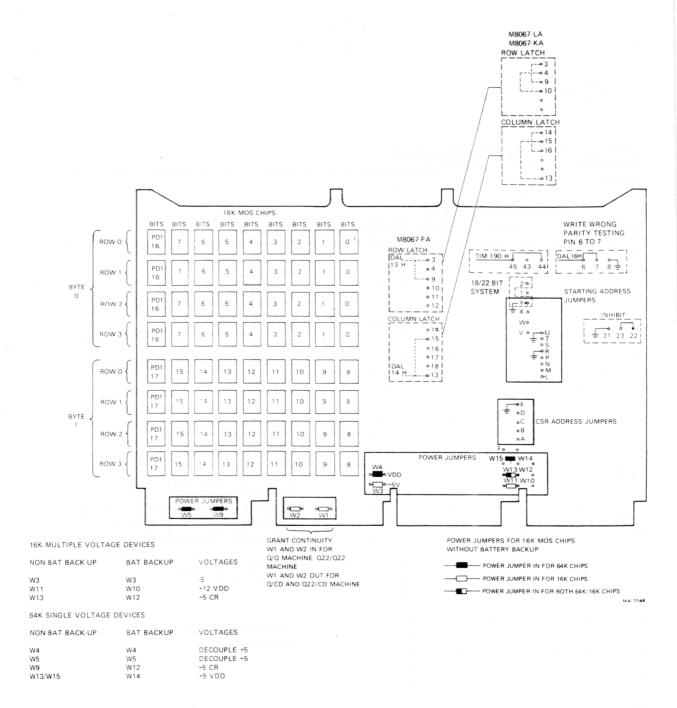

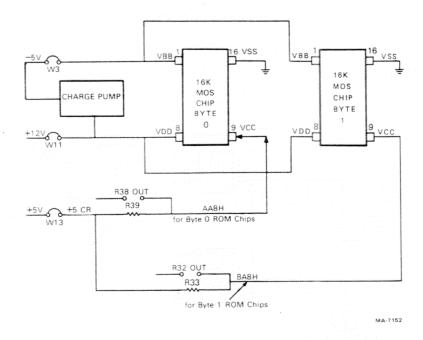

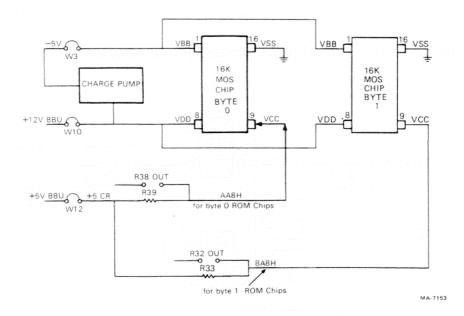

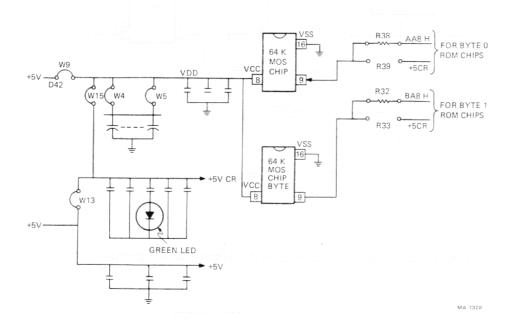

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5                                                                                           | Memory Board Triple Voltage MOS RAM with Battery Backup Triple Voltage MOS RAM without Battery Backup Single Voltage MOS RAM without Battery Backup | 17<br>17                                                       |

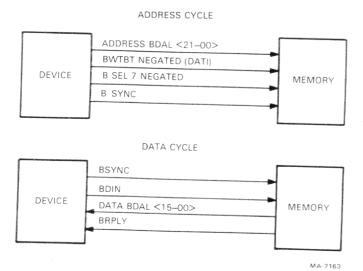

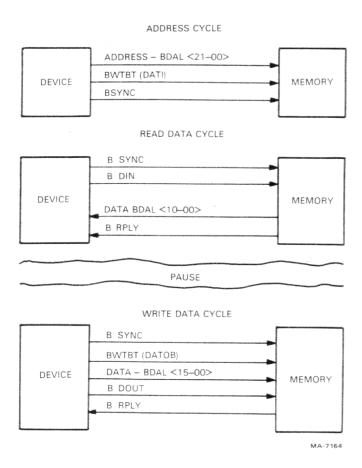

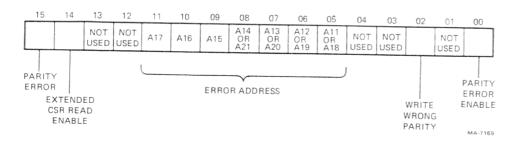

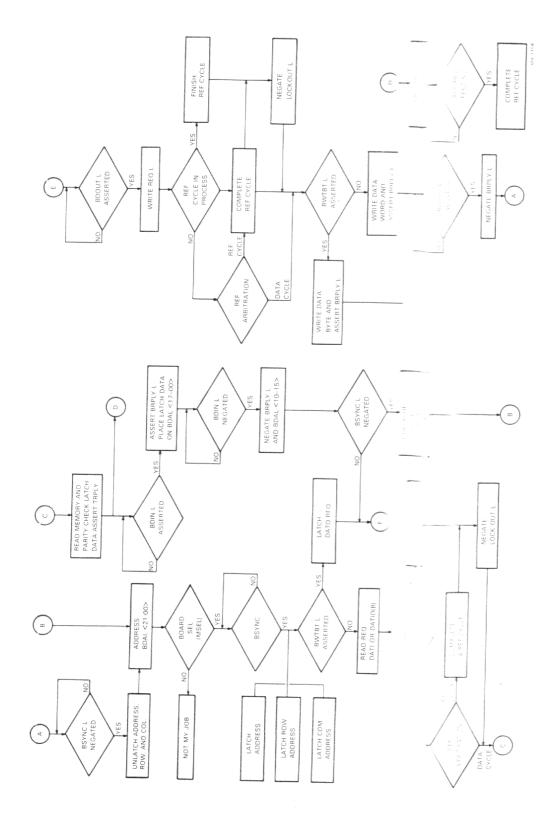

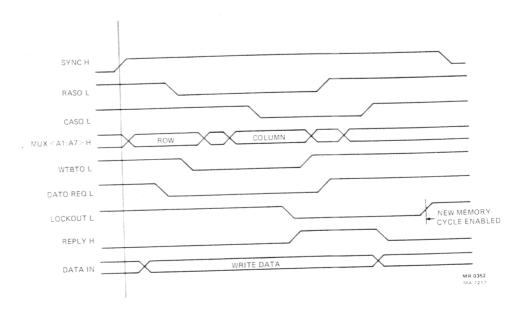

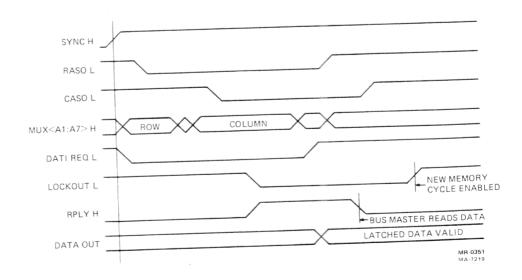

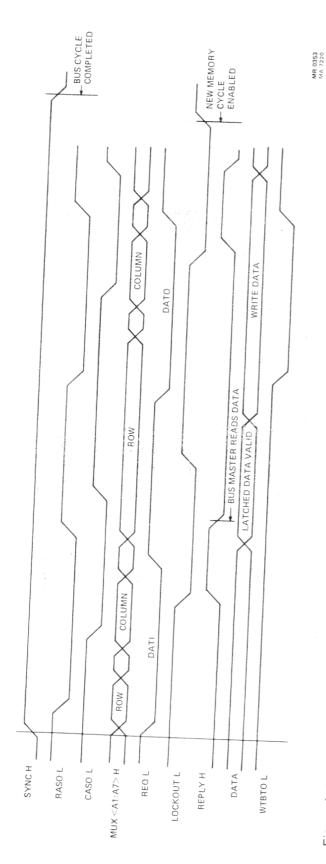

| 3-15<br>3-16<br>A-1<br>A-2<br>A-3<br>A-4                                                                                   | Refresh Logic and Charge Pump Circuit  CSR Bit Allocation  Memory Operation Cycle  DATO(B) Signal Sequence  DATI Signal Sequence  DATIO(B) Signal Sequence                                                                                                                                                                                                                                                                                                        | 40<br>46<br>47<br>47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TABLE                                                                                                                      | ES .                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7 | MSV11-P Versions Access and Cycle Times Multi/Single Voltage MOS RAM MSV11-P Power Backplane Pin Utilization MSV11-P Jumper Check List Starting Address Configurations CSR Address Selection Power Jumpers Bus Grant Continuity General Jumpers Summary of Bus Cycles LSI-11 Bus Signals and Definitions Dialogues to Perform Memory Data Transfers Dialogue DATO(B) Cycle Dialogue DATI Dialogue DATIO(B) Cycle PROM Output for M8067-LA (Starting Address Zero) | 3<br>4<br>5<br>6<br>12<br>13<br>15<br>16<br>19<br>21<br>22<br>24<br>25<br>27<br>28<br>31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| * 1                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                            | 3-16<br>A-1<br>A-2<br>A-3<br>A-4<br>TABLE<br>1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6                                                                                                                                                                                                                                                                                                  | 3-16 CSR Bit Allocation A-1 Memory Operation Cycle A-2 DATO(B) Signal Sequence A-3 DATI Signal Sequence A-4 DATIO(B) Signal Sequence  TABLES  1-1 MSV11-P Versions 1-2 Access and Cycle Times 1-3 Multi/Single Voltage MOS RAM 1-4 MSV11-P Power 1-5 Backplane Pin Utilization 2-1 MSV11-P Jumper Check List 2-2 Starting Address Configurations 2-3 CSR Address Selection 2-4 Power Jumpers 2-5 Bus Grant Continuity 2-6 General Jumpers 3-1 Summary of Bus Cycles 3-2 LSI-11 Bus Signals and Definitions 3-3 Dialogues to Perform Memory Data Transfers 3-4 Dialogue DATO(B) Cycle 3-5 Dialogue DATI 3-6 Dialogue DATIO(B) Cycle 3-7 PROM Output for M8067-LA (Starting Address Zero) |

#### CHAPTER 1 CHARACTERISTICS AND SPECIFICATIONS

#### 1.1 INTRODUCTION

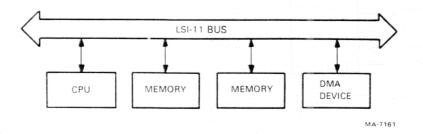

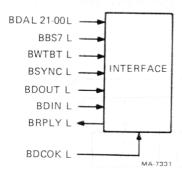

This manual describes the MSV11-P family of memory modules. The MSV11-P memory modules are metal oxide semiconducters (MOS), random access memory (RAM). They are designed to be used with the LSI-11 bus. The MSV11-P provides storage for 18-bit words (16 data bits and 2 parity bits) and also contains parity control circuitry and a control and status register (CSR). There are three versions of the MSV11-P memory modules as shown in Table 1-1.

Table 1-1 MSV11-P Versions

| Option<br>Designation | Module<br>Designation | Storage<br>Capacity  | MOS<br>Chips | Module<br>Population | Number<br>of<br>Rows |

|-----------------------|-----------------------|----------------------|--------------|----------------------|----------------------|

| MSV11-PL              | M8067-LA              | 256K words by 18 bit | 64K          | Full                 | 8                    |

| MSV11-PK              | M8067-KA              | 128K words by 18 bit |              | Half                 | 4                    |

| MSV11-PF              | M8067-FA              | 64K words by 18 bit  |              | Full                 | 8                    |

#### 1.2 GENERAL DESCRIPTION

The MSV11-P memory module consists of a single, quad-height module (M8067) that contains the LSI-11 bus interface, timing and control logic, refresh circuitry, and a MOS storage array. The module also contains circuitry to generate and check parity, and a control and status register.

The memory module's starting address can be set on any 8K boundry within the 2048K LSI-11 address space or 128K LSI-11 address space. The MSV11-P allows the top 4K of the LSI-11 address space to be reserved for the I/O peripheral page. Note that there is no address interleaving with the MSV11-P.

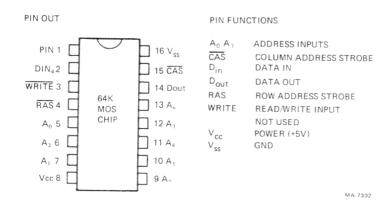

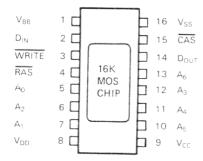

The memory storage elements are 16,384 by 1 bit, MOS dynamic RAM devices or 65,536 by 1 bit MOS dynamic RAM devices. The MOS storage array contains 18 of these devices for every 16K rows of memory or 64k rows of memory. Unlike core memory, the read operation for MOS storage devices is nondestructive; consequently the write-after-read operation associated with core memory is eliminated. The MOS storage devices must be refreshed every 14.5  $\mu$ s so that the data remains valid.

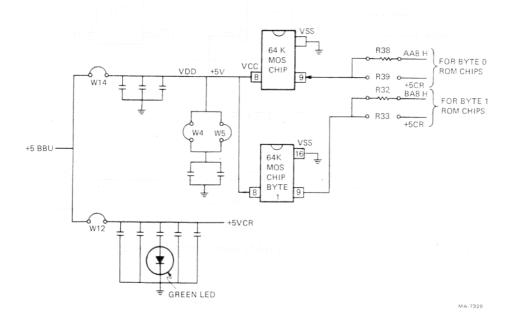

The MSV11-PF memory uses +5 V, +12 V and -5 V. The positive voltages are received from the backplane and the negative voltage is generated from a charge pump circuit on the board. The MSV11-PL and MSV11-PK require +5 V, which is received from the backplane.

There is a green LED on the module that stays on as long as +5 V power is supplied to the logic required for memory refresh, read/write request, arbitration, and row and column addressing.

The control and status register in the MSV11-P contains bits that are used to store the parity error address bits. By setting a bit in the CSR you can force wrong parity. This is a useful diagnostic tool for checking out the parity logic. The CSR has its own address in the top 4K of memory. Bus masters can read or write to the CSR.

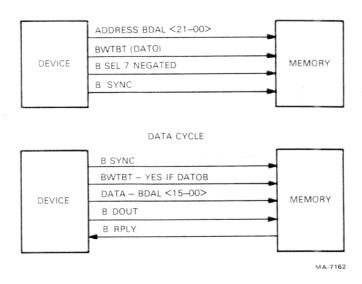

The parity control circuitry in the MSV11-P generates parity bits based on data being written into memory during a DATO or DATOB bus cycle. One parity bit is assigned to each data byte and is stored with the data in the MOS storage array. When data is retrieved from memory during DATI or DATIO bus cycles, the parity of the data is determined. If parity is good, the data is assumed correct. If the parity bits do not correspond, the data is assumed unreliable and memory initiates the following action.

- A red LED on the module lights. This provides a visual indication of a parity error and sets CSR bit 15.

- 2. If bit 0 in the CSR is set, the memory asserts BDAL 16 and 17. This warns the processor that a parity error has occurred.

- 3. Part of the address of the faulty data is recorded in the CSR.

#### 1.3 SPECIFICATIONS

This section of the manual gives functional, electrical, and environmental specifications and backplane pin utilization information.

#### 1.3.1 Functional Specifications

Table 1-2 provides MSV11-P functional specifications.

#### 1.3.2 Electrical Specifications

The electrical specifications state the voltage and power requirements for the MSV11-P.

No adjustment or maintenance is required. Two LEDs are used to indicate board status. A green LED indicates that +5 V CR is present on the board. This is useful on battery backed up systems where the boards could be removed from the backplane with only +5 V shut off. A red LED indicates the detection of a parity error.

Table 1-2 Access and Cycle Times\*

|               | Access Time        | †       |       | Cycle Tim          | Cycle Time‡ |       |

|---------------|--------------------|---------|-------|--------------------|-------------|-------|

| Bus<br>Cycles | Measure<br>Typical | Maximum | Notes | Measure<br>Typical | Maximum     | Notes |

| DATI          | 240                | 260     | 2     | 560                | 590         | 4     |

| DATO(B)       | 90                 | 120     | 2     | 610                | 640         | 5     |

| DATIO(B)      | 660                | 690     | 3     | 1175               | 1210        | 6     |

| REFRESH       |                    |         |       | 640                | 690         | 7     |

Parity - CSR configurations, refer to notes 1, 8, and 9.

NOTE 1: Assuming memory not busy and no arbitration.

NOTE 2: SYNCH to RPLYH with minimum times (25/50 ns) from SYNCH to (DINH/DOUTH). The DATO(B) access and cycle times assume a minimum 50 ns from SYNCH to DOUTH inside memory receivers. For actual LSI-11 bus measurements, a constant (K-50 ns) where K = 200ns should be added to DATO(B) times, i.e., Tacc (Typical) = 90 + (200 - 50) = 240 ns.

NOTE 3: SYNCH to RPLYH [DATO(B)] with minimum time (25 ns) from SYNCH to DINH and minimum (350 ns) from RPLYH (DATI) asserted to DOUT asserted.

NOTE 4: SYNCH to TIM250H negated.

NOTE 5: SYNCH to TIM250H negated with minimum time (50 ns) from SYNCH to DOUTH.

NOTE 6: SYNCH to TIM250H [DATO(B)] with minimum times (25 ns) from SYNCH to DINH and minimum (350 ns) from RPLYH (DATI) asserted to DOUT asserted.

NOTE 7: REF REQ L to TIM250H negated.

NOTE 8: REFRESH arbitration adds (90 ns) typical and (110 ns) maximum to access.

NOTE 9: REFRESH conflict adds (640 ns) typical and (690 ns) maximum to access and cycle times.

> 1.3.2.1 Voltages - The MSV11-PF memory modules require +5 V, +12 V, and -5 V for the multivoltage MOS RAMs. The -5 V is generated from the memory module. Single voltage MOS RAMs (MSV11-PK/PL) require only +5 V. Voltage margins for the +5 V and +12 V are  $\pm 5$  percent (Table 1-3).

> NOTE: Latest MSI available and in use at DIGITAL will be used for control.

> 1.3.2.2 Power Requirements - Power requirements are provided in Table 1-4.

#### 1.3.3 Environmental Specifications

Environmental specifications cover storage and operating temperature, relative humidity, altitude, and air flow specifications.

<sup>+</sup> Tacc (ns)

<sup>‡</sup> Tcyc (ns)

Table 1-3 Multi/Single Voltage MOS RAM

| Multivoltage MO   | SPAME    | /MCV/11  | DE) |

|-------------------|----------|----------|-----|

| marria orrade INO | O DAIVIS | UVISVIII |     |

|                          | Voltage               | Pins                           | Service                      |  |  |

|--------------------------|-----------------------|--------------------------------|------------------------------|--|--|

| Non Battery<br>Backed Up | +5 V<br>+12 V         | AA2, BA2, BV1, CA2<br>AD2, BD2 | TTL and MOS RAMs<br>MOS RAMs |  |  |

|                          | +5 V                  |                                | MOS RAMs and noncritical TTL |  |  |

| Battery<br>Backed Up     | +5 V BBU<br>+12 V BBU | AV1, AE1<br>AS1                | Critical TTL<br>MOS RAMs     |  |  |

#### Single Voltage MOS RAMs (MSV11-PK/PL)

|                          | Voltage            | Pins                      | Service                      |

|--------------------------|--------------------|---------------------------|------------------------------|

| Non Battery<br>Backed Up | +5 V<br>+5 V (VDD) | AA2, BA2, BV1, CA2<br>DA2 | TTL<br>MOS RAMs*             |

| Battery<br>Backed Up     | +5 V               | AA2, BA2, BV1, CA2        | noncritical TTL              |

|                          | +5 V               | AV1, AE1                  | Critical TTL<br>and MOS RAMs |

<sup>\*</sup> For systems without +5 V on DA2, +5 V can be supplied from AA2, BA2, BV1, and CA2.

## **1.3.3.1 Temperature** – Temperature is separated into the following two groups.

- 1. Operating Temperature Range The operating temperature range is  $+5^{\circ}$  C to  $+60^{\circ}$  C. Lower the maximum operating temperature by  $1^{\circ}$  C for every 1000 feet of altitude above 8000 feet.

- 2. Storage Temperature Range The storage temperature range is  $-40^{\circ}$  C to  $+66^{\circ}$  C. Do not operate a module that has been stored outside the operating temperature range. Bring the module to an environment within the operating range and allow at least five minutes for the module to stabilize.

- **1.3.3.2** Relative Humidity The relative humidity for the MSV11-P memory modules must be 10 percent to 90 percent noncondensing for storage or operating conditions.

- 1.3.3.3 Operating Airflow Adequate airflow must be provided to limit the inlet to outlet temperature rise across the module to  $5^{\circ}$  C when the inlet temperature is  $+60^{\circ}$  C. For operation below  $+55^{\circ}$  C, airflow must be provided to limit the inlet to outlet temperature rise across the module to  $10^{\circ}$  C maximum.

Table 1-4 MSV11-P Power

| MSV11-PF (Multivoltage I | MOS RAMS | ١ |

|--------------------------|----------|---|

|--------------------------|----------|---|

|                  | Standby Cur | rent (A) | Active Curre | ent (A) |

|------------------|-------------|----------|--------------|---------|

| Voltage          | Meas Typ    | Max      | Meas Typ     | Max     |

| +5 V Noncritical | 1.40        | 2.21     | 1.45         | 2.21    |

| +5 V BBU         | 1.15        | 1.55     | 1.20         | 1.55    |

| Total +5 V       | 2.55        | 3.76     | 2.65         | 3.76    |

| +12 V            | 0.10        | 0.12     | 0.35         | 0.53    |

|                  | Standby Pov | wer (W)  | Active Powe  | er (W)  |

| Voltage          | Meas Typ    | Max      | Meas Typ     | Max     |

| +5 V Noncritical | 7.00        | 11.60    | 7.25         | 11.60   |

| +5 V BBU         | 5.75        | 8.14     | 6.00         | 8.14    |

| Total +5 V       | 12.75       | 19.74    | 13.25        | 19.74   |

| +12 V            | 1.20        | 1.51     | 4.20         | 6.68    |

| Total Power      | 13.95       | 21.25    | 17.45        | 26.42   |

MSV11-PK (Single Voltage, Half Populated)

|                  | Standby Cu | rrent (A) | Active Curr | ent (A) |

|------------------|------------|-----------|-------------|---------|

| Voltage          | Meas Typ   | Max       | Meas Typ    | Max     |

| +5 V Noncritical | 1.65       | 2.10      | 1.70        | 2.10    |

| +5 V BBU         | 1.35       | 1.80      | 1.75        | 2.10    |

| Total +5 V       | 3.00       | 3.90      | 3.45        | 4.20    |

|                  | Standby Po | wer (W)   | Active Pow  | er (W)  |

|                  | Meas Typ   | Max       | Meas Typ    | Max     |

| Voltage          | (5.0)      | (5.25)    | (5.0)       | (5.25)  |

| +5 V Noncritical | 8.25       | 11.00     | 8.50        | 11.0    |

| +5 V BBU         | 6.75       | 9.45      | 8.75        | 11.0    |

| Total Power      | 15.0       | 20.45     | 17.25       | 22.0    |

MSV11-PL (Single Voltage, Fully Populated)

| Voltage                                    | Standby Current (A)<br>Meas Typ Max               | Active Current (A)<br>Meas Typ Max          |  |

|--------------------------------------------|---------------------------------------------------|---------------------------------------------|--|

| +5 V Noncritical<br>+5 V BBU               | 1.65 2.10<br>1.45 1.90                            | 1.70 2.10<br>1.85 2.20                      |  |

| Total +5 V                                 | 3.10 4.0                                          | 3.60 4.30                                   |  |

| Voltage                                    | Standby Power (W)<br>Meas Typ Max<br>(5.0) (5.25) | Standby Power (W) Meas Typ Max (5.0) (5.25) |  |

| +5 V Noncritical<br>+5 V BBU<br>Total +5 V | 8.25 11.0<br>7.25 10.0<br>15.5 21.0               | 8.50 11.00<br>9.25 11.55<br>17.75 22.55     |  |

NOTE: Typical power calculations are done at nominal voltages. Maximum power calculations are done with maximum currents at the highest voltage (nominal +5 percent).

**1.3.3.4** Altitude – The module resists mechanical or electrical damage at altitudes up to 50,000 feet (90 MM mercury) under storage or operating conditions.

NOTE: Lower the maximum operating temperature by 1° C for every 1000 feet of altitude above 8000 feet.

#### 1.3.4 Refresh

The MSV11-P memory module uses a self-contained refresh rate that is typically 650 ns every 14,500 ns. The refresh overhead maximum is 685 ns/13,500 ns or about 5 percent.

#### 1.3.5 Diagnostics

The diagnostics are CVMSAA (22-bit system) and CZKMAA (18-bit system).

#### 1.3.6 Backplane Pin Utilization

MSV11-P backplane pin utilization is shown in Table 1-5. Blank spaces indicate pins not used.

Table 1-5 Backplane Pin Utilization

|             | A Connecte         | or                 | B Connecto           | or               | CCc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | onnector           | D Con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nector            |

|-------------|--------------------|--------------------|----------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Pin         | Side 1             | Side 2             | Side 1               | Side 2           | Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 Side 2           | Side 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Side 2            |

| A<br>B<br>C | -<br>-<br>BDAL 16L | +5 V<br>-<br>GND   | BDCOK H              | +5 V             | Manual Ma | +5 V               | TORNO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | +5 V VDD          |

| D           | BDAL 17L           | +12 V              | BDAL 18L<br>BDAL 19L | GND<br>+12 V     | - Annies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | man.               | -Messi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

| E<br>F      | +5 V BBU           | BDOUT L<br>BRPLY L | BDAL 20L<br>BDAL 21L |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | max.               | Annua | 9900              |

| H<br>J      | -<br>GND           | BDIN L             |                      | BDAL             | )4L -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    | Mone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

| K           | REFKILL            | BSYNC L<br>BWTBT L | GND<br>-5 V MEAS*    | BDAL C           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | The same           | 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                 |

| -<br>И      | GND                | -<br>B1AK1L†       | -5 V MARGI<br>GND    | N* BDAL C        | 7L -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1000              |

| V           |                    | B1AK0L+            |                      | BDAL 0           | 9L -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B1AK1L‡<br>B1AK0L‡ | 100a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | energy (Marine)   |

| 7           | BREF L             | BBS7L<br>BDMG1L†   | Milital<br>Galleri   | BDAL 1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BDMG1L‡            | time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | No.               |

| 5           | +12 V BBU<br>GND   | BDMG0L+<br>BINIT L | -<br>GND             | BDAL 1           | 2L -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BDMG1L‡            | NAME .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | riskom<br>revenir |

| )           | SA16K§             | BDALOO L           | 9666                 | BDAL 1<br>BDAL 1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tin juni van j     | Military .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | mining.           |