512K-RAM-Adressierung mit flexibler MMU

2 serielle Schnittstellen

2 DMA-Kanäle

2 16-Bit-Timer

Erweiterter Befehlssatz

Höhere Geschwindigkeit

durch

Ersetzen des Z80 durch den HD64180

Helmut BernhardtDer Hersteller der HD64180-CPU benötigte zur Darstellung aller Leistungen dieses Z80-aufwärtskompatiblen Prozessors in einem "Datenblatt" ein 206 Seiten starkes Buch. Deshalb soll hier garnicht erst der Versuch gemacht werden, die Vorteile dieses Chips gegenüber seinem Vorgänger Z80 zusammenzufassen. Hier soll nur dem Bastler eine Möglichkeit gezeigt werden, wie dieser Prozessor im alten Z80-Microcomputer die Regie übernehmen soll.

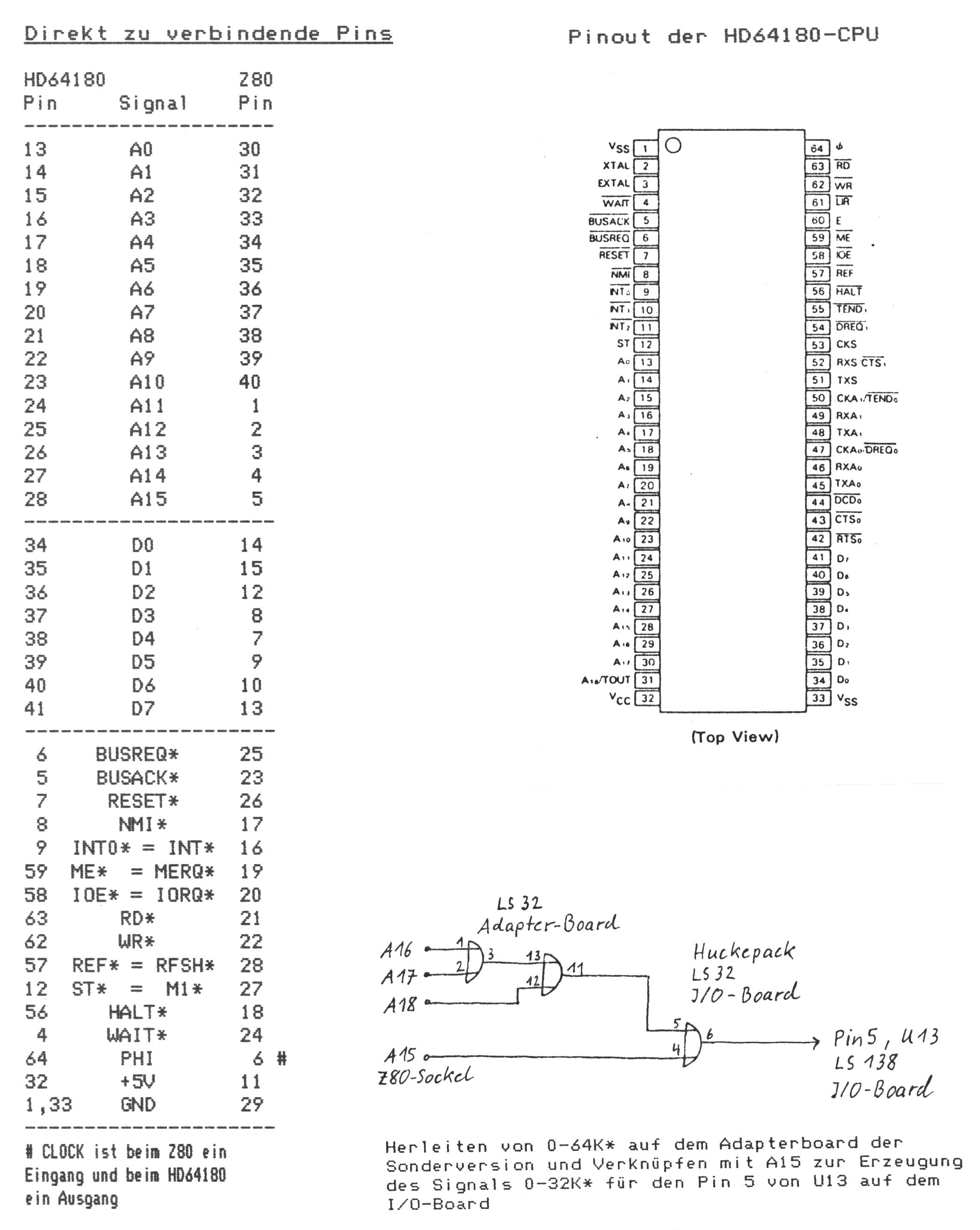

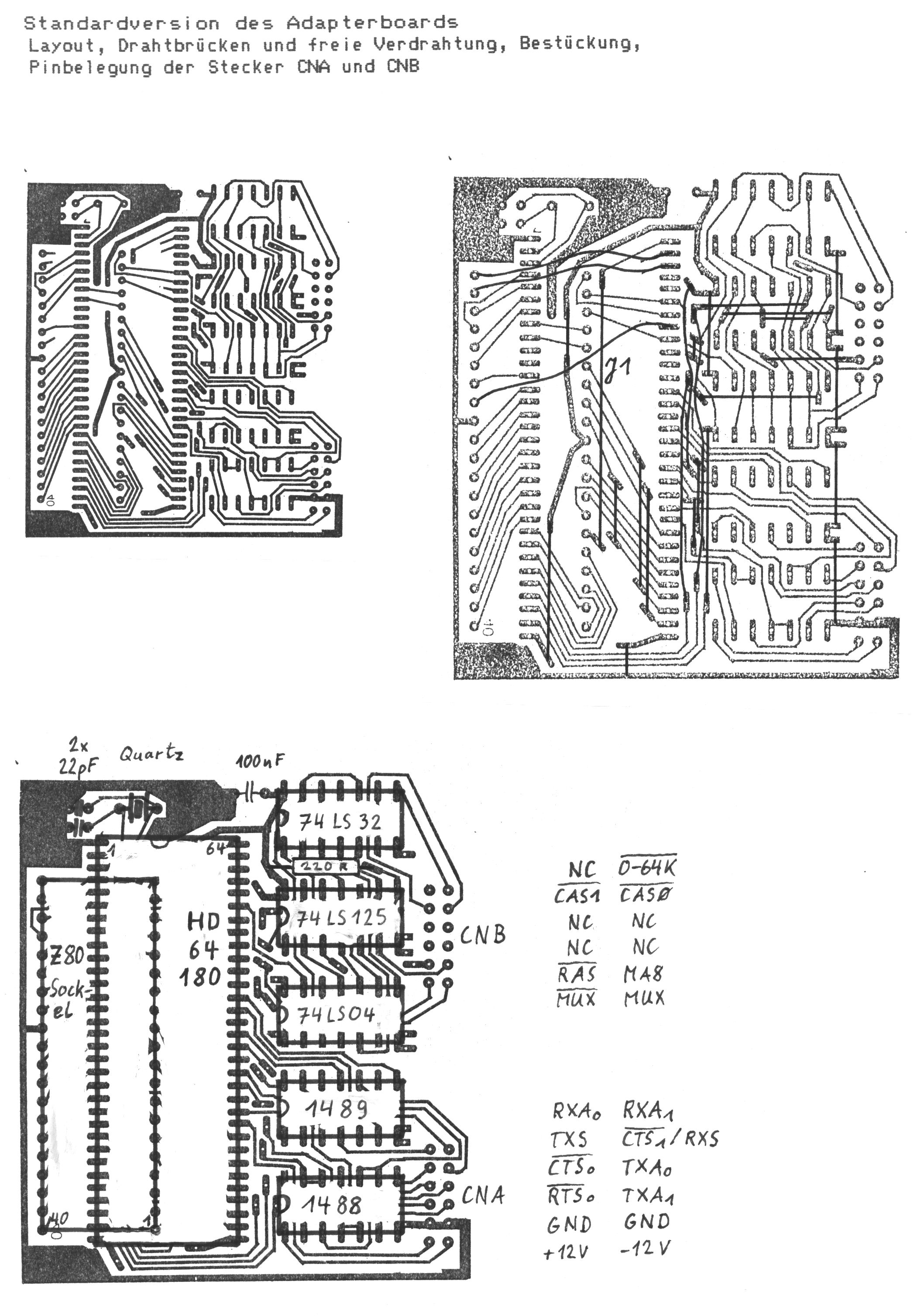

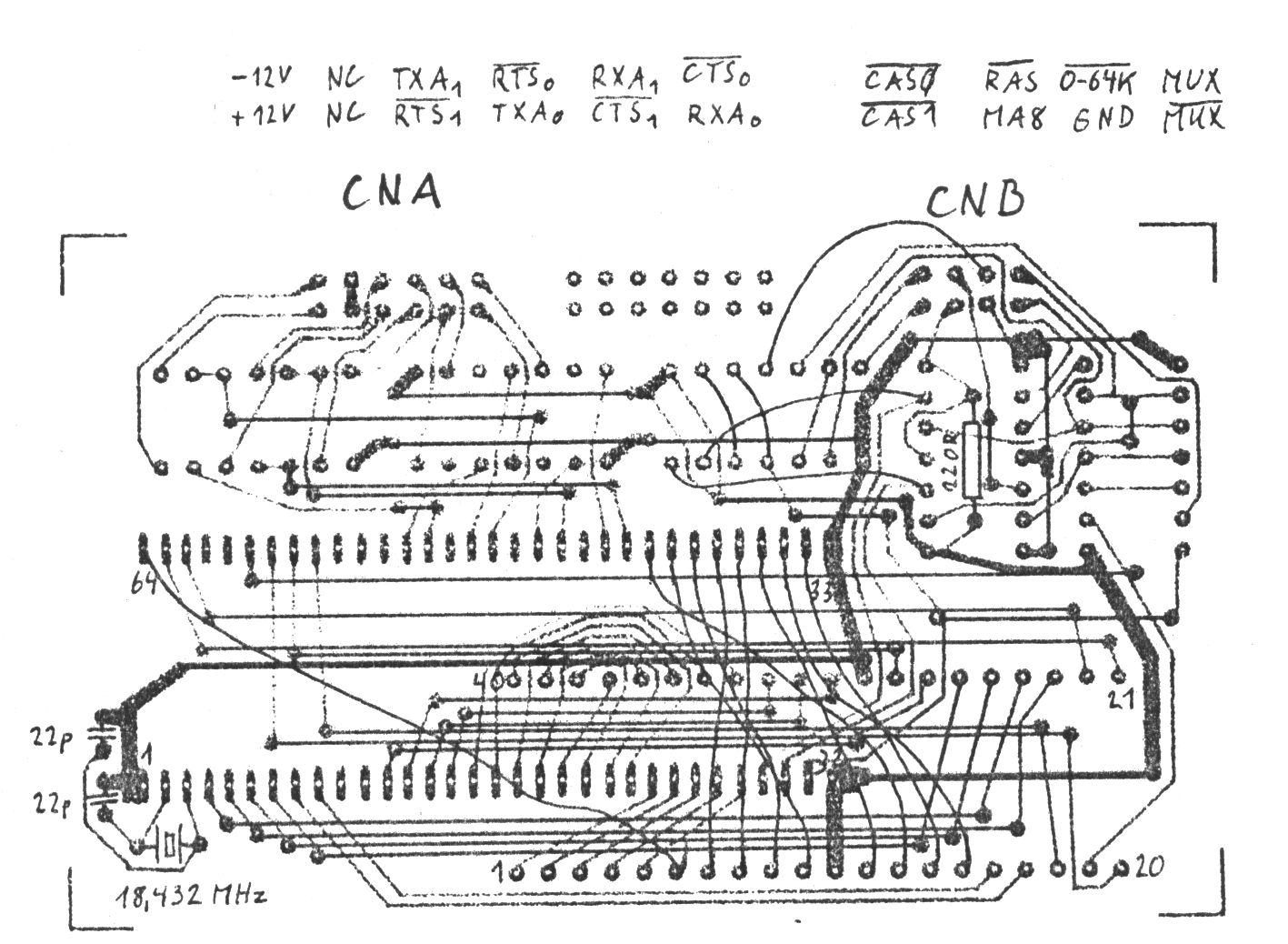

Für die Unterbringung des HD64180 anstelle des Z80 im Computer wird eine kleine Adapterplatine benötigt, an die von der Lötseite ein 40poliger Dilstecker angelötet wird und auf der die neue CPU und 5 weitere ICs untergebracht werden. Diese Platine wird in den Sockel des Z80 gesteckt und liefert über den Dilstecker alle Z80-äquivalenten Signale des HD64180 an den Computer.

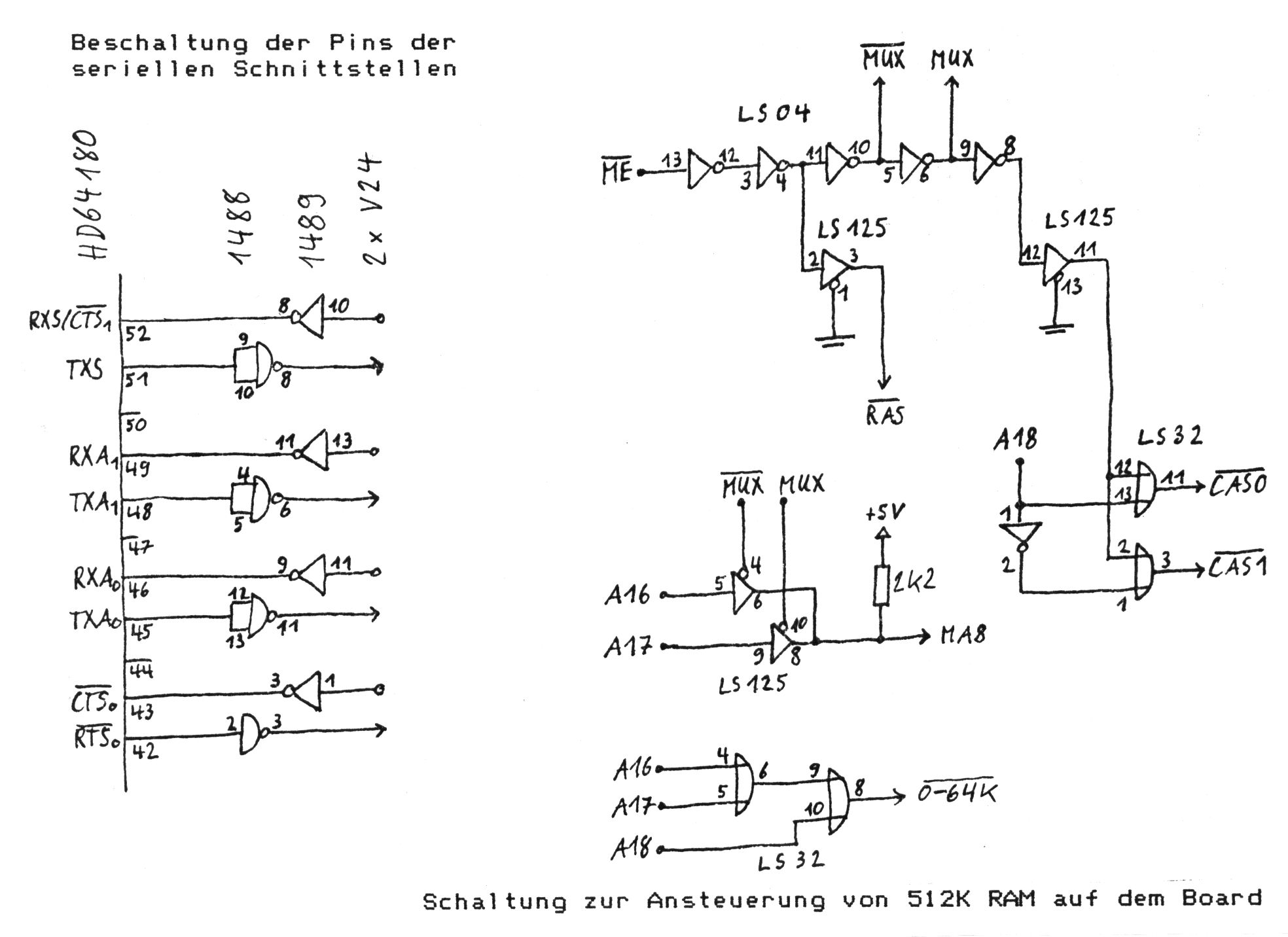

Auf der Platine sind schon zwei Treiber-ICs enthalten, die bei den Signalen der CPU-internen Seriellen Schnittstellen die Pegelwandlungen +12V/-12V => GND/+5V und umgekehrt vornehmen. Der Sendetreiber muß über zwei zusätzliche Leitungen +12 und -12V zugeführt bekommen. Die Signale der seriellen Schnittstellen können vom Stecker direkt abgenommen werden und z.B. an ein Modem geführt werden.

Auf der Adapterplatine wird der Takt für den Prozessor aus einem internen Oszillator und einem externen Qartz hergeleitet. An Pin 64 des HD64180 wird die durch 2 geteilte Qartzfrequenz, die dann dem Systemtakt entspricht bereitgestellt und kann bei Bedarf mit der Drahtbrücke J1 über den Pin 6 des Z80-Sockels an den Computer geliefert werden. Dann muß aber die bisherige Z80-Systemtaktquelle davon abgetrennt werden. Es muß geprüft werden, ob der Takt für den Z80 anderweitig als feste Frequenz verwendet wird. Dann muß dort weiterhin die Taktfrequenz für den Z80 hingeführt werden. Wenn aber der Takt für die Synchronisation mit der CPU benötigt wird, muß dieser vom Pin 64 des HD64180 entnommen werden.

Außerdem werden mit 3 weiteren ICs aus den zusätzlichen Adreßleitungen A16 bis A18 Freigabesignale für die Ansteuerung von 2 x 8 Stück 41256-RAMs und die an die Pins 1 dieser RAMs zu legende gemultiplexte RAM-Adresse MA8 erzeugt. Je nach Funktionsweise des bisherigen Adressmultiplexers für vorher 4164-RAMs wird für die Steuerung des Adressmultiplexers nun MUX oder MUX* vom Stecker CNB verwendet. Für die Wahl zwischen diesen Signalen muß geprüft werden ob das bisherige MUX-Signal low oder high aktiv war, entsprechend ist dann das low aktive MUX* oder das high aktive MUX zu verwenden. Das ist deshalb von Bedeutung, weil sonst bei Refresh die oberen Adressen an die RAMs durchgeschaltet werden, und dann das Refreshing nicht stattfinden kann.

Das Signal RAS* von CNB kann direkt anstelle des bisherigen RAS*-Signals an die RAMs gelegt werden (eventuell über 33 Ohm). Bei Bestückung des Computers mit nur 8 Stück 41256-RAMs wird nur das Signal CAS0* von CNB benötigt. Dieses Signal wird nicht direkt an die RAMs geführt sondern an den Eingang des Gatters gelegt, mit dem die Verknüpfung mit dem RAM-Freigabesignal erfolgt. Diese Stelle in der Schaltung herauszufinden, ist die einzige Anforderung an den Bastler, der sich die Vorteile des HD64180 für seinen Computer zunutze machen will. Hier muß auch geprüft werden, ob das bisherige CAS-Signal high oder low aktiv an diese Stelle gelangte. Wenn hier ein high aktives CAS nötig ist, muß CAS0* noch über einen Inverter geführt werden.

Wenn die bisherige Herleitung dieser Signale aus dem Systemtakt für den Z80 oder über Gatterlaufzeiten aus dem MERQ*-Signal erfolgte, kann diese weiterbenutzt werden. Bei einer Änderung des Systemtaktes beim Umrüsten kann bei größeren Unterschieden zwischen altem und neuem Takt eine Herleitung von RAS*, MUX bzw. MUX* und CAS* aus MERQ* über Gatterlaufzeiten eventuell nicht mehr funktionieren. Hier muß dann probiert werden, wieviele Verzögerungsgatter zwischen den einzelnen Signalen günstig sind.

Wenn das RAS*-, MUX- und CAS*-Timing bisher aus dem Systemtakt für den Z80 (nicht aus einem dazu vielfachen Muttertakt) hergeleitet wurde, kann diese Schaltung weiterbenutzt werden, indem die bisherige Taktquelle unschädlich gemacht wird und stattdessen der Takt von Pin 64 des HD64180 über Pin 6 des Z80-Sockels ins System geführt wird. Eventuelle Treiber des ursprünglichen Systemtaktes zwischen ursprünglicher Taktquelle und Z80 müssen überbrückt werden, um auch Bauteile zu erreichen, die mit dem Takt von diesem Treiber versorgt werden.

Dann werden nicht die Signale RAS*, MUX bzw. MUX* und CAS* des Adapterboards benutzt. Hier wird dann stattdessen das Signal MUX bzw. MUX* (was immer es dort ist) der bisherigen Schaltung an den Freigabe-Eingang des 74LS125-Treibers für A16 auf dem Adapterboard gelegt, der bisher mit diesem Pin verbundene Pin des 74LS04 muß dann aus der Fassung gebogen werden.

Wenn eine weitere Reihe von 8 Sockeln für RAMs vorhanden ist, oder wenn man das Risiko auf sich nehmen will, 8 weitere 41256-RAMs auf die anderen 8 Stück huckepack zu löten, dann wird der Pin 15 dieser zusätzlichen 8 RAMs mit CAS1* von CNB direkt beschaltet. Beim Huckepack-Verfahren dürfen die Pins 15 der beiden übereinander sitzenden ICs also nicht miteinander verbunden werden.

Es sei noch angemerkt, daß die meisten 4164-RAMs mit einer 7-Bit-Refreshadresse auskommen, während 41256-RAMs grundsätzlich eine 8-8it-Refreshadresse benötigen. Es muß also gewährleistet sein, daß A0-A7 beim Multiplexen zusammen durchgeschaltet werden. Bei älteren Geräten ist es wahrscheinlich, daß anstelle von A7 eine höhere Adresse zusammen mit A0-A6 durchgeschaltet wird. In diesem Fall sind A7 und die falsch angeschlossene höhere Adresse an den Multiplexer-Eingängen zu vertauschen.

Ein praktisches Beipiel

Nach diesem allgemeinen philosophischen Prolog, der eigentlich nur dem versierten Bastler prinzipiell zu berücksichtigende Punkte aufzeigt und wenig zum Wie sagt, soll nun an einem praktischen Beispiel gezeigt werden, was zu tun ist.

Das Beispiel ist ein GENIE IIs, dessen Besonderheit darin besteht daß dort eine Umschaltung des Taktes zwischen 1,77 und 5,3 (8) MHz möglilch ist. Wenn die 'LSP'-Taste gedrückt ist, das EPROM eingeschaltet ist und/oder, wenn durch die Software ein Bit in einem Steuerlatch auf 0 gesetzt wird (nach RESET ist dieses Bit immer 0), läuft der Computer nur mit 1,77 MHz. Ein Lesen des EPROMs ist bei höheren Taktraten nicht möglich. Diese Takterzeugung und -umschaltung kann für die HD64180-CPU nicht verwendet werden, mit diesem Prozessor muß man auf eine Taktumschaltung verzichten. Wegen der nach einem RESET selbstauferlegten 4 Waits dieser CPU ist es aber durchaus möglich, ein EPROM auch bei sehr hoher Taktrate noch zu lesen. Nach Abschalten des EPROMs können auch die Waits zurückgenommen werden. Der GENIE IIs läuft so mit ausschließlich 9,216 MHz ohne Probleme. Es muß allerdings darauf geachtet werden, daß vor dem Reaktivieren des EPROMs die Waits wieder eingefügt werden.

Dafür wurde einfach das Adapterboard für die Takterzeugung und -umschaltung entfernt und das 74S74-IC dieses Boards in den Sockel (U18) gesteckt, aus dem das Board entnommen wurde. Der Pin 6 dieses ICs ist aus der Fassung zu biegen. Bei U9, 74LS125 wurden die Pins 8 und 9 aus der Fassung gebogen und diese Pins des Sockels miteinander verbunden. Damit ist der Treiber zwischen alter (abgehängter) Taktquelle und Z80, Pin 6 überbrückt. Auf dem HD64180-Adapterboard werden an den dafür vorgesehenen Stellen ein 18,43 MHz-Quartz und die beiden 22pF-Kondensatoren bestückt. Der Pin 64 des HD64180 und der Pin 6 des Steckers für den Z80-Sockel werden durch einen Draht miteinander verbunden.

Beim GENIE IIs ist außerdem zu berücksichtigen, daß durch entsprechende Bits im Systemsteuerlatch zwischen RAM und memory-mapped I/O-Baugruppen innerhalb der unteren 16K umgeschaltet werden kann. Die Decodierung der Freigabesignale dieser Baugruppen berücksichtigt natürlich nur die Z80-Adressen bis A15 und nicht die HD64180-Adressen A16 bis A18. Entsprechend würden diese Baugruppen auch in den entsprechenden Adreßbereichen anderer Banks (physialische Adressen 10000H-7FFFFH) angesprochen werden.

Um dies zu verhindern, muß in der Adressdekoder-Baugruppe auf der I/O-Karte anstelle von A15 ein durch OR-Verknüpfung aus 0-64K* und A15 hergeleitetes 0-32K* Signal verwendet werden, das an den aus der Fassung gebogenen Pin 5 von U13, 74LS138 gelegt wird (Siehe Abbildung).

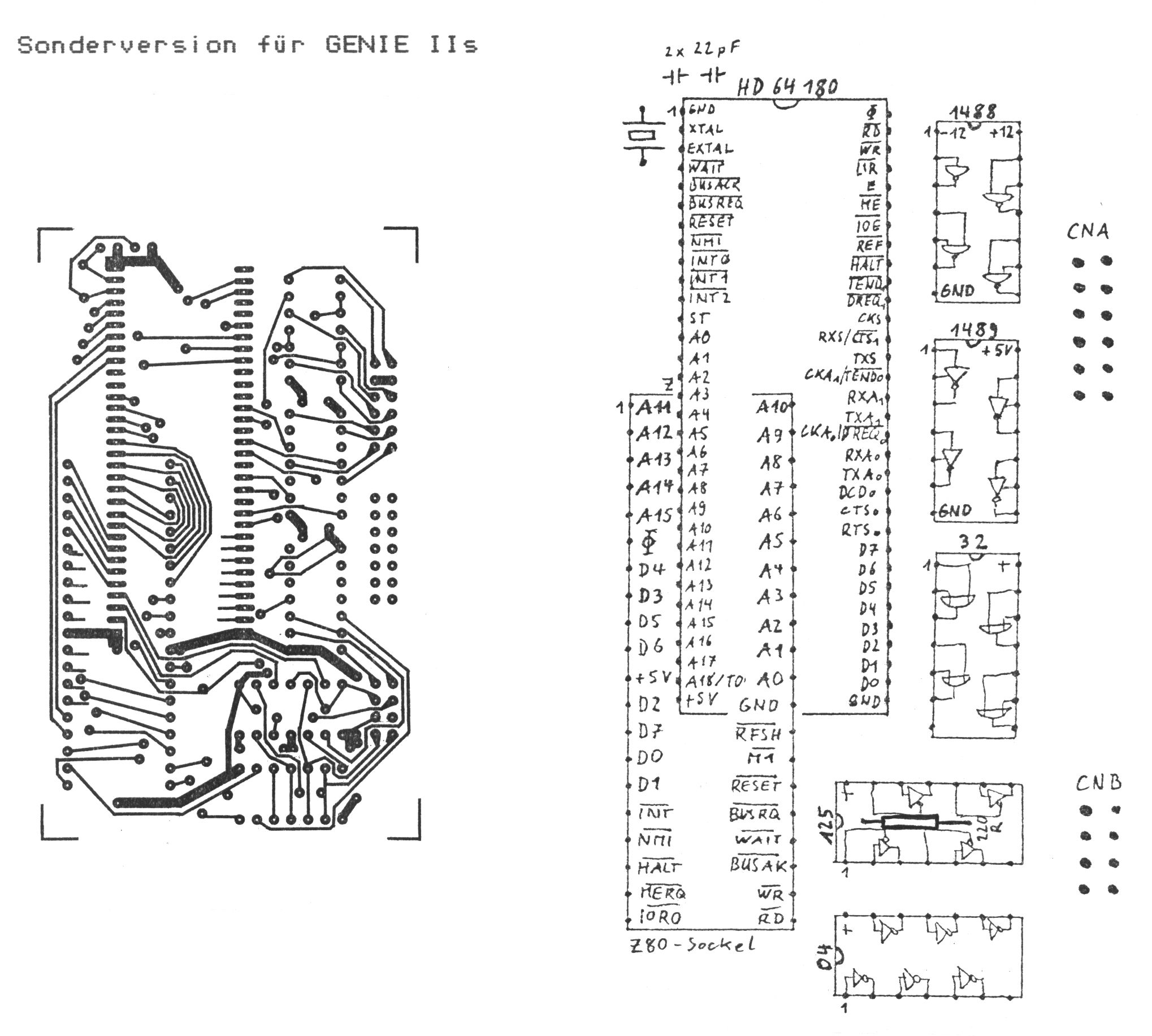

Aus geometrischen Gründen läßt sich die Standardversion des Layouts des Adapterboards im GENIE IIs nicht verwenden. Ein für diesen Computer geeignetes Layout ist ebenfalls gezeigt, bei dem aber wegen ungünstigerer Anordnung der Bauteile zueinander sehr viel mehr Drahtbrücken und freie Verdrahtungen nötig sind.

Beim GENIE IIs wird das RAS*-, MUX- und CAS*-Timing aus dem Systemtakt hergeleitet und kann deshalb beibehalten werden. Mux von Pin 1 von U6, 74S157 kann für die Umschaltung von A16 und A17 auf dem HD64180-Adapterboard verwendet werden. Dafür wird durch freie Verdrahtung von Pin 1 von U6 eine Verbindung mit MUX von CNB des Adapterboards hergestellt und der Pin 5 des 74LS04 auf dem Board aus der Fassung gebogen.

Auf dem speziell für den GENIE IIs gebauten Adapterboard muß die Erzeugung des 0-64K*-Signals noch in freier Verdrahtung nachgearbeitet werden. Dazu stehen die OR-Gatter des 74LS32 (Pins 1,2,3 und 13,12,11) noch zur Verfügung. Das Signal kann über den unbenutzten Pin des Steckers CNB dem I/O-Board zugeführt werden.

Die Sonderausführung des Adapterboards für den GENIE IIs entspricht prinzipiell auch der angegebenen Schaltung. Jedoch wurden teilweise andere Gatter innerhalb der ICs benutzt, so daß die Pin-Nummern in der Schaltung nicht überall zutreffen.

Wieviele Waits der einzelne Computer beim HD64180 und höherer Taktrate beibehalten muß, ist im Einzelfall zu untersuchen. Es ist durchaus nicht in jedem Computer ein Takt von 9,216 MHz möglich, auch wenn alle 4 Waits bei Memory-Zugriffen beibehalten werden.

Und wie geht es in meinem Computer?

Auf diese Frage hin muß ich nun doch wieder auf die allgemeingültigen Bemerkungen zurückkommen. Ich habe weder das Geld noch die Zeit noch überhaupt die Lust, diesen Hardware-Patch in allen mir zugänglichen Computern auszuprobieren, um dann für alle Geräte einfach nachzuvollziehende Lötanleitungen vorzulegen.

Ein bißchen Abenteuer und Eigenleistung und dadurch auch mehr Spaß an der Sache soll denen bleiben, die sich an dieses Projekt heranwagen. Als Unterstützung kann ich lediglich eine ungebohrte geätzte Platine (einer der beiden vorgestellten Varianten) für 10,-DM zur Verfügung stellen und eventuell fernmündlich oder -schriftlich helfen, soweit ich vom Stand meiner zwangsläufig begrenzten Hobbyistenkenntnisse und der Versorgung mit Schaltplänen der verschiedenen Geräte dazu in der Lage bin.

Über Einbauanleitungen des HD64180-Adapters in spezielle Computer (und dadurch indirekt über Erfolgsmeldungen) im Info würde ich mich sehr freuen.

Helmut Bernhardt