# FACHTHEORETISCHE ÜBUNG MIKROCOMPUTER — TECHNIK

SPEICHER-EINHEITEN BFZ/MFA 10.3.

Diese Übung ist Bestandteil eines Mediensystems, das im Rahmen eines vom Bundesminister für Bildung und Wissenschaft, vom Bundesminister für Forschung und Technologie sowie der Bundesanstalt für Arbeit geförderten Modellversuches zum Einsatz der "Mikrocomputer-Technik in der Facharbeiterausbildung" vom BFZ-Essen e.V. entwickelt wurde.

#### Inhaltsverzeichnis

#### Theorieteil 1

- 1.1 Einleitung

- 1.2 Aufbau eines Speichers (Grundprinzip)

- 1.3 Speicher-Baugruppen

- 1.4 Aufbau der Speicherzellen

- 1.5 Bausteine für Festwertspeicher

# Übungsteil 1

- A1 Oberprüfen des Inhalts von RAM-Speicherzeilen

- A2 Eingabe eines kleinen Programms in den RAM-Speicher und Überprüfen des Speicherinhalts nach kurzzeitigem Abschalten der Betriebsspannung

- A3 Lesen des Inhalts von ROM-Speicherzeilen

#### Theorieteil 2

- 2.1 Adreßdecodierung

- 2.2 Vereinfachte Schaltung einer Speicher-Baugruppe

### Obungsteil 2

- A1 Prüfen der Wirkung der Steuersignale am Eingang des Adreß-Vergleichers

- A2 Prüfen des Baugruppen-Freigabe-Signals

- A3 Prüfen der Baustein-Freigabe-Signale

# FACHTHEORETISCHE ÜBUNG MIKROCOMPUTER — TECHNIK

SPEICHER-EINHEITEN BFZ/MFA 10.3.

THEORIETEIL 1

# 1.1 Einleitung

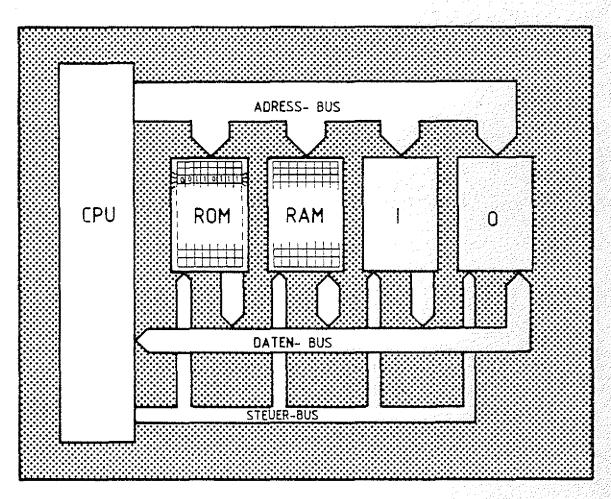

Im Speicher des Mikrocomputers werden neben der Arbeitsanweisung (Programm), die der Prozessor bearbeiten soll, auch die zu verarbeitenden Daten und Zwischenergebnisse aufbewahrt. Bei diesen Speichern handelt es sich fast ausschließlich um elektronische Speicher (Halbleiterspeicher), in denen die Informationen in binärer Form (0- und 1-Informationen) abgelegt werden. Aus Ihrer Umgebung kennen Sie andere Speicher als Träger für Informationen, z.B. werden Sprache und Musik, also akustische Signale und Informationen, magnetisch auf einem Tonband gespeichert. Das Telefonbuch ist ein Speicher, der die Informationen in Form von Schriftzeichen auf Papier aufbewahrt. Das Telefonbuch entspricht einem Nur-Lese-Speicher (ROM), da die Informationen im Speicher nur gelesen werden können. Dagegen kann die Information auf einem Tonband überschrieben werden. Dies ist das Merkmal eines Schreib-Lese-Speichers (RAM). Gleichgültig um welchen Informationsspeicher es sich handelt, sie haben alle ein gemeinsames Merkmal: "Die Informationen liegen in geordneter Form vor." Eine Ordnungsstruktur ist notwendig, um gezielt auf die gespeicherten Daten zugreifen zu können. Beim Tonband findet man mit Hilfe des Zählwerks die Position der aufgenommenen akustischen Signale. Die Ordnungsstruktur im Telefonbuch ergibt sich aus der alphabetischen Reihenfolge der Telefonbesitzer. Der Speicher im Computer geordnet, daß jeder Speicherplatz eine Adreswird dadurch se hat. Jeder Adresse entspricht genau ein Signalzustand auf dem Adreß-Bus. Muß beim Tonband der Zählerstand und beim Telefonbuch der Teilnehmername bekannt sein, um die gewünschten Informationen (Daten) wiederzufinden, so muß im Computer die Adresse bekannt sein, unter der die gesuchten (benötigten) Daten gespeichert sind.

Halbleiterspeicher

Nur-Lese-Speicher (Read only memory)

Schreib-Lese-Speicher (Random access memory) Ordnungsstruktur

# 1.2 Aufbau eines Speichers (Prinzip)

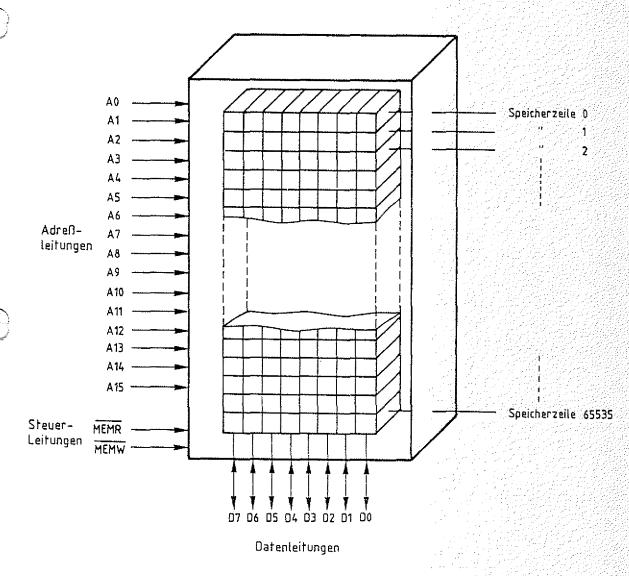

Im Bild 1 ist der Aufbau eines Speichers dargestellt. Jedem Signalzustand auf den Adreßleitungen AO bis A15 ist eine Speicherzeile zugeordnet. Eine Speicherzeile umfaßt jeweils acht Bit und ist somit an die Daten-Bus-Struktur des Prozessors angepaßt.

Speicherzeile

Bild 1: Aufbau eines Speichers ( Prinzip )

Der Prozessor unterscheidet nach dem Aussenden einer Adresse auf dem Adreß-Bus zwischen dem Lesen des Inhalts einer Speicherzeile und dem Speichern von Daten in eine Speicherzeile. Das Lesen einer Speicherzeile erfolgt mit dem Steuersignal MEMORY READ (MEMR) und das Ablegen eines Daten-Bytes im Speicher mit MEMORY WRITE (MEMW). Die Überstreichung der Kurzbezeichnungen MEMR und MEMW macht deutlich, daß es sich um Low-aktive Signale handelt. Ein Teil der möglichen Speicheradressen auf dem Adreß-Bus ist in Bild 2 zusammengefaßt.

MEMORY READ

MEMORY WRITE

|    |      |                | Si        | gnalz | ustä      | nde   | auf       | den            | Adre | Aleit    | unge | n              |    |           |   | Hex.<br>Adr. | Speicher-<br>zeile |

|----|------|----------------|-----------|-------|-----------|-------|-----------|----------------|------|----------|------|----------------|----|-----------|---|--------------|--------------------|

| 15 | 14   | 13             | 12        | 11    | 10        | 9     | 8         | 7              | 6    | 5        | 4    | 3              | 2  | 1         | 0 |              |                    |

| Ĺ  | L    | L              | ٦         | L     | _1        | L     | L         | L              | L    | Ļ        | L    | L              | L, | L         | Ļ | 0000         | 0                  |

| L  | Ļ    | L              | Ļ         | L     | L         | L     | L         | L              | L    | L        | L    | L              | Ļ  |           | H | 0001         |                    |

| L  | L    | L              | L         | L     | L         | L     | L         | L              | L    | L        | Ļ    | L              | L  | Ŧ         | L | 0002         | 2                  |

| L  | Ĺ    | L              | L         | L     | L         | L     | L         | L              | L    | L        | L    | L              | L  | Η         | Н | 0003         | 3                  |

| L  | L    | L              | L         | L,    | L         | L     | L         | L              | L    | L.       | L    | L              | Н  | L         | L | 0004         |                    |

|    | <br> | 1              | <br> <br> |       | <br> <br> | i<br> | !<br>[    | <u> </u>       |      |          |      | 1<br> <br>     | [  |           |   |              |                    |

| L  | Н    | L              | Н         | Н     | Н         | L     | L         | Н              | Н    | Н        | Н    | L              | Н  | Н         | Н | 5CF 7        | 23799              |

|    |      | <br> <br> <br> | [         |       |           |       | <br> <br> | <br> <br> <br> | 1    | <u> </u> |      | <br> <br> <br> | 1  | <br> <br> |   |              |                    |

| Н  | Н    | Н              | Н         | Н     | Н         | Н     | Н         | Н              | Н    | Н        | Н    | Н              | Н  | Н         | L | FFFE         | 65534              |

| H  | Н    | Н              | Н         | Н     | Н         | Н     | Н         | Н              | Н    | Н        | Н    | Н              | Н  | Н         | Н | FFFF         | 65535              |

Bild 2: Mögliche Speicheradressen auf dem Adreß-Bus

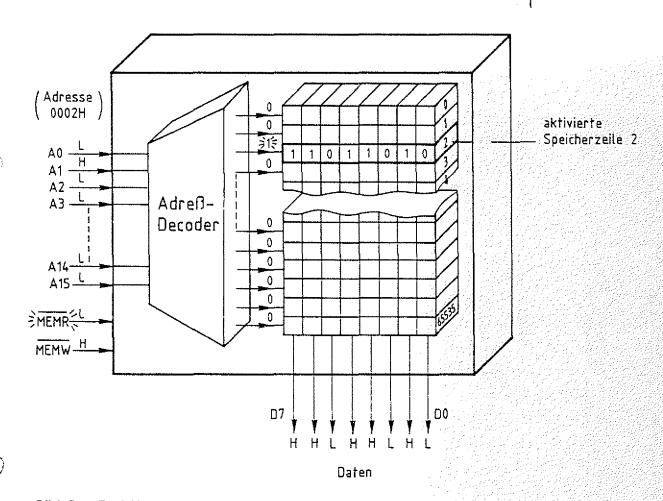

Mit den 16 Adreßleitungen können 65536 (2<sup>16</sup>) Speicherzeilen unterschieden werden. Zentrales Element hierzu in einem Speicher ist ein Adreß-Decoder (Bild 3). Dieser wählt aufgrund des Signalzustandes auf den Adreßleitungen die zugehörige Speicherzeile aus. Liegt beispielsweise am Adreß-Bus die Adresse 0000H an, so wird die Zeile 0 ausgewählt, bei 0001H die Zeile 1,... und bei FFFFH die Zeile 65535.

Adreß-Decoder

Ein Lesevorgang der Speicherzeile 0002H ist im Bild 3 dargestellt. Mit dem Steuersignal  $\overline{\text{MEMR}}$  wird der Speicherinhalt auf den Daten-Bus geschaltet und kann vom Prozessor gelesen werden.

Bild 3: Funktionsweise des Adreß-Decoders

Ein Kennwert des Speichers ist neben der Speichergröße - auch Speicherkapazität genannt - insbesondere die Zugriffszeit. Das ist die Zeit, die der Speicher nach Aktivierung des entsprechenden Steuersignals benötigt, um den Speicherinhalt einer adressierten Speicherzeile bereitzustellen bzw. ein Daten-Byte in die Speicherzeile zu übernehmen. Diese Zeit liegt bei üblichen Speichern in der Größenordnung von einigen hundert Nanosekunden. Die Angabe der Speicherkapazität erfolgt in der "Einheit" KByte (K=Kilo).

Speicherkapazität Zugriffszeit

**KByte**

Beachten Sie, daß das "K" im Gegensatz zu unserer alltäglichen Kilo-Angabe groß geschrieben wird. Bedeutet bei Maßund Gewichtsangaben 1 kilo gleich 1000, so bezeichnet 1 KByte

in der Computertechnik 1024 Byte. Mit 10 Adreßleitungen kann

man 1024=2<sup>10</sup> Speicherzeilen ansteuern. Ein Mikrocomputer,

der über 16 Adreßleitungen verfügt, kann insgesamt 64 KByte

adressieren. Dies kann auf folgende Weise veranschaulicht

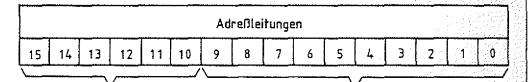

werden (Bild 4):

1KByte=1024 Byte

6 Adreßleitungen ergeben 2<sup>6</sup> = 64 mögliche 1-KByte-Speicher 10 Adreßleitungen für einen 1-KByte-Speicher

Bild 4: Verteilung von 16 Adressleitungen auf 64 einzelne 1-KByte-Speicher

Beim Einsatz eines Mikrocomputers kommt es häufig vor, daß wesentlich kleinere Speicher als 64-KByte-Speicher für die Aufnahme der Programme und Daten benötigt werden. Außerdem sind fast immer Nur-Lese- und Schreib-Lese-Speicher erforderlich. Aus diesen und anderen Gründen werden kleinere RAM- und ROM-Module (-Einheiten) verwendet, die man in gewünschter Weise kombiniert.

Es gibt Anwendungsfälle, bei denen der Nur-Lese-Speicher (ROM) nicht größer als 1 KByte ist und 1/4-KByte-RAM ausreichend sind. Es kann auch vorkommen, daß der Speicherbereich von 64 KByte nicht ausreicht. Dann greift man auf andere Speichermedien (-Geräte/-Techniken) zurück, z.B. auf einen Magnetplattenspeicher. Das Speicherprinzip entspricht dem des Tonbandgerätes, bei dem durch Magnetisierung die Information auf einen magnetischen Träger aufgebracht wird. Beim Magnetplattenspeicher ist der Träger eine rotierende Magnetplatte. Je nach Plattensystem können Vielfache von 64 KByte

Magnetplattenspeicher

auf einer Platte gespeichert werden. Die Angabe der Speicher-kapazität eines Plattensystems erfolgt bei entsprechender Größe in Mega-Byte, wobei 1 MByte gleich 1000 KByte sind. Bei diesen Systemen wird der Computer veranlaßt, immer nur den Programmteil von der Platte in den Systemspeicher zu laden, der gerade bearbeitet werden muß. Weitaus häufiger werden aber in der Mikrocomputertechnik kleine Speicher-Einheiten verwendet, die im folgenden Abschnitt behandelt werden.

MByte

# 1.3 Speicher-Baugruppen

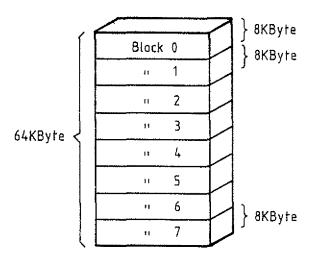

Eine mögliche Unterteilung des gesamten Systemspeichers in acht gleichgroße Speicherblöcke ist im Bild 5 dargestellt. Jeder Speicherblock hat eine Kapazität von 8 KByte. Es sind auch andere Aufteilungen möglich, das angewandte Prinzip ist jedoch immer ähnlich.

Bild 5: Aufteilung des 64-KByte-Systemspeichers in acht 8- KByte Speicherblöcke

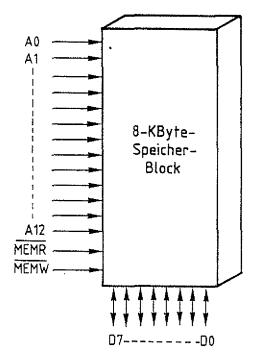

Betrachten wir zunächst einen dieser 8-KByte-Blöcke (Bild 6). Für die Adressierung der Speicherzeilen werden die 13 Adreß-leitungen AO bis A12 benötigt.  $(2^{13}=2^3\times2^{10}=8\times1024)$

Bild 6: Die Adreßleitungen für einen 8-KByte-Speicherblock

Von den 16 Adreßleitungen des Mikroprozessors verbleiben die drei Leitungen A13, A14 und A15. Über diese drei Leitungen kann man die acht verschiedenen Blöcke unterscheiden, wenn jedem Block einer der acht möglichen Signalzustände auf diesen Leitungen zugeordnet wird. Dies ist in Bild 7 dargestellt.

| 8lock- | Adrefileitungen |     |     |             |  |  |  |

|--------|-----------------|-----|-----|-------------|--|--|--|

| Nr.    | A15             | A14 | A13 | A12 A0      |  |  |  |

| 0      | L               | L   | Ļ   | für Block 0 |  |  |  |

| 1      | L               | L   | Н   | für Block 1 |  |  |  |

| 2      | Ĺ               | Н   | L   | für Block 2 |  |  |  |

| 3      | L               | н   | Н   | für Block 3 |  |  |  |

| 4      | Н               | L   | L   | für Block 4 |  |  |  |

| 5      | н               | L   | Н   | für Block 5 |  |  |  |

| 6      | Н               | Н   | L   | für Block 6 |  |  |  |

| 7      | Н               | Н   | Н   | für Block 7 |  |  |  |

Bild 7: Unterscheidung von 8 Blöcken durch die Adressleitungen A13, A14 und A15

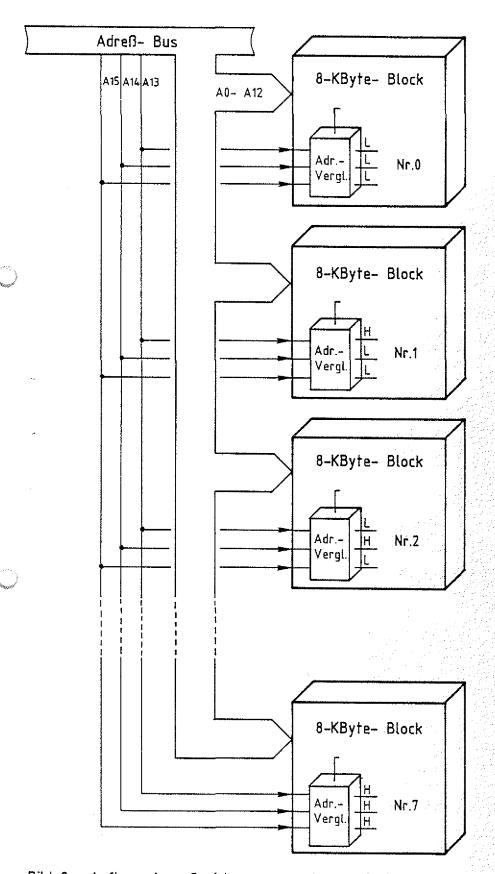

Die acht Signalzustände kann man als Block- oder Baugruppen-Nummer auffassen, ähnlich wie die Baugruppen-Nummer der Einund Ausgabe-Baugruppen. Für die Erkennung dieser Block- oder Baugruppen-Nummer muß jeder Speicherblock einen Adreßvergleicher besitzen, der den Signalzustand auf den Adreßleitungen A13, A14 und A15 mit einem vorgegebenen Signalzustand vergleicht, welcher der Block- oder Baugruppen-Nummer entspricht. Dieses Verfahren hat den Vorteil, daß alle Speicherblöcke vollkommen gleich aufgebaut und universell einsetzbar sind. Die entsprechend der Problemstellung geforderte Speichergröße eines Mikrocomputersystems kann man jetzt durch die Anzahl der Blöcke anpassen. Außerdem wird es so möglich, RAM- und ROM-Blöcke miteinander zu kombinieren.

Bild 8 zeigt, wie mehrere 8-KByte-Speicherblöcke an den Adreß-Bus des Systems angeschlossen sind.

Block-Nummer

Baugruppen-Nummer

Bild 8: Aufbau eines Speichers aus mehreren 8-KByte-Speicherblöcken

Der Adreßbereich, den ein einzelner 8-KByte-Speicherblock im Systemspeicher überdeckt, hängt von der eingestellten Blocknummer ab. In Bild 9 ist für jeden der acht Blöcke die Adresse der ersten und der letzten Speicherstelle im Block aufgeführt. Die erste Adresse in einem Block nennt man auch Basis-Adresse.

Basis-Adresse

|    |        |    |    | Sign | alzus | tände | auf | den     | Adrefi | leitur | igen |      |    |   |   | Adreßbe-<br>reich | Block- |

|----|--------|----|----|------|-------|-------|-----|---------|--------|--------|------|------|----|---|---|-------------------|--------|

| 15 | 14     | 13 | 12 | 11   | 10    | 9     | 8   | 7       | 6      | 5      | 4    | 3    | 2  | 1 | 0 | von<br>bis        | Nr.    |

| L  | Ļ      | Ļ  | L. | L    | L     | L     | L   | L       | L      | L      | L    | Ļ    | L  | L | L | 0000              |        |

| L  | :<br>L | L. | н  | н    | Н     | Н     | H   | Н       | Н      | Н      | н    | Н    | Н  | Н | Н | 1FFF              | 0      |

| L  | Ŀ      | Н  | L  | L    | L     | L     | L   | L       | Ļ      | Ĺ      | L    | L    | L  | L | L | 2000              |        |

| L  | :<br>L | Н  | Н  | Н    | Н     | Н     | Н   | н       | Н      | H      | нΙ   | Н    | Н  | Н | Н | 3FFF              | 1      |

| L. | Н      | L  | L  | L    | L     | L     | L   | L       | L      | L      | L    | Luna | L. | L | Ļ | 4000              |        |

| L  | :<br>H | L  | Н  | Н    | н     | Н     | Н   | Н       | Н      | Н      | Н    | н    | Н  | Н | Н | SFFF              | 2      |

| L  | H      | Н  | L. | L    | L     | L     | L   | L       | L      | L      | L    | Ļ    | L  | L | 1 | 6000              |        |

| L  | Н      | Н  | Н  | Н    | Н     | н     | Н   | <br>  H | Н      | н      | Н    | Н    | Н  | Н | Н | 7FFF              | 3      |

| Н  | L      | L  | L  | L    | L     | L.    | L   | L       | L      | L      | Ĺ    | L    | L  | L | L | 8000              |        |

| Н  | L      | L  | н  | н    | H     | H     | Н   | Н       | Н      | Н      | Н    | Н    | Н  | Н | Н | 9FFF              | 4      |

| Н  | Ļ      | Н  | L  | L    | L     | L     | Ļ   | L       | L      | L      | L    | L    | L  | L | L | A000              |        |

| Н  | :<br>L | Н  | н  | Н    | Н     | Н     | H   | Н       | Н      | Н      | Н    | н    | Н  | Н | H | BFFF              | 5      |

| Н  | H      | L  | L  | L    | L     | L     | L   | L       | L      | Ļ      | L    | Ļ    | L  | ι | L | C000              |        |

| Н  | :<br>H | L  | Н  | Н    | Н     | Н     | Н   | Н       | Н      | Н      | Н    | Н    | Н  | Н | Н | DFFF              | 6      |

| н  | Ħ      | Н  | L  | L    | L     | L     | Ļ   | L       | L      | Ļ      | L    | Ļ    | L  | L | L | E000              |        |

| Н  | :<br>H | н  | н  | н    | Н     | Н     | Н   | Н       | Н      | Н      | н    | Н    | Н  | Н | Н | FFFF              | 7      |

Bild 9: Die erste (Basis-Adresse) und letzte Adresse für die acht möglichen 8-KByte-Speicherblöcke

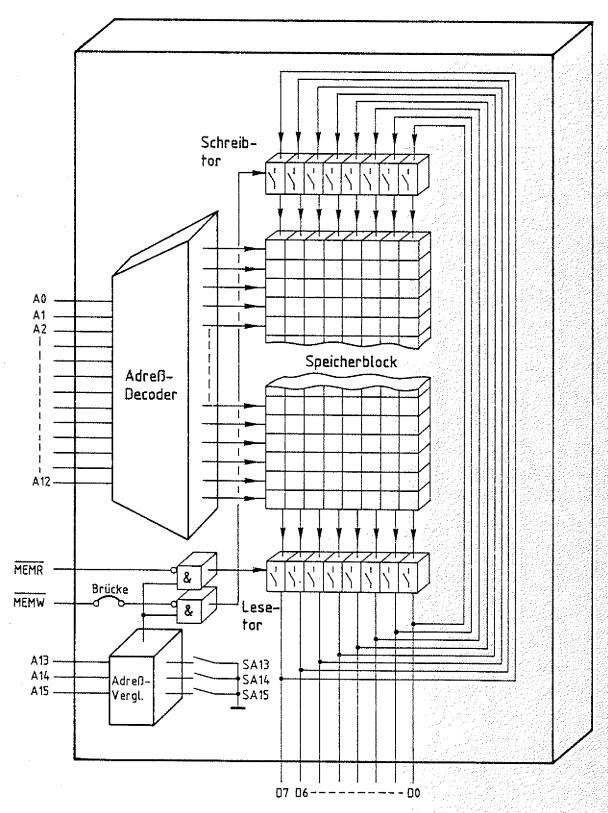

Das folgende Bild 10 zeigt detaillierter den Aufbau einer 8-KByte-RAM-Baugruppe. Neben Adreßdecoder, Speicherblock und Adreßvergleicher sind ein Lese- und ein Schreibtor eingefügt. Das Lesetor schaltet den Inhalt einer Speicherzeile auf den Daten-Bus, sofern die Baugruppen-Nummer oder Block-Nummer an den Adreßleitungen A13 bis A15 ansteht und das Steuersignal MEMORY READ (MEMR) L-Pegel führt.

Lesetor, Schreibtor

Bild 10: Aufbau einer 8-KByte-Speicherbaugruppe (8-KByte-Speicherblock)

Die Datenübernahme in eine Speicherzeile erfolgt dagegen mit der Freigabe des Schreibtors, wobei die Daten-Bus-Signale zur adressierten Speicherzeile durchgeschaltet werden und der alte Inhalt überschrieben wird. Die Schreibfreigabe wird durch den L-Pegel des Steuersignals MEMORY WRITE (MEMW) ausgelöst. Voraussetzung ist, daß auf den Adreßleitungen A15, A14 und A13 die Block-Nummer ansteht.

Für die technische Realisierung dieser Baugruppe stehen zwar heute 8-KByte-Speicher-ICs zur Verfügung, jedoch verwendet man meist mehrere kleinere Speicherbausteine mit Speicherkapazitäten von 1, 2 oder 4 KByte. Falls es sich um RAM-Bausteine handelt, sind in ihnen Adreß-Decoder und Lese- und Schreibtor integriert. Einige Hersteller bieten pinkompatible RAM- und ROM-Bausteine an; sie sind bis auf das Schreibtor prinzipiell gleich aufgebaut und haben die gleiche Signalbelegung an den Anschlüssen. Damit kann man durch Austausch von RAM- und ROM-Bausteinen eine RAM-Baugruppe einfach in eine ROM-Baugruppe umwandeln. In diesem Fall wird das Steuersignal MEMW auf der Speicher-Baugruppe nicht benötigt und durch öffnen einer Brücke unterbrochen (Bild 10).

Greift der Prozessor auf die Speicher-Baugruppe zu, so löst er die folgenden Schritte aus: Der Prozessor...

- sendet die Adresse der gewünschten Speicherzeile auf dem Adreβ-Bus aus.

- veranlaßt den Speicher, entweder durch das Steuersignal MEMR, den Speicherinhalt auf den Daten-Bus zu schalten oder durch das Steuersignal MEMW den Signalzustand vom Daten-Bus in die Speicherzeile zu übernehmen.

- übernimmt beim Lesen mit dem Abschalten des Steuersignals MEMR die Daten vom Bus oder beendet den Schreibvorgang durch Wegschalten des Signals MEMW.

pinkompatibel

#### 1.4 Aufbau der Speicherzellen

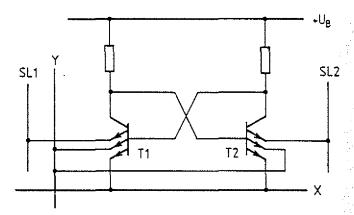

Wie schon erwähnt wurde, handelt es sich bei den verwendeten Speichern meist um Halbleiterspeicher, in denen die einzelnen Speicherzellen (für 1 Bit) hauptsächlich mit Dioden und Transistoren aufgebaut sind. Grundelement einer RAM-Speicherzelle z.B. ist eine bistabile Kippstufe, wie in Bild 11 dargestellt.

Bild 11: Prinzipieller Aufbau einer RAM-Zelle

Die beiden stabilen Zustände sind dadurch gekennzeichnet, daß entweder Transistor T1 leitet und T2 gesperrt ist oder T1 sperrt und T2 leitet. Den beiden Zuständen wird der Speicherinhalt "0" und "1" zugeordnet. Über die Leitungen X und Y wird die gewünschte Speicherzelle adressiert, über die Leitungen SL1 und SL2 (Schreib-Lese-Leitungen) kann der Inhalt der Speicherzelle gelesen oder ein neuer eingeschrieben werden.

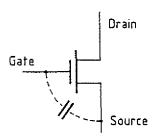

Wegen des einfachen Herstellungsprozesses werden die Speicherzellen meist mit MOS-Transistoren aufgebaut, die außerdem höhere Packungsdichten ermöglichen und geringere Verlustleistung haben. Eine noch höhere Packungsdichte und geringere Verlustleistung erhält man bei einer Technik, bei der die Information in einem kleinen Kondensator gespeichert wird, und zwar in der Gate-Source- oder Gate-Drain-Kapazität eines MOS-Transistors. Das Prinzip dieser Speicherzelle zeigt Bild 12.

Halbleiterspeicher

Speicherzelle

Bistabile Kippstufe

(Flipflop)

MOS-Transistor

Kondensator Gate-Source-Gate-Drain-Kapazität

Bild 12: Prinzip der kapazitiven Informationsspeicherung in einem MOS-Transistor

Die beiden möglichen Signalzustände der Speicherzelle werden hier dem geladenen bzw. entladenen Kondensator zugeordnet. Bei dieser Speichertechnik ist allerdings eine sogenannte Auffrischschaltung erforderlich. Sie muß den

ständigen Ladungsverlust der Kondensatoren ausgleichen, der

aufgrund unvermeidbarer Leckströme in der Isolierschicht

auftritt. Schaltungen dieser Art nennt man im englischen

"refresh circuit".

Weil ständig für diesen Auffrischvorgang auf die Speicherzellen zugegriffen werden muß (etwa alle 2msec), nennt man diese Speicher "dynamische RAMs" (Dynamik, Bewegung) im Gegensatz zu den Flipflop-Zellen, die man entsprechend "statische RAMs" (Statik, Ruhe) nennt.

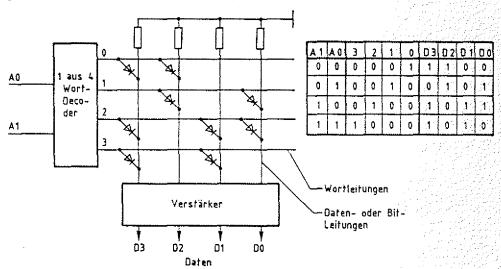

Das Prinzip eines ROMs ist die Diodenmatrix (Bild 13). Jeder Kreuzungspunkt der horizontalen und vertikalen Leitungen der Matrix stellt eine Speicherzelle dar.

Bild 13: Prinzip eines ROM-Speichers Kapazität: 4x4Bit ( 4 Worte a' 4Bit )

Kapazitive Informationsspeicherung

Auffrischschaltung refresh circuit

Dynamisches RAM

Statisches RAM

ROM Diodenmatrix

Der Wort-Decoder ist so aufgebaut, daß abhängig vom Signalzustand auf den Adreßleitungen, nur einer der Decoder-Ausgänge 1-Signal haben kann. Die ausgewählte Wortleitung legt

nun alle Datenleitungen, die mit ihr über Dioden verbunden

sind, auf H-Pegel. Die nicht mit ihr verbundenen Datenleitungen erhalten über die Widerstände L-Pegel. Die Tabelle

in Bild 13 zeigt den ROM-Inhalt, abhängig von den möglichen

Adressen. Die Programmierung des Speichers erfolgt also dadurch, daß während seiner Herstellung an gewünschten Kreuzungspunkten zwischen Wort- und Datenleitungen (oft auch

Bit-Leitungen genannt) Dioden eingebaut werden. Je nach

Herstellungsverfahren werden anstelle der Dioden auch Widerstände, bipolare Transistoren und MOS-Transistoren verwendet.

1.5 Bausteine für Festwertspeicher (ROMs)

Der gewünschte ROM-Inhalt wird in einem der letzten Produktionsschritte in die Bausteine eingebracht. Diese Bausteine heißen "maskenprogrammierbare ROMs". Der Name "maskenprogrammiert" rührt von den Fertigungsschritten her, die sogenannte Masken für die Diffusionsprozesse erfordern. Dieses Verfahren ist teuer und wird nur bei hohen Stückzahlen angewandt. Außerdem kann ein fehlerhafter Inhalt nicht korrigiert werden. Nachteilig kommt hinzu, daß die notwendigen Fertigungseinrichtungen nicht jedem zugänglich sind. Daher hat man sogenannte PROM-Bausteine entwickelt. PROM heißt programmierbares ROM und bedeutet. daß der Anwender durch einen speziellen Vorgang die gewünschte Information in das ROM einbringen (programmieren) kann. Dazu liefert der Hersteller ROM-Bausteine, bei denen alle Speicherstellen entweder nur "0"- oder "1"-Informationen enthalten. In diesem Fall spricht man von unprogrammierten PROMs. Auch diese Bausteine haben den Nachteil, daß sie nicht wieder verwendbar sind, wenn eine falsche Information einprogrammiert wurde.

Wort-Decoder

Wortleitung Datenleitung

Programmierung des ROMs

maskenprogrammiert

PROM-Bausteine

Fehler treten aber häufig in der Entwicklungsphase eines Programms auf, so daß man für den Anwender wiederverwendbare PROMs entwickelt hat, die man programmieren und wieder löschen kann. Diese Bausteine heißen EPROMs, d.h. lösch-(erasable) und programmierbare ROMs. Zum Löschen werden die ICs, die ein Quarzglasfenster besitzen, mit UV-Licht beleuchtet. Mittlerweile gibt es auch elektrisch löschbare (electrical erasable) und programmierbare ROMs, die man entsprechend EEPROM nennt.

**EPROM**

EEPROM

# 1.6 RAM-Speicher als Festwertspeicher

Schreib- Lese-Speicher (RAM) zieht man in Mikrocomputer-Systemen den Festwertspeichern immer dann vor, wenn man in der Programm-Entwicklungsphase das Programm und damit den Speicherinhalt ständig ändern muß.

Will man den Speicherinhalt von RAM-Zellen über längere Zeit erhalten, so muß man sie ständig mit Spannung versorgen, denn die Kondensatoren in dynamischen RAMs entladen sich, und Fliflops nehmen beim Einschalten der Spannung die Zustände O oder 1 in zufälliger Weise an. Zur Konservierung der Speicherinhalte verwendet man Batterien und spricht von Batteriepufferung und gepufferten RAMs.

gepuffertes RAM

# FACHTHEORETISCHE ÜBUNG MIKROCOMPUTER — TECHNIK

SPEICHER-EINHEITEN

BFZ/MFA 10.3.

ÜBUNGSTEIL 1

zusammengebaut und

geprüft nach

FPU BFZ/MFA 1.2.

Arbeitsblatt A7

# Übungsteil 1

In den folgenden Arbeitsschritten werden Sie Messungen an einer RAM- und an einer ROM-Baugruppe durchführen.

# Dazu benötigen Sie:

- 1 Baugruppenträger mit Busverdrahtung (BFZ/MFA 0.1.)

- 1 Bus-Abschluß (BFZ/MFA 0.2.)

- 1 Trafo-Einschub (BFZ/MFA 1.1.)

- 1 Spannungsregelung (BFZ/MFA 1.2.)

- 1 Bus-Signalgeber (BFZ/MFA 5.1.)

- 1 Bus-Signalanzeige (BFZ/MFA 5.2.)

- 1 8-K-RAM/EPROM bestückt mit RAM (BFZ/MFA 3.1.)

- 1 8-K-RAM/EPROM bestückt mit EPROM MAT 85 (BFZ/MFA 3.1.)

# Allgemeine Hinweise zur Durchführung der Übungen:

- Die Einschübe dürfen nur bei abgeschalteter Betriebsspannung gesteckt oder gezogen werden

- Aufgrund der Busverdrahtung können die Baugruppen in beliebige Steckplätze gesteckt werden

- Den logischen Signalen "O" und "1" sind die folgenden Pegel zugeordnet:

- Alle zur Messung an den Baugruppen vorgegebenen Arbeitsblätter enthalten:

- = Angaben über den Sinn der jeweiligen Messung

- = Angaben über einzustellende Bedingungen (z.B. Schalterstellungen)

- = Aufgabenstellungen, ggf. mit Hinweisen zu möglichen Fehlern.

# Übungsteil 1

# Bedienungshinweise:

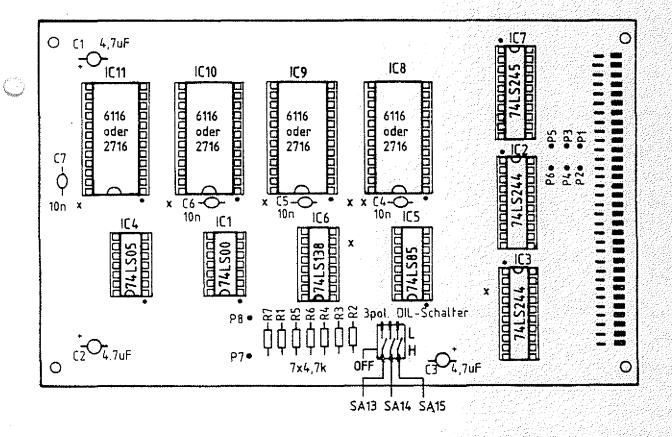

#### 8-K-RAM/EPROM-Baugruppe als RAM-Baugruppe:

- Die IC-Sockel IC8, IC9, IC10, IC11 müssen mit RAM-Bausteinen 6116P-3 bestückt sein

- Wenn keine vier Bausteine bestückt sind, müssen Sie mindestens einen Baustein in den Sockel IC8 stecken

- Die Lötpunkte P3-P4 und P5-P6 müssen gebrückt sein

- Mit den Schaltern SA13, SA14 und SA15 muß die Baugruppen-Nummer O eingestellt werden (siehe dazu folgende Seite)

# 8-K-RAM/EPROM-Baugruppe als EPROM-Baugruppe:

- Die IC-Sockel IC8 bis IC11 müssen mit EPROM-Bausteinen 2716 bestückt sein, die entsprechend der folgenden Tabelle beschriftet sind:

| Sockel      | IC11 | IC10 | IC9  | IC8  |

|-------------|------|------|------|------|

| beschriftet | V1.8 | V1.8 | V1.8 | V1.8 |

| mit         | IV   | III  | II   |      |

- Die Lötpunkte P1-P2 und P7-P8 müssen gebrückt sein

- Die Baugruppen-Nummer O muß eingestellt sein

# Übungsteil 1

Tabelle zur Einstellung der Baugruppen-Nummern bzw. der Basis-Adressen der Speicher-Baugruppen.

Schalter offen∆H Schalter zu △L

| SA15 | SA14 | SA13 | Nummer<br>Baugruppen- | AdreNbereich (H)<br>von bis |

|------|------|------|-----------------------|-----------------------------|

| L    | L    | Ļ    | 0                     | 0000 - 1FFF                 |

| L    | L    | Н    | 1                     | 2000 - 3FFF                 |

| L    | Н    | L    | 2                     | 4000 - SFFF                 |

| L.   | Н    | Н    | 3                     | 6000 - 7FFF                 |

| Н    | Ļ    | L    | 4                     | 8000 - 9FFF                 |

| Н    | L    | Н    | 5                     | A000 - BFFF                 |

| Н    | Н    | L    | 6                     | C000 - DFFF                 |

| Н    | Н    | Н    | 7                     | E000 - FFFF                 |

Basis-Adressen

| Arbeitsblatt       | BFZ / MFA 10.3 20 |

|--------------------|-------------------|

| Speicher-Einheiten | Name:             |

| Übungsteil 1       | Datum:            |

Oberprüfen des Inhalts von RAM-Speicherzeilen

**A1**

Die dazu notwendigen Adreß- und Steuersignale liefert der Bus-Signalgeber. Adressen und Speicherinhalte werden auf der Bus-Signalanzeige angezeigt.

Stecken Sie Bus-Signalgeber, Bus-Signalanzeige und RAM-Baugruppe in den Baugruppenträger und schalten Sie die Betriebsspannung ein. Überprüfen Sie den Inhalt der ersten Speicherstellen im RAM, indem Sie nacheinander ab der Adresse 0000H einige Speicherstellen adressieren und das Steuersignal MEMR auslösen. Notieren Sie die Speicherinhalte und vergleichen Sie diese mit den Speicherinhalten, die Ihr Nachbar ermittelt hat. Die Inhalte sind zufällig und werden nicht übereinstimmen. Lesen Sie auch mehrmals eine gleiche Speicherstelle; der Inhalt darf sich nicht verändern.

| Adresse | Inhalt |

|---------|--------|

| 0000    | ·      |

| 0001    |        |

| 0002    |        |

| E000    |        |

| 0004    |        |

| 0005    |        |

| 0006    |        |

| 0007    |        |

| 0008    |        |

| 0009    |        |

| 0 0 0A  |        |

# Arbeitsblatt Speicher-Einheiten Obungsteil 1 BFZ / MFA 10.3. - 21 Name: Datum:

Eingabe eines kleinen Programms in den RAM-Speicher und Überprüfen des Speicher-Inhalts nach kurzzeitigem Abschalten der Betriebs-spannung.

**A**2

Übergeben Sie der RAM-Baugruppe ab der Speicheradresse 0000H die untenstehenden Daten. Sie laden damit ein Programm ins RAM, das in einer der späteren Übungen benötigt wird. Es veranlaßt den Prozessor fortwährend, den Signalzustand an den Eingangsleitungen einer Eingabe-Baugruppe zu lesen und ihn anschließend an einer Ausgabe-Baugruppe anzuzeigen.

| Adresse | flednl |

|---------|--------|

| 0000    | DB     |

| 0001    | 01     |

| 0002    | D3     |

| 0003    | 02     |

| 0004    | C3     |

| 0005    | 00     |

| 0006    | 00     |

Kontrollieren Sie die im RAM gespeicherten Daten anschließend durch Lesen der Speicherstellen.

Schalten Sie nun kurz die Betriebsspannung aus und ermitteln Sie die Daten der Speicherstellen 0000H bis 0006H. Vergleichen Sie diese mit den zuvor eingegebenen Daten.

| Adresse | Inhalt nach erneutem<br>Einschalten der Be-<br>triebsspannung | Erkenntnis: |  |

|---------|---------------------------------------------------------------|-------------|--|

| 0000    |                                                               |             |  |

| 0001    |                                                               |             |  |

| 0002    |                                                               |             |  |

| 0003    |                                                               |             |  |

| 0004    |                                                               |             |  |

| 0005    |                                                               |             |  |

| 0006    |                                                               |             |  |

| Arbeitsblatt       | BFZ / MFA 10.3 22 |  |  |  |

|--------------------|-------------------|--|--|--|

| Speicher-Einheiten | Name:             |  |  |  |

| Obungsteil 1       | Datum:            |  |  |  |

Lesen des Inhalts von ROM-Speicherzeilen bei verschiedenen Basisadressen der Baugruppe.

**A3**

Entfernen Sie nun die RAM-Baugruppe und stecken Sie an ihre Stelle die EPROM-Baugruppe. (Nicht beide Baugruppen wegen der gleichen Baugruppen-Nummer gemeinsam betreiben!)

Ermitteln Sie den Inhalt einiger Speicherstellen im ROM ab der Adresse 0000H und tragen Sie die Daten in untenstehende Tabelle ein. Lesen Sie die Speicherinhalte nach kurzzeitigem Abschalten der Betriebsspannung erneut. Vergleichen Sie die Daten mit den Tabellenwerten. Versuchen Sie durch einen Schreibvorgang den Inhalt einiger Speicherstellen zu überschreiben.

| Adresse      | inhalt | Inhalt nach erneutem Ein-<br>schalten der Betriebsspannung |

|--------------|--------|------------------------------------------------------------|

| 0000         |        |                                                            |

| 0001         |        |                                                            |

| 0002         |        |                                                            |

| 0004         |        |                                                            |

| Erkenntnis : |        |                                                            |

Stellen Sie nun die Baugruppen-Nummer 5 ein. Überprüfen Sie, ob die in obiger Aufgabe ermittelten Daten jetzt unter den Adressen des Blocks 5 (ab A000H) wiederzufinden sind. Kontrollieren Sie auch die Speicherstellen ab der Adresse 0000H.

| Adresse | Inhalt | Erkenntnis: |                                         |

|---------|--------|-------------|-----------------------------------------|

| A 0 0 0 |        |             | 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - |

| A 0 0 1 |        |             |                                         |

| A 002   |        |             |                                         |

| A 0 0 3 |        |             |                                         |

| A 004   |        |             |                                         |

# FACHTHEORETISCHE UBUNG MIKROCOMPUTER — TECHNIK

SPEICHER-EINHEITEN BFZ/MFA 10.3.

THEORIETEIL 2

# 2.1 Adreßdecodierung

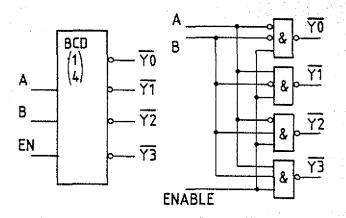

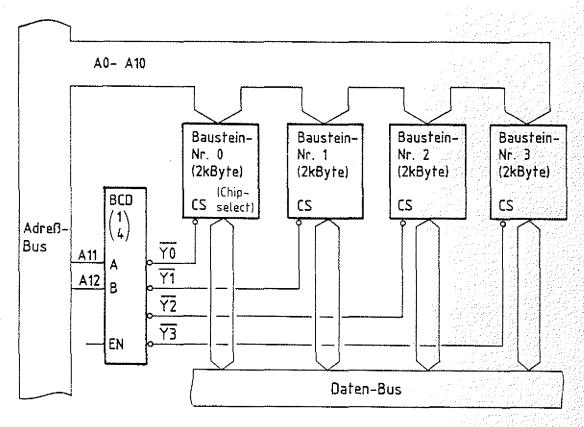

Ebenso wie man den Systemspeicher eines Computers aus mehreren Speicherblöcken aufbaut, wird ein einzelner Block meist aus mehreren kleineren Speicher-Bausteinen zusammengesetzt. Auf der 8-K-RAM/EPROM-Baugruppe BFZ/MFA 3.1. besteht der 8-KByte-Block aus vier 2-KByte-Speicher-Bausteinen. Der technische Aufbau eines solchen Blocks ergibt sich aus einer ähnlichen Überlegung, wie sie im Teil 1 ausgeführt wurde: Für einen 2-KByte-Speicher werden 11 Adreßleitungen für die Adressierung der 2048 Speicherstellen benötigt  $(2^{11} = 2^{1} \times 2^{10})$ 2x1024. Von den 13 Adreßleitungen, die der 8-KByte-Speicherbaugruppe zugeführt werden, bleiben zwei Leitungen übrig (A11 und A12). Aus den vier möglichen Signalzuständen auf diesen beiden Adreßleitungen lassen sich vier Freigabesignale für die vier 2-KByte-Bausteine ableiten. Dafür verwendet man wieder einen (Adreβ-)Decoder. Ein solcher Decoder ist mit seiner Innenschaltung in Bild 14 dargestellt.

8-K-Speicher-Block aufgebaut aus 4 2-K-Bausteinen

| Eingänge |                        |   | Α         | US       | gäng      | je        |  |  |

|----------|------------------------|---|-----------|----------|-----------|-----------|--|--|

| EN       | В                      | Α | <u>Y0</u> | Ϋ́1      | <u>72</u> | <u>73</u> |  |  |

|          | L                      | L |           | Ξ        | H         | :Ha       |  |  |

| Н        | L                      | Н | H         | L        | Н         | Н         |  |  |

|          | Н                      | L | Н         | Н        | L         | Н         |  |  |

|          | H                      | Н | Н         | Н        | Н         | L         |  |  |

| L        | X                      | X | alle      | <u>.</u> |           |           |  |  |

|          | X= beliebig (H oder L) |   |           |          |           |           |  |  |

Bild 14: Schaltung und Funktionstabelle eines 1 aus 4- Decoders

Entsprechend dem Signalzustand an den Eingängen A und B wird immer ein Ausgang auf L-Signal (Aktiv Low-Signal) geschaltet. Über einen Freigabe-Eingang (ENABLE) können außerdem alle Ausgänge gesperrt werden. Dieser Decoder wird 1-aus 4-Decoder genannt, weil einer von vier möglichen Zuständen an den Ausgängen angezeigt wird.

1 aus 4-Decoder

Entsprechend gibt es auch 1 aus 8- und 1 aus 16-Decoder. Die Schaltung eines 8-KByte-Blocks unter Verwendung eines Adreßdecoders ist in Bild 15 dargestellt.

Bild 15: 8-KByte-Speicherblock aufgebaut mit vier 2-KByte-Speicher-Bausteinen

Die Adreßleitungen AO bis A10 werden an alle Speicher-Bausteine angeschlossen. Über den Signalzustand auf diesen Leitungen wird in den Bausteinen eine ganz bestimmte Speicherstelle ausgewählt. Welcher Baustein schließlich Daten senden oder empfangen darf, wird vom Signalzustand auf den Adreßleitungen A11 und A12 bestimmt. Die Freigabesignale, die dazu vom Adreßdecoder geliefert werden, sind mit den sogenannten "Chip-Select-Eingängen" (chip-select = Bausteinauswahl) der Speicher-Bausteine verbunden. Diese Eingänge sind speziell für die hier geschilderte Anwendung vorgesehen. In der Tabelle Bild 16 sind die Adreßbereiche angegeben, die von den vier Bausteinen überdeckt werden. Hier wurde von der Baugruppe 0 bzw. der Basis-Adresse 0000 ausgegangen. Unberücksichtigt bleiben in dieser Tabelle

Chip-Select (CS)

die Adreßleitungen A13 bis A15, über die die Baugruppen-Nummer bzw. die Basis-Adresse festgelegt wird.

|    |    | ··· | Ad | reßle | itung |            |    |   |   |   |     | ·  | Adresse | Baustein |

|----|----|-----|----|-------|-------|------------|----|---|---|---|-----|----|---------|----------|

| 12 | 11 | 10  | 9  | 8     | 7     | 6          | 5  | 4 | 3 | 2 | . 1 | 0  |         |          |

| L  | L  | L   | L  | L     | Ļ     | , L        | Ĺ  | L | L | Ļ | L   | L. | 0000    |          |

| L  | L  | Н   | Н  | H     | Н     | :<br>H     | Н  | Н | Н | Н | Н   | Н  | 07FF    |          |

| L  | Н  | L   | L  | L     | L     | . L        | L. | Ļ | L | L | L   | L  | 0800    |          |

| L  | н  | н   | Н  | Н     | Н     | :<br>H     | Н  | Н | н | н | . н | Н  | OFFF    |          |

| Н  | L  | L   | L. | L     | L     | <u>.</u> L | L  | L | L | L | L.  | Ļ  | 1000    |          |

| Н  | Ļ  | н   | Н  | Н     | Н     | :<br>H     | Н  | Н | Н | н | Н   | ŧΗ | 17FF    | 2        |

| Н  | Н  | L   | L  | L     | L     | . L        | L  | L | L | L | Ļ   | L  | 1800    |          |

| Н  | Н  | н   | Н  | H     | н     | :<br>H     | Н  | Н | Н | Н | Н   | ЭН | 1FFF    | 3        |

Bild 16: Baustein-Adreßbereiche der vier Speicher-Bausteine der 8-KByte-Speicherbaugruppe

Das Anschlußbild eines 2-KByte-Speicher-Bausteins ist in Bild 17 dargestellt. Es handelt sich dabei um einen RAM-Baustein. RAM- und ROM-Bausteine unterscheiden sich nur durch die Write Enable-Leitung (Write Enable = Schreiben ermöglichen), die beim ROM-Speicher fehlt. Mit einem L-Signal auf dieser Leitung wird ein Datenwort in den Speicher geschrieben. Da die Speicher-Bausteine - ebenso wie die Eingabe-Baugruppen - Daten auf den Daten-Bus schalten, werden ihre Datenleitungen über Tristate-Gatter hinausgeführt. Der Chip-Select-Eingang ist bei diesen Bausteinen intern direkt mit dem ENABLE-Eingang der Tristate-Gatter verbunden.

Bild 17: Anschlußbild eines 2-KByte-Speicher-Bausteins

Write-Enable-Leitung

# 2.2 Vereinfachte Schaltung einer Speicher-Baugruppe

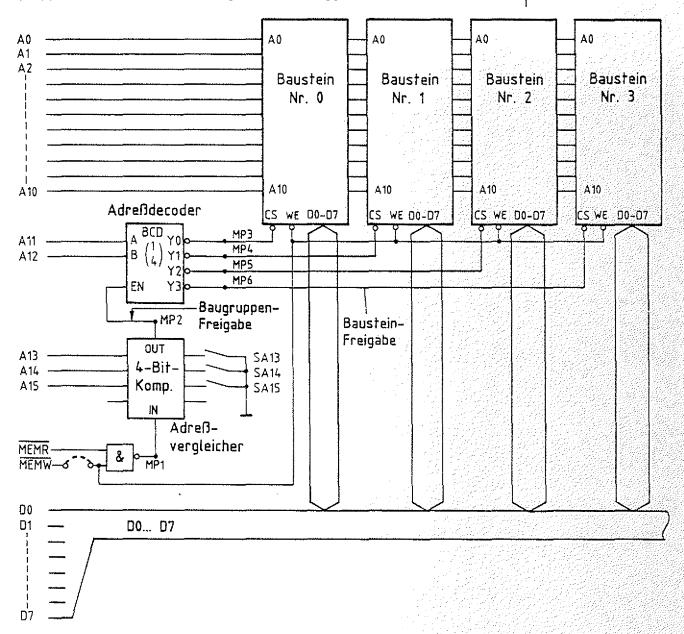

Die Schaltung der Speicher-Baugruppe ist in Bild 18 abgebildet. Zur Verbesserung der Übersichtlichkeit sind die Daten-Bus-Leitungen vereinfacht dargestellt und einige auf der Baugruppe vorhandene Schaltungsdetails weggelassen worden.

Bild 18: Vereinfachtes Schaltbild der Speicherbaugruppe

Der Adreßvergleicher zur Erkennung der Baugruppen-Nummer bzw. der Basis-Adresse auf den Adreßleitungen A13 bis A15 entspricht dem Adreßvergleicher auf den Ein- und Ausgabe-Baugruppen. Allerdings reicht hier ein 4-Bit-Komparator aus. Der Kaskadiereingang "IN" des Komparators erhält immer dann

9

H-Signal, wenn entweder MEMR oder MEMW L-Signal führen, d.h. der Prozessor den Speicher aktiviert. Der Ausgang des Adreßvergleichers (OUT) ist mit dem Freigabe-Eingang (ENABLE) des Adreßdecoders verbunden.

Ein Speicher-Baustein wird nur dann freigegeben, wenn

- die Baugruppe über A13 bis A15 ausgewählt wird,

- das Steuersignal MEMR oder MEMW aktiviert wird und

- die entsprechende Baustein-Nummer an den Adreβ-Leitungen A11 und A12 ansteht.

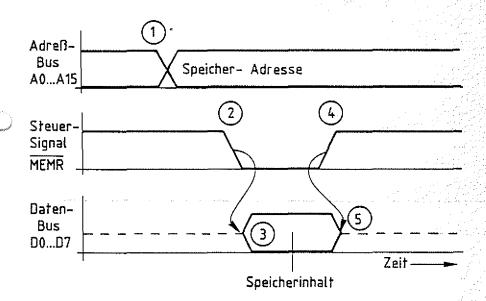

Handelt es sich um eine RAM-Baugruppe, so wird bei einem Schreibvorgang die WE-Leitung an den Bausteinen auf L-Signal geschaltet. Bei einer ROM-Baugruppe wird das Steuersignal MEMW durch eine Brücke von der Baugruppe getrennt. Die Signal- Zeit-Diagramme für einen Lese- und einen Schreibvorgang durch den Prozessor sind in den Bildern 19 und 20 dargestellt.

Bild 19: Lesen einer Speicherzeile

#### Lesevorgang:

Zum Zeitpunkt 1 sendet der Prozessor die Speicheradresse auf den Adreßleitungen AO bis A15 aus. Zum Zeitpunkt 2 veranlaßt der Prozessor den Speicher, den Inhalt der adressierten Speicherzeile auf den Daten-Bus zu schalten (ZeitBedingungen für Schreiben oder Lesen

Zeitdiagramm Lesevorgang

punkt 3). Mit dem L-H-Signalwechsel auf der Steuerleitung MEMR übernimmt der Prozessor den Signalzustand vom Daten-Bus und beendet gleichzeitig den Lesevorgang, so daß der Speicher die Daten vom Bus wegschaltet (Zeitpunkt 5). Der Vorgang ist identisch mit dem Lesevorgang einer Eingabe-Baugruppe.

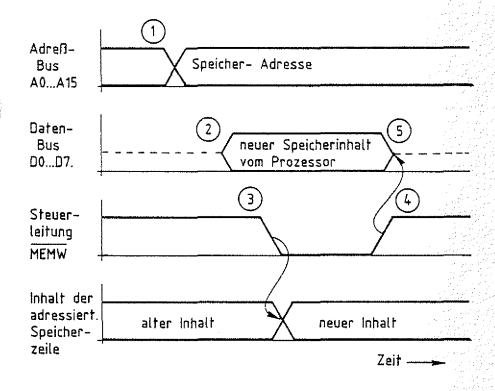

Bild 20: Schreiben in eine Speicherzeile

#### Schreibvorgang:

Zum Zeitpunkt 1 sendet der Prozessor die Speicheradresse auf den Adreßleitungen AO bis A15 aus. Zum Zeitpunkt 2 stellt er den neuen Speicherinhalt am Daten-Bus bereit. Mit dem Steuersignal MEMW (Zeitpunkt 3) löst er die Datenübernahme in die adressierte Speicherzeile aus. Der Schreibvorgang wird mit H-Signal auf der Steuerleitung MEMW beendet (Zeitpunkt 4), so daß der Prozessor gleichzeitig die Daten vom Bus wegschalten kann (Zeitpunkt 5). Auch dieser Ablauf ist identisch mit einer Datenübergabe an eine Ausgabe-Baugruppe.

Zeitdiagramm Schreibvorgang

# FACHTHEORETISCHE ÜBUNG MIKROCOMPUTER — TECHNIK

SPEICHER-EINHEITEN

BFZ/MFA 10. 3.

ÜBUNGSTEIL 2

# Übungsteil 2

In den folgenden Arbeitsschritten werden Sie auf der Speicher-Baugruppe die Signale für...

- die Freigabe der Baugruppe und

- die Auswahl der Speicher-Bausteine (CS)

meßtechnisch überprüfen.

# Dazu benötigen Sie:

- 1 Baugruppenträger mit Busverdrahtung (BFZ/MFA 0.1.)

- 1 Bus-Abschluß (BFZ/MFA 0.2.)

- 1 Trafo-Einschub (BFZ/MFA 1.1.)

- 1 Spannungsregelung (BFZ/MFA 1.2.)

- 1 Bus-Signalgeber (BFZ/MFA 5.1.)

- 1 Bus-Signalanzeige (BFZ/MFA 5.2.)

- 1 8-K-RAM/EPROM bestückt mit RAM (BFZ/MFA 3.1.)

- 1 Adapter 64polig (BFZ/MFA 5.3.)

- 1 Logiktester oder Vielfachmeßinstrument

- 2 Meßleitungen

Allgemeine Hinweise zur Durchführung der Übungen:

- Die Einschübe dürfen nur bei abgeschalteter Betriebsspannung gesteckt oder gezogen werden

- Aufgrund der Busverdrahtung können die Baugruppen in beliebige Steckplätze gesteckt werden

- Den logischen Signalen "0" und "1" sind die folgenden Pegel zugeordnet:

- Alle zur Messung an den Baugruppen vorgegebenen Arbeitsblätter enthalten:

- = Angaben über den Sinn der jeweiligen Messung

- = Angaben über einzustellende Bedingungen (z.B. Schalterstellungen)

- = Aufgabenstellungen, ggf. mit Hinweisen zu möglichen Fehlern.

zusammengebaut und geprüft nach FPÜ BFZ/MFA 1.2. Arbeitsblatt A7

# Übungsteil 2

# Bedienungshinweise:

8-K-RAM/EPROM-Baugruppe als RAM-Baugruppe:

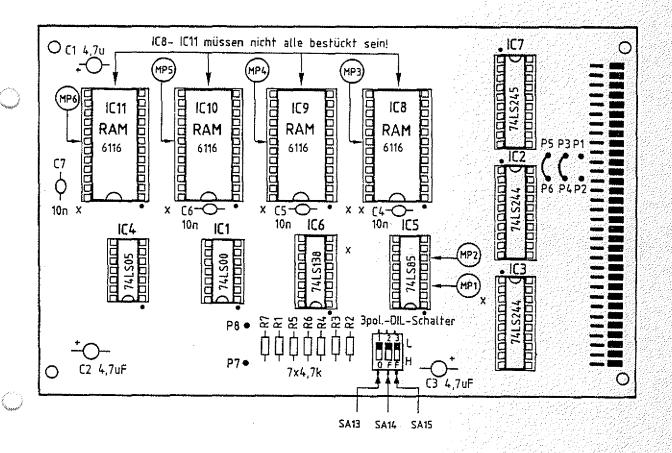

Im unten abgebildeten Bestückungsplan der RAM-Baugruppe sind die in Bild 17 (vereinf. Schaltbild) eingetragenen Meßpunkte MP1 bis MP6 gekennzeichnet. Benutzen Sie dieses Schaltbild auch während der Messungen.

MP1 — Verknüpfung der Steuersignale MEMR u. MEMW MP2 — Baugruppen- Freigabe MP3 — Bausteinfreigabe Nr.0 (CS0) MP4 — " Nr1 (CS1) MP5 — " Nr2 (CS2)

Nr3: (CS3)

MP6

| Arbeitsblatt       | BFZ / MFA 10.3 31 |  |  |  |

|--------------------|-------------------|--|--|--|

| Speicher-Einheiten | Name:             |  |  |  |

| Übungsteil 2       | Datum:            |  |  |  |

Prüfen der Wirkung der Steuersignale am Eingang des Adreß-Vergleichers (MP1) A1

Stellen Sie mit SA13 - SA15 die Baugruppen-Nummer O ein (Basis-Adresse 0000H). Stecken Sie die Speicher-Baugruppe über die Adapter-Karte neben den Bus-Signalgeber und die Bus-Signalanzeige in den Baugruppenträger ein. Schalten Sie die Betriebsspannung ein.

Überprüfen Sie mit einem Logiktester oder Meßgerät die Wirkung der Steuersignale MEMR und MEMW am Eingang des Adreßvergleichers (MP1), indem Sie während der Messung die Steuersignale (Bus-Signalgeber) abwechselnd betätigen (nicht gleichzeitig).

| Steuersignaltaste |                | Pegel am MP1 |

|-------------------|----------------|--------------|

| MEMR              | nicht betätigt |              |

|                   | betätigt       |              |

| MEMW              | nicht betätigt |              |

|                   | betätigt       |              |

| Αr | he  | it | sh | la | t t |

|----|-----|----|----|----|-----|

| ~1 | H C |    | 30 | ισ | 1 1 |

BFZ / MFA 10.3. - 32

Speicher-Einheiten

Name:

Übungsteil 2

Datum:

Prüfen des Freigabesignals für die Speicher-Baugruppe (MP2)

A2.1

Prüfen Sie das Freigabesignal für die Speicher-Baugruppe am Meßpunkt MP2, wenn Sie nacheinander am Bus-Signalgeber Adressen einstellen, die <u>im</u> und <u>außerhalb</u> des Adreßbereiches der Baugruppe liegen. Tragen Sie den Signalzustand in die Tabelle ein.

| Schalter       | Baugruppen-<br>Nummer | Adrefibereich | Pegel am<br>Meßpunkt           |  |

|----------------|-----------------------|---------------|--------------------------------|--|

| SA15 SA14 SA13 |                       | von bis       | MP2                            |  |

| <u> </u>       | QQ                    | 0000 — 1FFF   |                                |  |

|                | 1                     | 2000 — 3FFF   |                                |  |

|                | 2                     | 4000 5FFF     |                                |  |

| 1              | 3                     | 6000 — 7FFF   | zi giye ve yaşılığı kaşılıyını |  |

|                | 4                     | 8000 - 9FFF   | daradar#inibada                |  |

|                | 5                     | A000 - BFFF   |                                |  |

|                | 6                     | COOO DFFF     | 1940×15000000000000            |  |

|                | 7                     | E000 - FFFF   |                                |  |

| Arbeitsblatt       | BFZ / MFA 10.3 33 |

|--------------------|-------------------|

| Speicher-Einheiten | Name:             |

| Übungsteil 2       | Datum:            |

Stellen Sie mit den Schaltern SA13 bis SA15 die Baugruppen-Nummer 5 ein und wiederholen Sie die vorangegangenen Messungen. A2.2

|      | Schalter |       | Baugruppen-<br>Nummer | Adreßbereich Pegel am<br>Meßpunkt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|----------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SA15 | SA14     | SA13  |                       | von bis MP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |          |       | 0                     | 0000 — 1FFF 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |          |       | 1                     | 2000 — 3FFF 2 1 00.2200/p/200/200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |          |       | 2                     | 4000 - SFFF (1.1.) 18.00486/19/09/20/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |          |       | . 3                   | 6000 - 7FFF - 2 0.5-505-5465-2805                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |          | ····· | 4                     | 8000 - 9FFF : 1 1 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| H    | L        | H     | 5                     | A000 - BFFF And I have a second and a second a second and |

|      |          |       | 6                     | COOO - DFFF and supplementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |          |       | 7                     | E000 - FFFF to a second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Arbeitsblatt                            | BFZ / MFA 10.3 34            |

|-----------------------------------------|------------------------------|

| Speicher-Einheiten                      | Name:                        |

| Übungsteil 2                            | Datum:                       |

| Prüfen der Baustein-Freigabe-Signale an | den CS-Eingängen $\Lambda$ 3 |

der Speicher-Bausteine

Stellen Sie die Baugruppen-Nummer auf 0.

Stellen Sie nacheinander die unten aufgeführten Adressen mit dem Bus-Signalgeber ein und überprüfen Sie bei jeder Einstellung die vier Baustein-Freigabesignale (Chip Select) an den Meßpunkten MP3 bis MP6.

| Baustein- | Einzustellende                                         | Baustein-Freigabesignale |              |              |              |  |  |

|-----------|--------------------------------------------------------|--------------------------|--------------|--------------|--------------|--|--|

| Nummer    | Adressen<br>(Anfangs-und End-<br>Adr. jedes Bausteins) | (MP3<br>(CS0)            | MP4<br>(CS1) | MP5<br>(CS2) | MP6<br>(CS3) |  |  |

| 0         | 0000, 07FF                                             |                          |              |              |              |  |  |

| 1         | 0800, 0FFF                                             | -                        | <u> </u>     |              |              |  |  |

| 2         | 1000, 17FF                                             |                          |              |              |              |  |  |

| 3         | 1800, 1FFF                                             |                          |              |              | 4.73.9       |  |  |